Works with 96MB at half-speed. Still not quite enough bandwidth, but its not nearly as glitchy as 4 bit halfspeed.

96MB board can thus play big games. Slight problem: I can't get any PROGBK2 games (well, tried mslug 4 and matrimelee) to boot at all. Gotta be some issue with how the bankswitching works on them.

Tried The Last Blade though, that works great (though it's only ~61 MB and being a fight game, obviously doesn't have big CPU usage to slow down).

You could potentially try sysclk/3 if you can sort out generating the asymmetric clock on the CLK pins. Would give a speed boost of 50% 33%. Streamer can do divide by 3 and you would remain below the rated speed of the PSRAM but the data sheet mentions it should be from 45-55% duty cycle so IDK if it would work or not.

@Rayman said:

@Wuerfel_21 I tried this on 96 MB board with 64 MB installed. Loads the roms and then gives blank screen.

Does it need all the chips for some reason?

What game did you try? (I've added mslug4 and matrimelee to gamedb, but as stated, brogbk2 is busted) The available chips need to obviously be consecutive (i.e. CS 10,11,12,13)

@rogloh not having any luck with your test program...

This is with the 96 MB board (only 64 MB installed) on base pin #0

Does this look right? Or, do you see what I'm doing wrong?

D:\Propeller2\P2Eval_PSRAM\Rogloh\psram8>c:/flexprop/bin/loadp2 -t psram8_delay_test.binary

( Entering terminal mode. Press Ctrl-] or Ctrl-Z to exit. )

PSRAM 8 bit memory read delay test over frequency, ESC exits

Enter the base pin number for your PSRAM (0,8,16...48) [40]: 0

Enter the chip enable pin number for your PSRAM [57]: 10

Enter the clock pin number for your PSRAM [56]: 72

Enter an additional CE/CLK P2 pin to drive high (0-55), or a higher value to exit [56]: 11

Enter an additional CE/CLK P2 pin to drive high (0-55), or a higher value to exit [56]: 56

Enter a starting frequency to test in MHz (100-350) : [100] 250

Enter the ending frequency to test in MHz (250-350) : [250] 260

Enter 1 to use the automatic delay value only, or 0 to test over the delay range : [0] 1

Enter 1 to display the first error encountered, or 0 to not display error details : [0] 0

Testing P2 from 250000000 - 260000000 Hz

Successful data reads from 100 block transfers of 8192 random bytes

Frequency Delay 3 4 5 6 7 8 9 10 11 12 13 14

250000000 (10) 0%

251000000 (10) 0%

252000000 (10) 0%

253000000 (10) 0%

254000000 (10) 0%

255000000 (10) 0%

256000000 (10) 0%

257000000 (10) 0%

258000000 (10) 0%

259000000 (10) 0%

260000000 (10) 0%

Enter the base pin number for your PSRAM (0,8,16...48) [0]:

Wasn't having any luck, so added two more chips.

Now it works! Well, sort of...

Last Blade seem to load and play, but some of the graphics are missing.

First see this in the game menu. I think there's supposed to be something showing your selection, but seems to be missing.

Then, when battle starts, the opponent is mostly invisible.

@Wuerfel_21 Great news with the 84 MB game. Do you think it's all actually working?

Maybe we're OK with the 96 MB board as is?

@Rayman said:

Wasn't having any luck, so added two more chips.

Now it works! Well, sort of...

Last Blade seem to load and play, but some of the graphics are missing.

First see this in the game menu. I think there's supposed to be something showing your selection, but seems to be missing.

Then, when battle starts, the opponent is mostly invisible.

Sounds like one of the chips is reading zeroes. As said, you sure there are chips on pins 10,11,12,13 (or another consecutive range of 4 pins with adjusted config)?

@Wuerfel_21 Great news with the 84 MB game. Do you think it's all actually working?

Seems to. KOF2000 also works, but has corrupted fix layer (I think it's supposed to have some sort of bankswitching, which I can't emulate, anyways)

Maybe we're OK with the 96 MB board as is?

Not really. Can't actually sustain full graphics load (play twinsprites to see this in effect) and slows down quite heavily when there's actual CPU load (also play twinsprites to see this in effect).

Also, as said, try messing with PSRAM_DELAY and PSRAM_SYNC_DATA. For me delay settings 1 and 2 work. So I guess DELAY=2, SYNC_DATA=true might be the ideal setting?

@Rayman said:

@rogloh not having any luck with your test program...

This is with the 96 MB board (only 64 MB installed) on base pin #0

Does this look right? Or, do you see what I'm doing wrong?

Wuerfel_21 was correct, you need to not use the automatic delay only, but test over the full range of delays when it asks that.

Also you may want to drive more of your floating chip enable pins high if you have more than one bank fitted. In your case you mentioned 64MB fitted, that would be 8 chips and this is 3 extra chip enables that need to be driven high on your board. It looked like what you posted only drove one more chip enable high (pin 11). There is a risk if the other devices chip enables floated low that it would clash with the selected device during the test when it reads back the data and this is not good.

@Rayman said:

Maybe we're OK with the 96 MB board as is?

Not really. Can't actually sustain full graphics load (play twinsprites to see this in effect) and slows down quite heavily when there's actual CPU load (also play twinsprites to see this in effect).

We probably have a few options for improving this....

migrate to boards that are 16 bit wide and consume 3 accessory header groups...there's a chance that 3 parallel chips would work okay at sysclk/2, based on the 24MB board results IIRC, if the layout is tight enough. This is the least risky option IMO.

try the sysclk/3 option on the 96MB board, not holding my breath but could be worth a shot if it saves HW respin work

get an 8 bit board to run at sysclk/2 with multiple chips, but this one is tough. If you want 6 paralleled devices for 96MB it seems like it's probably too much load even with good board designs, but it's a real unknown. Maybe 4 paralleled loads is achievable for 64MB on a good layout...?

How would sys/3 even work? Pulse train mode i guess?

Yeah it's not transition mode. Its a 1:2:1:2:1:2 clock pulse sequence. You would also get to place the position of the clock with respect to the data (ie. device may work better with 2:1:2:1 vs 1:2:1:2, for example, either more setup time or more hold time). Maybe the address setup phase should keep using sysclk/4 too and you switch the clock rate after that...dunno.

@Rayman said:

@Wuerfel_21 would you say Metal Slug is 100% working with 96 MB board in 8 bit mode? Or, at least working as well as it does with 32 MB edge board?

Haven't played that quite enough. Metal Slug 2 I did and I'd say it's okay-ish. Lots of slowdown, but MS2 kinda just has that, even on real HW / accurate emulator.

I did play some Twinkle Star Sprites and the graphics system breaking down due to lack of bandwidth is kinda obvious in that one. Also slowdown.

All the pünch and stäb kinda games do work perfectly fine, they don't really stretch the hardware too thin.

How would sys/3 even work? Pulse train mode i guess?

Yeah it's not transition mode. Its a 1:2:1:2:1:2 clock pulse sequence. You would also get to place the position of the clock with respect to the data (ie. device may work better with 2:1:2:1 vs 1:2:1:2, for example, either more setup time or more hold time). Maybe the address setup phase should keep using sysclk/4 too and you switch the clock rate after that...dunno.

Are all main memory array data access totally restricted to only happen within the initially-specified (addressed) row, or does some of the existing drivers makes use of any row boundary crossing scheme?

@Yanomani said:

Are all main memory array data access totally restricted to only happen within the initially-specified (addressed) row, or does some of the existing drivers makes use of any row boundary crossing scheme?

Bursts in my driver get fragmented to not go over the page boundary, while Wuerfel_21's reads are small blocks that are also 2^n aligned and won't cross the page.

Note: for an 8 bit driver the page boundary is effectively 2kB sized (4bit = 1kB, 16bit = 4kB).

Comments

New driver seems to work from coldboot, all good.

Works with 96MB at half-speed. Still not quite enough bandwidth, but its not nearly as glitchy as 4 bit halfspeed.

96MB board can thus play big games. Slight problem: I can't get any PROGBK2 games (well, tried mslug 4 and matrimelee) to boot at all. Gotta be some issue with how the bankswitching works on them.

Tried The Last Blade though, that works great (though it's only ~61 MB and being a fight game, obviously doesn't have big CPU usage to slow down).

Some working code attached.

Cool, glad something is finally working now.

You could potentially try sysclk/3 if you can sort out generating the asymmetric clock on the CLK pins. Would give a speed boost of 50% 33%. Streamer can do divide by 3 and you would remain below the rated speed of the PSRAM but the data sheet mentions it should be from 45-55% duty cycle so IDK if it would work or not.

@Wuerfel_21 I tried this on 96 MB board with 64 MB installed. Loads the roms and then gives blank screen.

Does it need all the chips for some reason?

What game did you try? (I've added mslug4 and matrimelee to gamedb, but as stated, brogbk2 is busted) The available chips need to obviously be consecutive (i.e. CS 10,11,12,13)

Could also just be that I bungled the upload.

Was trying lastblad ...

@rogloh not having any luck with your test program...

This is with the 96 MB board (only 64 MB installed) on base pin #0

Does this look right? Or, do you see what I'm doing wrong?

D:\Propeller2\P2Eval_PSRAM\Rogloh\psram8>c:/flexprop/bin/loadp2 -t psram8_delay_test.binary ( Entering terminal mode. Press Ctrl-] or Ctrl-Z to exit. ) PSRAM 8 bit memory read delay test over frequency, ESC exits Enter the base pin number for your PSRAM (0,8,16...48) [40]: 0 Enter the chip enable pin number for your PSRAM [57]: 10 Enter the clock pin number for your PSRAM [56]: 72 Enter an additional CE/CLK P2 pin to drive high (0-55), or a higher value to exit [56]: 11 Enter an additional CE/CLK P2 pin to drive high (0-55), or a higher value to exit [56]: 56 Enter a starting frequency to test in MHz (100-350) : [100] 250 Enter the ending frequency to test in MHz (250-350) : [250] 260 Enter 1 to use the automatic delay value only, or 0 to test over the delay range : [0] 1 Enter 1 to display the first error encountered, or 0 to not display error details : [0] 0 Testing P2 from 250000000 - 260000000 Hz Successful data reads from 100 block transfers of 8192 random bytes Frequency Delay 3 4 5 6 7 8 9 10 11 12 13 14 250000000 (10) 0% 251000000 (10) 0% 252000000 (10) 0% 253000000 (10) 0% 254000000 (10) 0% 255000000 (10) 0% 256000000 (10) 0% 257000000 (10) 0% 258000000 (10) 0% 259000000 (10) 0% 260000000 (10) 0% Enter the base pin number for your PSRAM (0,8,16...48) [0]:That should totally work. The chips you have are on CS 10,11,12,13, right? If yes, play with PSRAM_DELAY and PSRAM_SYNC_DATA.

You need to answer 0 at the second to last question.

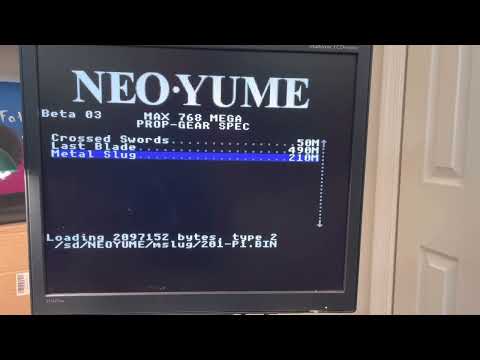

I present to you, the largest (~84 MB) game that I can get to run without issues. Yep, that's the actual loading time.

Updated gamedb attached, but good luck getting all the right ROMs.

Wasn't having any luck, so added two more chips.

Now it works! Well, sort of...

Last Blade seem to load and play, but some of the graphics are missing.

First see this in the game menu. I think there's supposed to be something showing your selection, but seems to be missing.

Then, when battle starts, the opponent is mostly invisible.

@Wuerfel_21 Great news with the 84 MB game. Do you think it's all actually working?

Maybe we're OK with the 96 MB board as is?

Just tried Metal Slug... Loads ROMS then gets just black screen.

Could be ROMS or memory problem, I suppose....

Sounds like one of the chips is reading zeroes. As said, you sure there are chips on pins 10,11,12,13 (or another consecutive range of 4 pins with adjusted config)?

Seems to. KOF2000 also works, but has corrupted fix layer (I think it's supposed to have some sort of bankswitching, which I can't emulate, anyways)

Not really. Can't actually sustain full graphics load (play twinsprites to see this in effect) and slows down quite heavily when there's actual CPU load (also play twinsprites to see this in effect).

@Wuerfel_21 Ooops, but the new chips in the wrong place...

Metal Slug 1? That'd mean bank 1 (CS on pin 11) is bad.

Ok, with 96 MB board fully populated, Last Blade seems to be working correctly.

Metal slug runs now, but showing heavily garbled graphics, starting with Neo-Geo logo...

That sounds strange. Can I get video of that?

Also, as said, try messing with PSRAM_DELAY and PSRAM_SYNC_DATA. For me delay settings 1 and 2 work. So I guess DELAY=2, SYNC_DATA=true might be the ideal setting?

Here it is...

maybe roms are wrong... Had to rename all file extensions from .rom to .bin...

Does it work with the 8-bit driver for you?

Okay, that's interesting, correct graphics but in the wrong place. Seems like bung romset. Try getting a different one.

(yes, it does work for me)

Ok, looks like had the wrong roms... Download a different set (this time with correct extension) and it does seem to work!

Wuerfel_21 was correct, you need to not use the automatic delay only, but test over the full range of delays when it asks that.

Also you may want to drive more of your floating chip enable pins high if you have more than one bank fitted. In your case you mentioned 64MB fitted, that would be 8 chips and this is 3 extra chip enables that need to be driven high on your board. It looked like what you posted only drove one more chip enable high (pin 11). There is a risk if the other devices chip enables floated low that it would clash with the selected device during the test when it reads back the data and this is not good.

We probably have a few options for improving this....

That is REALLY amazing! Just… WOW! Has Chip/Ken seen this?

If you mean the emulator - yes.

The huge memory board - don't think so.

@rogloh

How would sys/3 even work? Pulse train mode i guess?

Yeah it's not transition mode. Its a 1:2:1:2:1:2 clock pulse sequence. You would also get to place the position of the clock with respect to the data (ie. device may work better with 2:1:2:1 vs 1:2:1:2, for example, either more setup time or more hold time). Maybe the address setup phase should keep using sysclk/4 too and you switch the clock rate after that...dunno.

@Wuerfel_21 would you say Metal Slug is 100% working with 96 MB board in 8 bit mode? Or, at least working as well as it does with 32 MB edge board?

Haven't played that quite enough. Metal Slug 2 I did and I'd say it's okay-ish. Lots of slowdown, but MS2 kinda just has that, even on real HW / accurate emulator.

I did play some Twinkle Star Sprites and the graphics system breaking down due to lack of bandwidth is kinda obvious in that one. Also slowdown.

All the pünch and stäb kinda games do work perfectly fine, they don't really stretch the hardware too thin.

Are all main memory array data access totally restricted to only happen within the initially-specified (addressed) row, or does some of the existing drivers makes use of any row boundary crossing scheme?

Bursts in my driver get fragmented to not go over the page boundary, while Wuerfel_21's reads are small blocks that are also 2^n aligned and won't cross the page.

Note: for an 8 bit driver the page boundary is effectively 2kB sized (4bit = 1kB, 16bit = 4kB).