Maybe use the Parallax TTF font. The one that installs with Propeller Tool. All the tables and code snippets in the P1 manual use it.

Slightly offtopic:

The best monospace font I've used is probably Consolas. You know, the default one that comes with Windows. Depressingly boring, yet somehow looks better than everything else I've tried, especially at low resolution.

I prefer the robo fonts (ie 3 posts back)

It's a document so it doesn't need to be the parallax font, which BTW, a number of people seem to have difficulty installing. Shame because I love to include diagrams using it with the source code

I’ve never had a problem but others keep reporting problems every now and then. Not sure if it’s gone away.

Then there’s issues with different compilers not recognising the extended characters in the source. I had this problem just a few days ago - may have been with pnut but can’t be sure.

Colored Smart-Pin block diagrams in this discussion include left-side labels:

"Physical Even# Pin" (Even Pin, pins 0, 2, 4,...62), and

"Physical Odd# Pin" (Odd Pin, pins 1, 3, 5,..63).

This seems to indicate that the odd-numbered I/O pins, such as P1, P3, and so on, that I connect devices to have only those functions in the lower section of the diagram. Is that correct? Likewise for the even-numbered pins.

I thought each Smart Pin had the complete functionality shown in the entire block diagram. The diagram, however, indicates differences in the circuits that connect to even pins and to odd pins.

Mainly it's about the interconnect for supporting differential output using Other and input with PinA and PinB.

And, yes, the USB smarts happens to be managed from the even Smartpin also. USB needs a differential pair so it was easiest to do it that way I presume.

@Rayman & @evanh Do you mind if I take your diagrams as inspiration for another experiment? If it works out, I'll give attribution, of course.

I'm considering an attempt to make the smartpin routing and configuration something much more dynamic that someone can play with on a web page.

Sure thing, go for it. Sounds a little like one of those logic simulators.

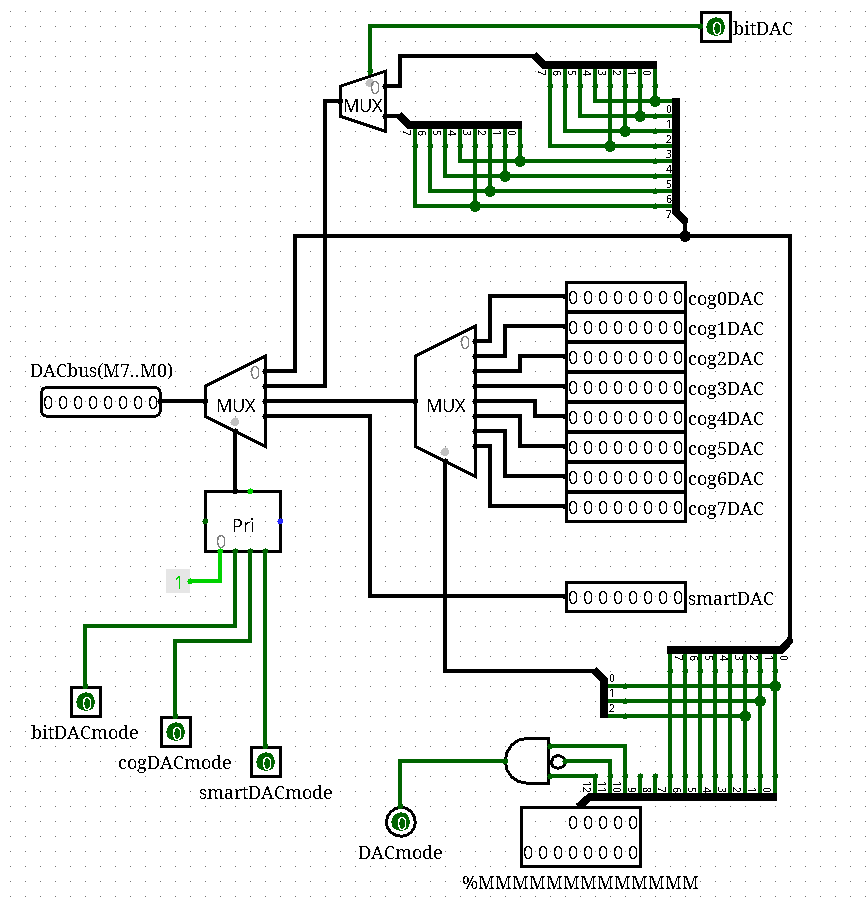

EDIT: Hehe, the schematic like diagrams that I did were done with Logisim. They were done as documentation but it also allowed me to verify the function by twiddling the inputs.

I'm thinking of taking the block diagram and pin descriptions as the base layer and adding a configuration selector for each set of pins.

The idea is to visually illustrate the active routings and component level configuration to make it visually obvious.

I have a concept in mind for how to do it, but the tools to implement cleanly and without extra complication it are still being sought. Early experiments show promise but I'm still skirmishing with tooling.

Ideally it should be easy to throw onto a static hosting site like gh pages where we can all use it. First things first, though.

Bob, sure thing.

Rayman, maybe give also change DAC label on the green line to DACbus or DACBUS or DAC_Bus. Whichever you like most. Just to make it clearer the line is the 8-bit data lines and not the analogue.

I've just updated the T-block functional schematic too. Corrected the logic for OUT override with smartpin configured. And also now uses %SSSSS labelling for smartpin mode field instead of the older %MMMMM.

Comments

How's this (Note: Fixed sub table fonts after posting and reposted):

Also, I'm not sure how I got two different Ohm symbols in there...

Slightly offtopic:

The best monospace font I've used is probably Consolas. You know, the default one that comes with Windows. Depressingly boring, yet somehow looks better than everything else I've tried, especially at low resolution.

It's a document so it doesn't need to be the parallax font, which BTW, a number of people seem to have difficulty installing. Shame because I love to include diagrams using it with the source code

PS: Here's the one I have installed

Then there’s issues with different compilers not recognising the extended characters in the source. I had this problem just a few days ago - may have been with pnut but can’t be sure.

"Physical Even# Pin" (Even Pin, pins 0, 2, 4,...62), and

"Physical Odd# Pin" (Odd Pin, pins 1, 3, 5,..63).

This seems to indicate that the odd-numbered I/O pins, such as P1, P3, and so on, that I connect devices to have only those functions in the lower section of the diagram. Is that correct? Likewise for the even-numbered pins.

I thought each Smart Pin had the complete functionality shown in the entire block diagram. The diagram, however, indicates differences in the circuits that connect to even pins and to odd pins.

Would someone explain, please? --Jon

Enjoy!

Mike

And, yes, the USB smarts happens to be managed from the even Smartpin also. USB needs a differential pair so it was easiest to do it that way I presume.

I'm considering an attempt to make the smartpin routing and configuration something much more dynamic that someone can play with on a web page.

What do you think?

EDIT: Hehe, the schematic like diagrams that I did were done with Logisim. They were done as documentation but it also allowed me to verify the function by twiddling the inputs.

The idea is to visually illustrate the active routings and component level configuration to make it visually obvious.

I have a concept in mind for how to do it, but the tools to implement cleanly and without extra complication it are still being sought. Early experiments show promise but I'm still skirmishing with tooling.

Ideally it should be easy to throw onto a static hosting site like gh pages where we can all use it. First things first, though.

@evanh Is this how you wanted it changed?

Excellent. Just remembered one more thing - Put an arrow head on the dashed line through the smartpin block to IN.

Ok, how's this?

Evanh

This sure helps with select A\B. If you don' mind I would like to include drawing in my notes document.

Regards

Bob (WRD)

Bob, sure thing.

Rayman, maybe give also change DAC label on the green line to DACbus or DACBUS or DAC_Bus. Whichever you like most. Just to make it clearer the line is the 8-bit data lines and not the analogue.

Maybe like this?

Yes, nice touch with the bit widths.

I've just updated the T-block functional schematic too. Corrected the logic for OUT override with smartpin configured. And also now uses %SSSSS labelling for smartpin mode field instead of the older %MMMMM.

And matching M-block (was called P-block), just new labelling, no logic change:

[doh! Spoke too soon. Didn't double check on the scope first]