Prop2 Family

cgracey

Posts: 14,315

cgracey

Posts: 14,315

In our discussions with pjv, we realized that the Prop2 can be stripped down, pretty much exactly like we've been doing on various FPGA builds, and very significant savings can be realized in fabrication. And by using plain I/O's in place of some smart pins, the edge of the die can be shrunk greatly, while maintaining the same number of I/O's.

Smart pins take 330um, while plain I/O's can take only 100um. By making variants where groups of 4 pins alternate between smart and plain, the pad frame can be reduced dramatically. Then, the guts can be shrunk, as well, by reducing the cogs and the hub RAM.

To synthesize these variants, it's only a matter of parameters in my top-level Verilog module. Then, Treehouse must take our several existing pads, along with a new plain I/O, and assemble pad frames which accept the synthesized guts. Once we get everything scripted, with the constraints set for each type of pad, it becomes very easy (and inexpensive) to make variants.

OnSemi's cost for a 180nm mask set is about $60k, which is way less than I was thinking. I was adding in the initial production run cost, to make it more than that, in my head. Anyway, with simple-to-make layout variations and shuttle runs, we can make all these for a fraction of what we had assumed separate chips would cost.

We're on track for making the big one, first, but as soon as we prove that it works, we can start generating these other designs with little effort and moderate money.

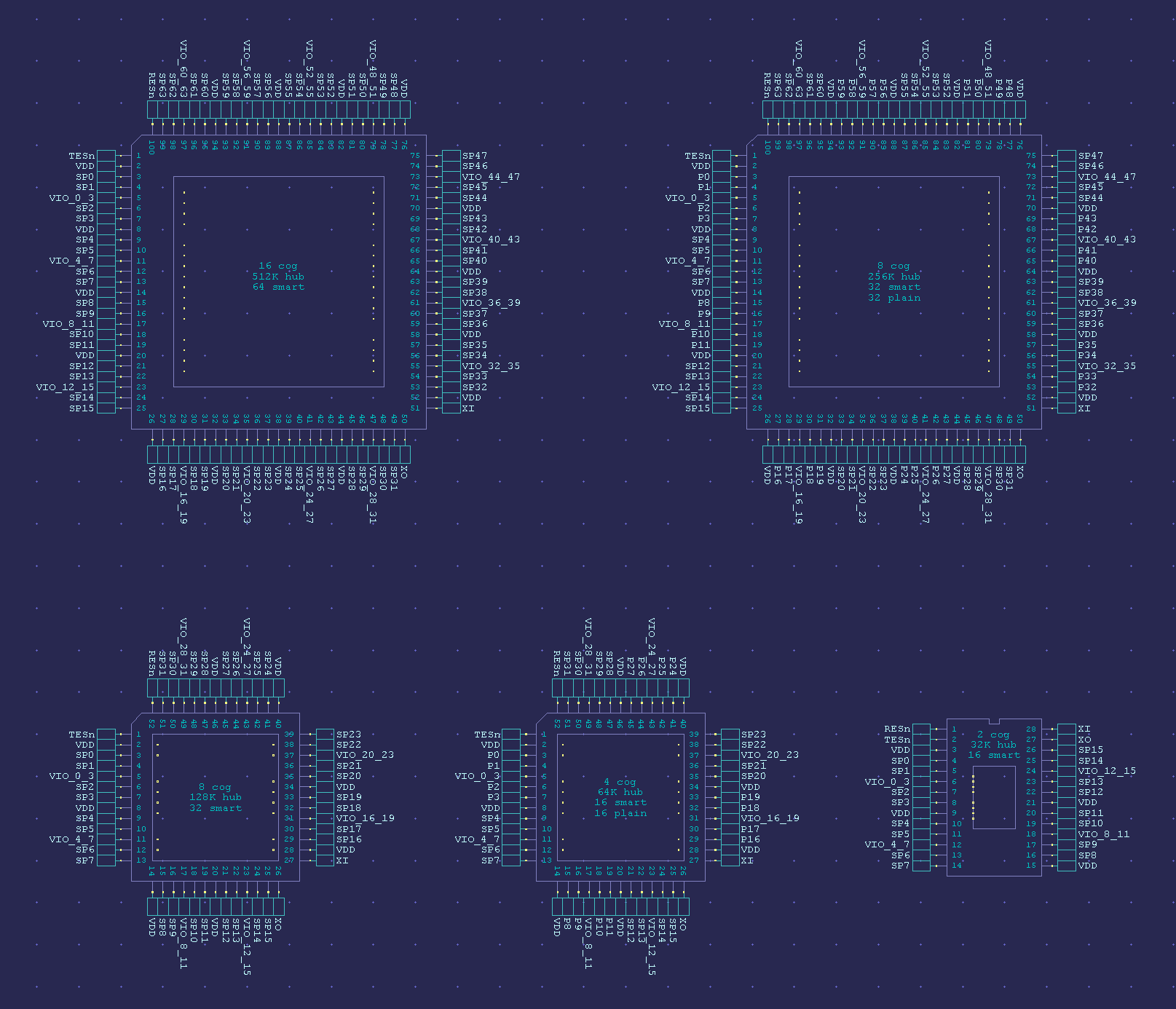

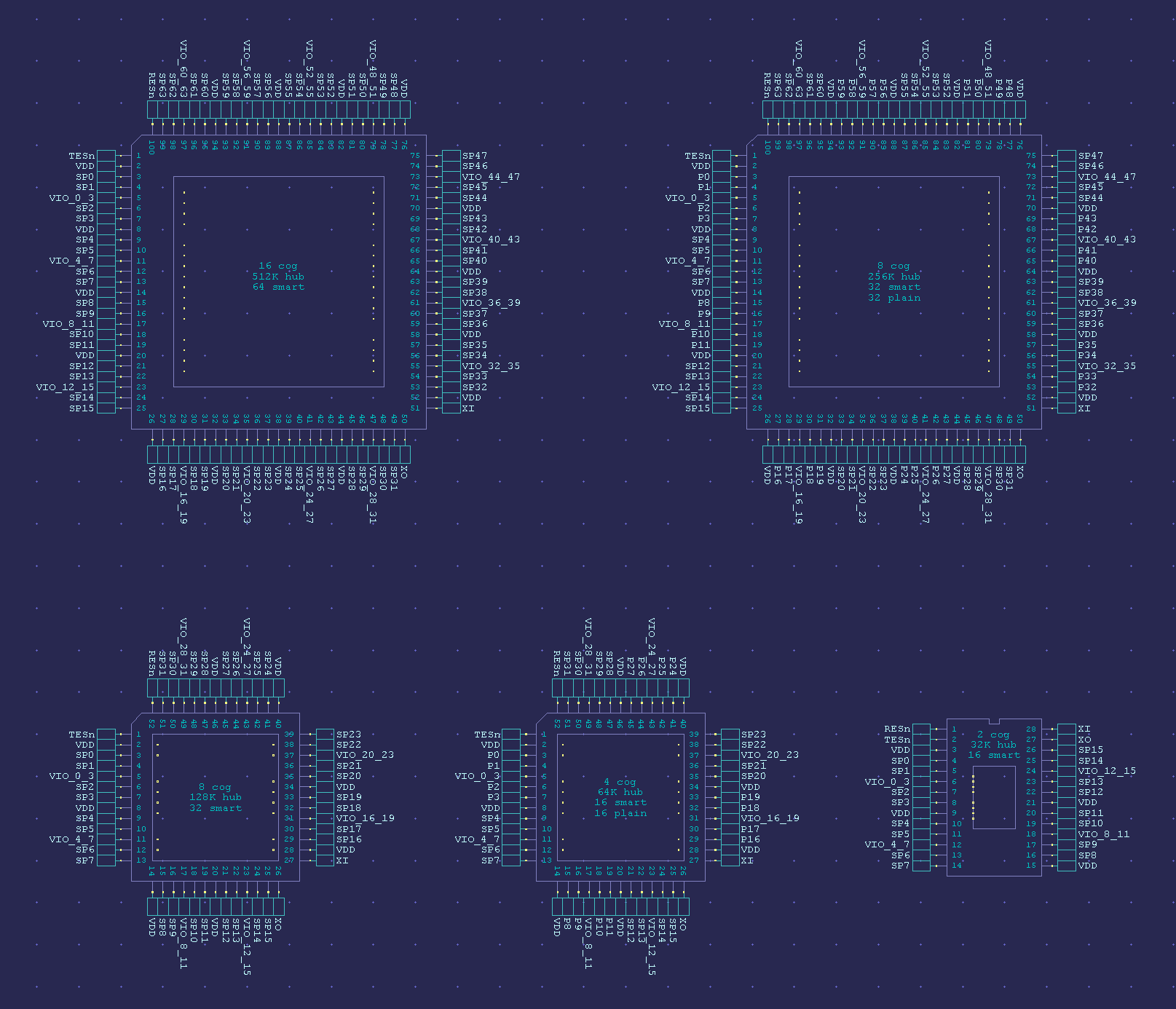

Here's a set of pinouts for what seems like a well-divided family of parts. The smallest part will cost only ~20% of what the big one will. This way, you can prototype with the big guy and then target one that is sufficient. Note that each TQFP package size has two pin-compatible variants, allowing you to use a bigger or smaller part on the same PCB design, as long as your smart pins are in the same place where the lower version has its smart pins (as opposed to plain I/O's).

On second thought, that 28-pin version can have 4 cogs. Two is too few.

Smart pins take 330um, while plain I/O's can take only 100um. By making variants where groups of 4 pins alternate between smart and plain, the pad frame can be reduced dramatically. Then, the guts can be shrunk, as well, by reducing the cogs and the hub RAM.

To synthesize these variants, it's only a matter of parameters in my top-level Verilog module. Then, Treehouse must take our several existing pads, along with a new plain I/O, and assemble pad frames which accept the synthesized guts. Once we get everything scripted, with the constraints set for each type of pad, it becomes very easy (and inexpensive) to make variants.

OnSemi's cost for a 180nm mask set is about $60k, which is way less than I was thinking. I was adding in the initial production run cost, to make it more than that, in my head. Anyway, with simple-to-make layout variations and shuttle runs, we can make all these for a fraction of what we had assumed separate chips would cost.

We're on track for making the big one, first, but as soon as we prove that it works, we can start generating these other designs with little effort and moderate money.

Here's a set of pinouts for what seems like a well-divided family of parts. The smallest part will cost only ~20% of what the big one will. This way, you can prototype with the big guy and then target one that is sufficient. Note that each TQFP package size has two pin-compatible variants, allowing you to use a bigger or smaller part on the same PCB design, as long as your smart pins are in the same place where the lower version has its smart pins (as opposed to plain I/O's).

On second thought, that 28-pin version can have 4 cogs. Two is too few.

Comments

Will these all run at the same clock rate? Or will the reduced stuff make it possible to run smaller ones faster?

Would a variant of the large size that is less cogs but more memory be possible? Say 8 cog, 1MB hub, 64 smart (or 32 smart 32 plain), or whatever combination that could fit 1MB hub (or more?).

More hub ram is always useful, even with less cogs.

On the big pad frame, we could do more RAM and less cogs, but there's not enough room for 1MB.

They should all run at the same speed. The critical path is pretty much in the CORDIC, already.

Hehe, the myriad of combinations is beginning ...

Please, everyone else uses either 48-pin or 64-pin and those are the sizes for which cheap adapters are available.

I guess the 28-pin is DIP? Why not pair that with a 0.8mm 32-pin QFP

TQFP64 is more common than TQFP52, which may make it cheaper.

There is also a 0,4mm TQFP64 ( as well as 0.5 and 0.8mm ).

28 pins is unusual these days, a better choice would be TQFP32, as mentioned.

That is 0,8mm, which is wave solderable, and much thinner than SO28L

I noticed NXP seem to have pruned all DIP packages from their LOGIC families.

DIP moduiles can make sense, but DIP ICs are dinosaurs.

Did you talk to OnSemi about Wide-Vcc, like 1.8~5.5V, for the smaller parts ?

Makes sense to use the fastest process possible for the largest variant, but as these scale down, power and voltage become more important.

Of course, at the same time total power envelopes drop, making the Core Regulator more practical on smaller parts.

I can see the old logic families not selling DIPs now, they aren't exciting for hobby/educational material, but there is plenty of peops still buying DIP micro's. I'm sure Parallax can verify this.

All that said, the underside GND is a nice feature for the Prop2 because of its analogue needs.

Does DIP P1 still sell?

I suppose it's the need for twin supplies that makes it not as easy as P1...

Can the baby version have an integrated LDO regulator for the core voltage?

Actually, I guess you can just make PCB with DIP footprint...

Would it be possible for all 4/5 variants to be mixed on the one wafer ???

Might therefore a mask set be ~$60K for the wafer ?

If so, it might be actually cheaper to have all the variants produced at one time. Of course, the numbers of each on a wafer would be fixed in whatever ratio you chose, but sometimes this is a cheaper overall cost due to the sharing of the mask costs.

eg 12 Cogs + 32 smart pins + 32 I/O + 1MB hub ram ???

Chip said no to even 8 Cogs, 32+32 I/O, 1MB. I'd guess it would require much more drastic changes like removal of LUTs and more.

I like it

However, you will need to check if the microchip patent is still valid or not. Check this:

http://microcontroller.com/news/luminary_micro_lawsuit.asp

http://www.finetpat.com.tw/default.asp?ID=186

http://www.google.com/patents/US5847450

If not sure, you can choose a package with at least 32 pins.

The possibility of designing with a full feature chip then easily pruning down for production cost savings gives a nice "Buffer" zone for guys like me who are never quite sure how much "Horsepower" we might need. Introducing a new product with smaller (cheaper) chips but having a solid, easy upward migration path gives another level of comfort too.

I think that keeping this "family" of P2's in mind will make it much easier to attract new designers to the Parallax bandwagon.

Onward and upward!

That patent is about:

“Microcontroller Having An N-bit Data Bus Width with Less than N I/O Pins and A Method Therefore”

WTF?

All I can say is the patent office needs to set a minimum IQ requirement and some level of knowledge of the area the patent applies to for whoever is making the decisions on what is patentable.

Yep. In the old days patent offices used hire people like Einstein as patent clerks.

The whole patent idea should be scrapped. It has never worked.

Back in the day when it was time to build steam engines that could create rotary motion to dive machines in factories James Watt was not allowed to do it the obvious way, use a crank shaft. Why because some jerk had a patent on using a crank handle in a steam engine. I'm mean really, the crank handle had been around for millenia. So james had to develop all kind of complex and inefficient mechanisms to do it, like sun and planet gears.

A hundred years ago someone wrote a book about the history of steam power, and noted how the patent system had held up the development of steam power by two decades.

Or they should just crowd source the whole patent application checking business. Think "patentoverflow.com". All us people out here could soon tell the them if their was prior art or if the "invention" was not actually trivially obvious to anyone versed in the arts.

Yes, note Parallax do not make the Stamp, using DIP parts.

I'm sure DIPs still sell, but for existing designs, much less for NEW design starts ?

I think that requirement kills DIP anyway, so the DIP discussion is moot.

The other small package choice is QFN32, but that cannot wave solder.

It comes down to PADDLE size, and actual package is an easy late-choice.

Provided the die fits, if someone wants enough QFN32, Parallax can run that package.

re 28 pin version

Not sure whether there are any specific reasons, but might it be more prudent to shift RESn to pin 14, and shift XI/XO down to pins 16/15 ???

This would mean that the pins 1..13 and 16..28 would match the QFP51 LHS & RHS pinouts.

In the smaller 8 cog versions, would the egg-beater be reduced to 8 wide, meaning normal hub would now be 1:8 rather than 1:16 clocks ie 2x the hub speed of the 16 cog version?

Similarly with the 4 cog version?

Would the 4 cog version actually derive much benefit from the egg-beater silicon? (hub exec would be ~50% speed without egg-beater)