Prop123 -A9 Testing

cgracey

Posts: 14,303

cgracey

Posts: 14,303

After getting the RGB LED problem solved, the -A9 board seems to be working great.

There's a lot to test, but so far, it's running 16 cogs well.

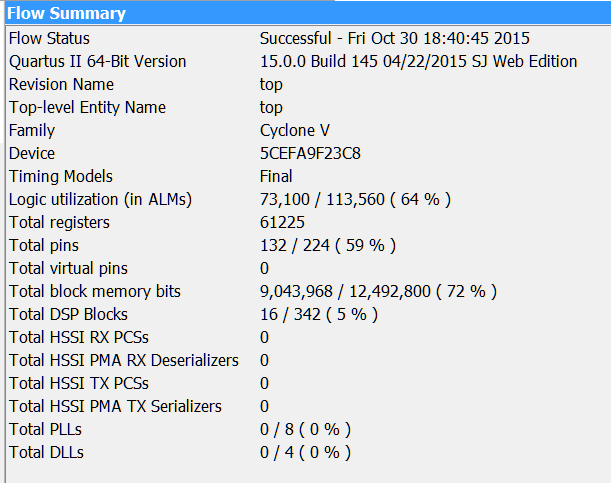

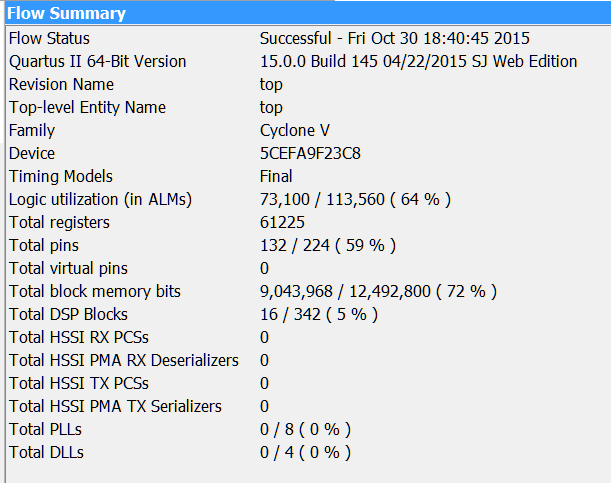

Here's from Quartus:

Here's an exciting movie of all_cogs_blink.spin:

https://drive.google.com/file/d/0B9NbgkdrupkHdjhUU2RRWHA2ejg/view?usp=sharing

There's a lot to test, but so far, it's running 16 cogs well.

Here's from Quartus:

Here's an exciting movie of all_cogs_blink.spin:

https://drive.google.com/file/d/0B9NbgkdrupkHdjhUU2RRWHA2ejg/view?usp=sharing

Comments

The MUL/MLS multiplier in each cog uses a DSP block.

The CORDIC is nothing more than set of add/subtract stages.

What is the build time on that ?

It seems to have 1M of HUB, does that mean OnSemi can fit more RAM ?

At 180nm, 512KB is all we can fit. The architecture can do 1MB, though, and the -A9 has the RAM, so I had it fill it out.

hehe, I did have the winky, to show it was not an entirely serious question

You don't need more RAM you just need to learn how to write more efficient code

Great looking board!!

Can the PLL's be coupled to look like P2 PLLs' for run-time changes, and with the same quantisation ?.

Or, is the design limited to build-time PLL choices ?

ALMs and LEs are not the same. An ALM can do more, but there isn't a simple relationship between the two. I think I read somewhere that you can estimate 1 ALM ≈ 2.5 LE. But the actual number varied considerably based on design and compilation settings.

For testing purposes, please keep it at 512K.

Even after the P2 chip comes out, somebody who needs more RAM might spring for a P123 board...

I wonder about JMG's question too. If the PLL is working, can we modify the clock?

You can reconfigure PLLs at run-time, but you need to feed them a configuration bitstream. Not simple.

So it looks like the P123 A9 is a must for complete emulation. Happy to see the P123 A9 is coming along.

Yes.

Both are useful to have.

Certainly, for final FPGA testing, whatever the P2 chip will have ( which may not be exactly 512k) should be used.

!M is still useful to test, to fully confirm the Opcode reach, as OnSemi might come back and say 580k of RAM can fit.

Plus, as other mention, it is a useful FPGA-only target

In fact, the FPGA can support more than that.

hmm.. Less than ideal, but I suppose partial config may allow a selection of PLL settings to be tried, via a few small PLL_Setting files ?

I also find

https://www.altera.com/content/dam/altera-www/global/en_US/pdfs/literature/an/an661.pdf

which shows an ALTERA_PLL_RECONFIG IP Core, but that does not look seamless either.

I note that A9 has 8 PLL's so an alternative approach could be to choose some useful defaults for multiple PLLs and then select which to use (Assuming that can be a run-time choice?)

The question is, since 130nm was the tick for 180nm's tock, does OnSemi offer 130nm with the same features as 180nm, then allowing for 1MB of RAM?

EDIT: I looked and their next step is 110nm. What's very interesting, aside from 3.3v and 5v tolerance is that the power dissipation at 110nm is 9nW per Mhz per gate and it's 46nW per Mhz per gate in 180nm! That's 5 times less power dissipation!

One downside is that 180nm is considered their 'low price' solution while 110nm is not.

I wonder how much more expensive it is. I will ask them, for whatever it's worth, at this point.

Update... I went and looked at their site to see what technologies are offered today and they only go down to 180nm, in house. They outsource those other technologies. We talked to them once about 65nm, but it was going to be over half a million to get it done. I think we need to just finish this at 180nm and then see what we can do, after that.

I worked at ASML when they were developing the 180nm lithography machines in 1999. Those machines use Deep Ultraviolet lasers (DUV) to project the chip patterns onto a wafer through a gigantic lens. To get better resolutions, you need shorter wavelengths of light (such as EUV -- Extreme Ultraviolet) which get absorbed by pretty much everything so current machines use a vacuum and mirrors instead of air and a lens.

So yeah, going to a better resolution is not just a matter of adjusting some knobs and running the wafer a little slower or something. They have to use different machines and apparently OnSemi doesn't have those.

===Jac