Dual I/O with DTR with onboard flash?

in Propeller 2

Has anybody tried this? Seems like it should work with the usual SPI connection...

Think could make transfers 4X faster...

Comments

For boot up? Dual IO is already in the common flashloader program.

I don't use it. I had to buy AT25SF128A-SHB-T due to the chip shortage and the dual spi wasn't working. https://forums.parallax.com/discussion/comment/1525737/#Comment_1525737 Nothing more permanent than a temporary solution. My programs are relatively small anyway.

Dual IO with DTR (AKA DDR) is already being used for regular boot from flash?

Guess didn't know that...

I don't think the flashloader uses DDR, but I haven't looked at the latest version.

Most flash chips don't support DDR?

That DualSPI version (I added the DualSPI feature to existing code) was probably my code I wrote for the early Eval board only. I never tried to make it a generic solution, which wasn't particularly wise. And no, it didn't do DDR clocking. I've not seen that for any SPI unless you count HyperBus.

PS: Chip did a simpler more generic version for Pnut.

DTR/DDR seems to be a new feature?

It's a bit confusing as there appears to be two datasheets for W23Q128JV. One with DTR and one without.

The one without says this:

For DTR, QPI supporting, please refer to W25Q128JV-M DTR datasheet.So, I'm not entirely sure what is going on there...

Totally a new feature for 4-bit parts. What package are these? There has been 8-bit OPI interface using identical package, pinout and DDR clocking as HyperRAM but with SPI type command set. Those appeared a few years back. Almost forgot about them.

I’m looking at the part that parallax uses on their boards…

Ah ... looking in schematic parts list of Eval rev C lists U301 as W25Q128JVSIM-TR. Missing the D in the suffix.

Exactly the same for EC32MB rev B card.

I note in the new W25Q128 datasheet it also now has the same microBGA package, as is used by HyperRAM, as one of its packages. I'm guessing those are the DDR parts ... it'll even be the same pinout as HyperRAM, minus four data pins. Not that I bothered to confirm.

IDK, both Digikey and Mouser show the SOIC part as having the DTR feature, unless I'm missing something...

Wondering if it was always there, but just not advertised at first or something...

Yeah, you're right. I've had a read now and yep, all the new parts are "DTR" capable. It's not quite full DDR. That'll be why they are naming it DTR. It's akin to QuadSPI/DualSPI, ie: DTR doesn't apply to the command. But it's also applied on top of those - So you can have any of SPI/DualSPI/QuadSPI/QPI combined with DTR.

It's getting messy.

EDIT: Looks like there is no DPI mode. I just presumed that existed.

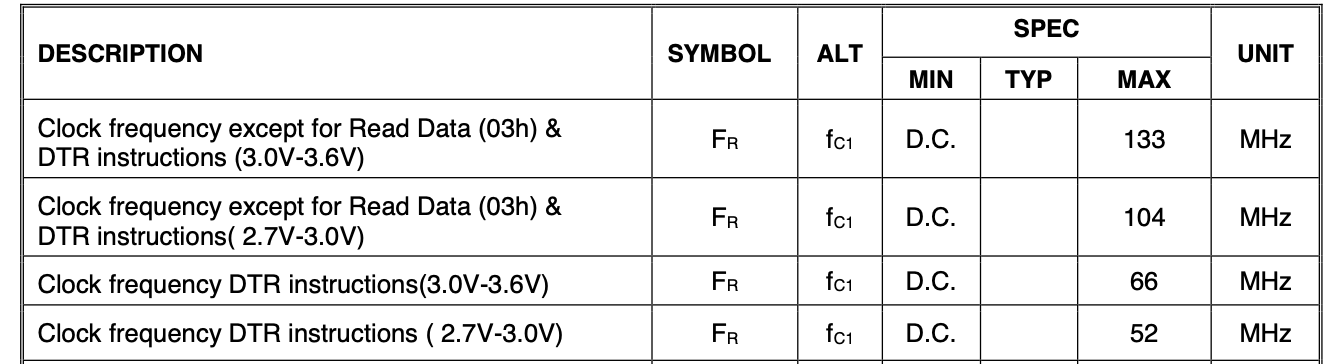

Looking at the data sheet, it seems strange that DTR operation halved the maximum clock rate from 133MHz to 66MHz. Pity about that. Otherwise it could have transferred bulk data significantly faster in this mode. Perhaps they are gearing up for the rate to be sped up over time in future parts using this same interface. Without the DDR actually clocking the data faster the only real gain you get from DTR is by sending the lookup address out using multiple data lanes instead of just one. I do like the continuous read mode operation though, that could help a little bit too for repeated read transfers, at the expense of driver complexity and maintaining some extra state; it seems intended mostly for XIP usage. For long sector length transfers it'll hardly make a difference however.

https://www.winbond.com/resource-files/w25q128jv_dtr revc 03272018 plus.pdf

Not sure that is right. There is a 66 MB/s limit. Maybe 66 MHz is for quad operation with dtr?

Ok, took me a sec to decipher that... That 66 MHz is referring to the low speed "Read Data" command. You have to use the "Fast Read" command to go high freq...

Are you sure, @Rayman? I read it such that it appears that the DTR instruction transfers are limited to 66MHz but it's not 100% clear. Do you believe it is only applying to the initial instruction component of the DTR transaction and data can be subsequently clocked at 133MHz DTR? That would be good if true - and may make more sense why the feature was provided in the first place.

Here is the related snippet from the original data sheet.

Actually in the features section it lists this:

So it would appear that it could clock a nibble on the rising and falling edge of a 66MHz DTR clock making 66MB/s in 4 bit mode. Ugh. No 133MHz operation then.

Ok, yeah, guess it is 66 MHz. That jives with "equivalent clock rates of 266MHz (133MHz x 2) for Dual I/O"

Unfortunate if true. Seems you need QPI to get full speed...

Now, I don't get the point of DTR at all. Why have double transfer rate but at only half the clock speed? Don't see how that buys us anything...

That's what I was saying, yeah. My only thought was it was in preparation for faster speed devices one day by eventually removing that 66MHz restriction, but keeping the same signalling.

It'll overclock. Of course, it'll overclock without using DTR too. But DDR clocking is electrically less stressful on the clock pin.