Who's Copying Who?

erco

Posts: 20,263

erco

Posts: 20,263

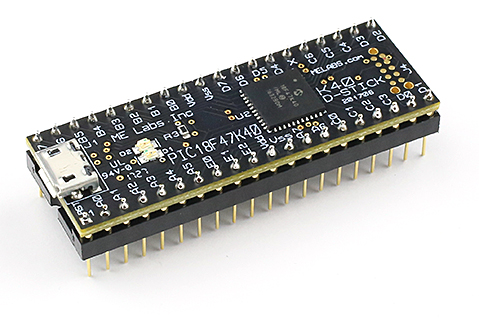

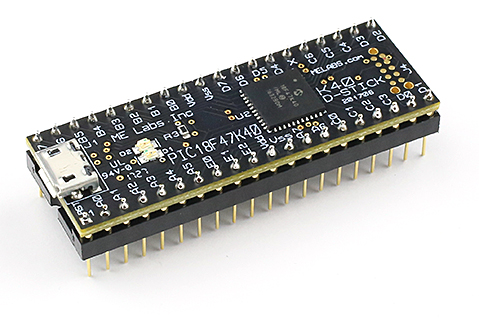

Just saw this new D-Stick in the Oct SERVO issue. Looks a lot like the FLiP module, amirite? Is this the new form factor? http://store.melabs.com/prod/DSTICK/DS2.html

Comments

Sad,

Mike

I agree, but they do have a good reason for not using long header pins.

Rounded machined pins are easy on spring contacts allowing for multiple insertion cycles

I have had no success in finding long enough machined pins for a header on top and bottom pins long enough for a prototyping board or IC socket.

One of my first PIC experimenters boards came from ME Labs. I wasn't fond of PIC BASIC, but it's serviceable.

As for the form factor of combining an MCU with all the other components for a stand-alone device, the original BS1 might be the forerunner of most of these. With the advent of USB and micro connectors, they have the PC port built into the module, which allows the module to be truly independent: apply power and go.

I'd be interested if there was a mainstream (readily available commercially) composite module than the BS1. To fit the bill, it has to combine MCU, program memory, crystal or resonator, regulator, RS-232 interface, and other pieces. There may have been, but my attention wasn't going that direction in the early 1990s. I was still experimenting with Z80s!

They were not in a DIP format but they were newer CPUs supported by clock and voltage translation circuitry.

I think a few of the old 80's 6502 upgrades were in a DIP format.

I also remember replacing the 8088 from an IBM PC with a V20 processor in the early 90's.

DIP is alive for lots of stuff (including Z80 etc). And the Parallax Propeller (P1), of course..

(Hm, I have a V20 (and a V30 or two) somewhere.. no PC around to upgrade though.)

That was great except the only way to wake it up from deep sleep was my poking it with an NMI. That meant that every possible source of interrupt had to go through the NMI and hence to the NMI handler. That handler then had to take care of all the interrupt source masking, interrupt priorities, nested interrupts etc. It became the most horrible, twisted, fragile, incomprehensible piece of assembler I have ever seen! It suffered no end of race conditions for a long time.

Then, they wanted to build an Ada run time and it's scheduler on top of it, grrr....

It's been a long time so I may not remember correctly but I thought there were several drop in faster versions of the 6502. I think most were made for the Apple II.

Heater,

Aren't you glad that you don't need to bother with interrupts on the Propeller. That was genius on Chip's part.

I was even campaigning against adding interrupts to the P2 design. Which it now has....

The first upgrade for the 6502 on the Apple II was the 65c02, but it was not a drop-in replacement. The Apple II had severe timing issues and some 65c02 (there were multiple sources) would work in a subset of machine models, others would not. There were some articles about it in Apple Assembly Line around the time, by Bob Sander-Cederlof. He keeps the magazines online somewhere btw.

The 65c02 CPU became faster over the years (today's DIP versions are 14 MHz, but that's very conseratively rated - 25MHz is possible under normal conditions), but the Apple can't run faster than it's designed for. If you wanted faster it would require a co-processor extension as far as I remember (which could even be a Z80, to run CP/M)

Tor, I think you have them mixed up. The 802 is a 16-bit chip but uses an 8-bit bus while the 816 was 16-bit on a 16-bit bus.

Heater, hopefully Chip has interrupts disabled by default.

No idea. But as far as I understand interrupts in one COG can not influence the deterministic execution of any other COG. So all is good.

You're right, I mixed up a couple of my memory threads. The GS used the '16 of course. The 65802 was actually sold as an upgrade for the Apple II, for some time.

In that case the programmer has given up deterministic execution in the same way as waiting on a pin or LOCK etc.

All sounds good to me.