Possiblity to add more COG ram to Prop II

Sapieha

Posts: 2,964

Sapieha

Posts: 2,964

I still study my processor.

·

In present instruction set of adressing of memory in present COG instructions can not adress anymore as 512 longs.

But there are one·possibility to add more RAM to COG processor.

With only 2 special instructions it is possible to address more memory, retaining·persent instructions and addressing mode add compatibility·in COG.

Diagram coming soon.

▔▔▔▔▔▔▔▔▔▔▔▔▔▔▔▔▔▔▔▔▔▔▔▔

Nothing is impossible, there are only different degrees of difficulty.

Sapieha

Post Edited (Sapieha) : 9/11/2008 2:02:29 PM GMT

·

In present instruction set of adressing of memory in present COG instructions can not adress anymore as 512 longs.

But there are one·possibility to add more RAM to COG processor.

With only 2 special instructions it is possible to address more memory, retaining·persent instructions and addressing mode add compatibility·in COG.

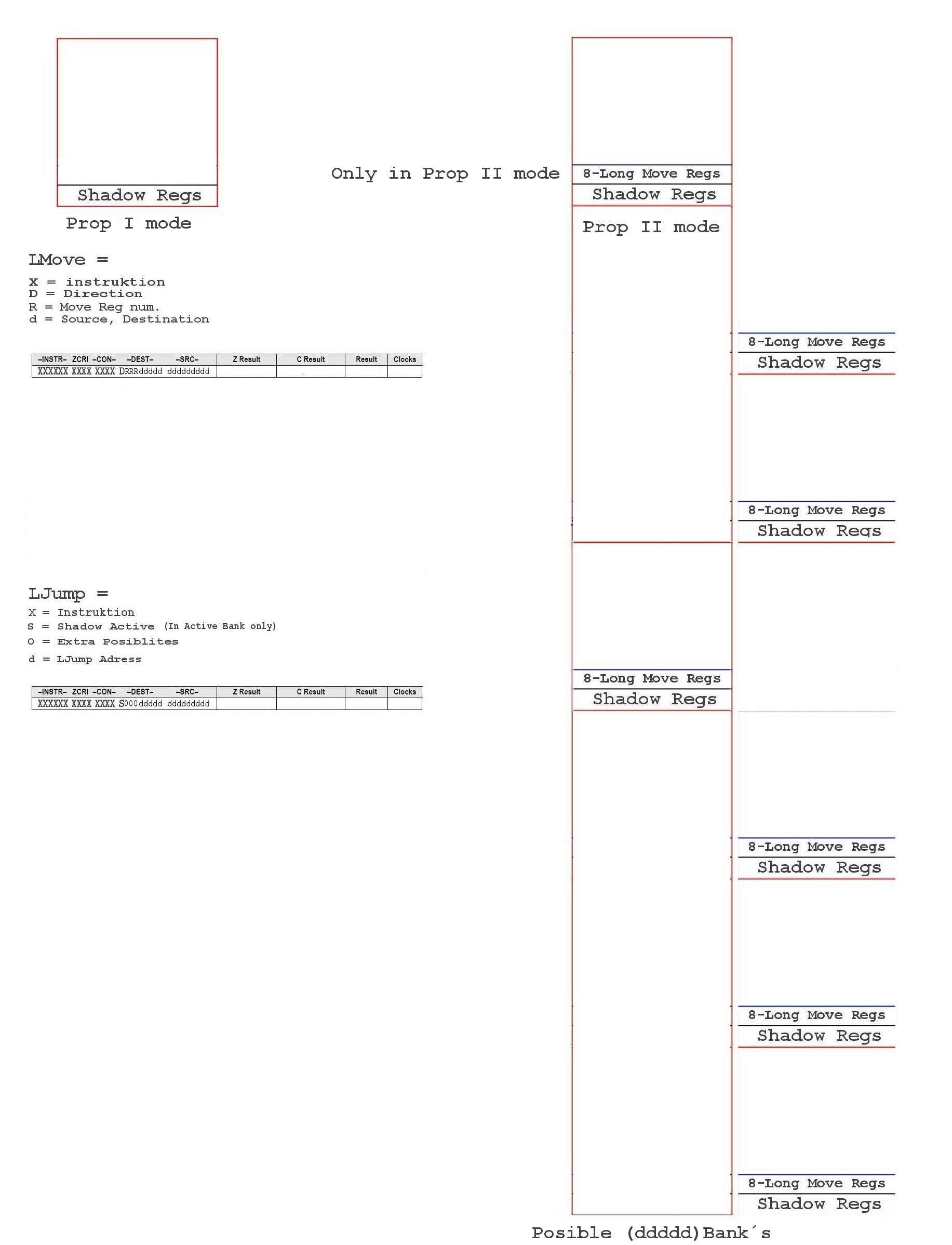

- Long Jump (Long address)

- Long Move (8 regs in COG to all of memory) (regs to memory and memory to regs)

Diagram coming soon.

▔▔▔▔▔▔▔▔▔▔▔▔▔▔▔▔▔▔▔▔▔▔▔▔

Nothing is impossible, there are only different degrees of difficulty.

Sapieha

Post Edited (Sapieha) : 9/11/2008 2:02:29 PM GMT

Comments

> addressing mode add compatibility in COG.

Can't see how to access registers with more RAM.

Nick

▔▔▔▔▔▔▔▔▔▔▔▔▔▔▔▔▔▔▔▔▔▔▔▔

Never use force, just go for a bigger hammer!

The DIY Digital-Readout for mills, lathes etc.:

YADRO

It is said 250KB ram on HUB.

For more procesing power it is beter more to COG and less to HUB

▔▔▔▔▔▔▔▔▔▔▔▔▔▔▔▔▔▔▔▔▔▔▔▔

Nothing is impossible, there are only different degrees of difficulty.

Sapieha

We all have our opinions of what would be better or best. The only one that counts is Chip's and he has made it clear that there will be 512 longs of cog memory for each cog on the 2nd generation Propeller. There are all kinds of other constraints on what's possible or doable or preferable or practical. Some of them have to do with the area of the chip required for something, some have to do with the manufacturing process involved, etc.

Anyways it can not come soon enough.

Sapieha: I really like your sig.

Don't forget, it will have 256K of RAM ( IIRC ) and can therefore using various methods you can bring in extra instructions like in the Large Model Mode, that people are working on for Prop1, with 256K of ram and a processor 8 times faster, this shouldn't really be an issue, but if you truely want more ram for your program, then either add extra ram and stream code in from that, like Andre's H512X SRAM addon, or failing that use another processor?

Just out of curiosity, what is it you need all those extra instructions for? I know it'll be handy to have more cog ram, but it's a fair trade for the performance this microcontroller has.

I suppose variables / read/write access could still be restricted to <512 and just have instructions >512 and an use call pointer instead of call #, and that would allow >512 longs keeping current instruction set.

Baggers.

And self-modifying code?

Nick

▔▔▔▔▔▔▔▔▔▔▔▔▔▔▔▔▔▔▔▔▔▔▔▔

Never use force, just go for a bigger hammer!

The DIY Digital-Readout for mills, lathes etc.:

YADRO

My model use.

Bank model with 8 dedicated regs in one bank to move variables from one bank to another and long jump to acces code in bank's.

And stil have compatibility with old Prop I code.

▔▔▔▔▔▔▔▔▔▔▔▔▔▔▔▔▔▔▔▔▔▔▔▔

Nothing is impossible, there are only different degrees of difficulty.

Sapieha

http://forums.parallax.com/showthread.php?p=669485

http://forums.parallax.com/showthread.php?p=678552

With an eight-fold increase in speed, faster hub access, more cogs and more memory, Large Memory Model programming is a practical and a feasible mechanism to overcome cog memory limitations for most cases.

The current issues with LMM are not particularly technical nor hardware related but a matter of not having the right tools available to make it easily realisable and usable. There are plenty, and a variety, of good ideas out there and, in time, solutions will arrive.

Post Edited (hippy) : 12/8/2007 6:36:25 PM GMT

Thanks for links.

But it is slightly different way.

In my model it is posible tu run both code and store data.

In entire memory block 512*X block´s

This open posiblites to run X-diferent intrerpreters on same prop.

▔▔▔▔▔▔▔▔▔▔▔▔▔▔▔▔▔▔▔▔▔▔▔▔

Nothing is impossible, there are only different degrees of difficulty.

Sapieha

Added Memory model Diagram.

And Instructions to add to COG assembly

▔▔▔▔▔▔▔▔▔▔▔▔▔▔▔▔▔▔▔▔▔▔▔▔

Nothing is impossible, there are only different degrees of difficulty.

Sapieha

▔▔▔▔▔▔▔▔▔▔▔▔▔▔▔▔▔▔▔▔▔▔▔▔

Paul Baker

Propeller Applications Engineer

Parallax, Inc.

It is only my possible resolve to have more durability on yours Processor.

It giving more power than yours resolve.

It is not my problem but I thinking if your want trade away more yuor should construct Powerfull Processor.

You writing "there will be a block move function" it not solve Fast Buffers And more advanced programings algoritms.

And more advanced Interpreters in only 512 longs with Propellers FastSpeed but only interpreters in same class as Spin.

Spin is good interpreter but its speed is not good.

▔▔▔▔▔▔▔▔▔▔▔▔▔▔▔▔▔▔▔▔▔▔▔▔

Nothing is impossible, there are only different degrees of difficulty.

Sapieha