See my PropII prototype

Well, sort of....

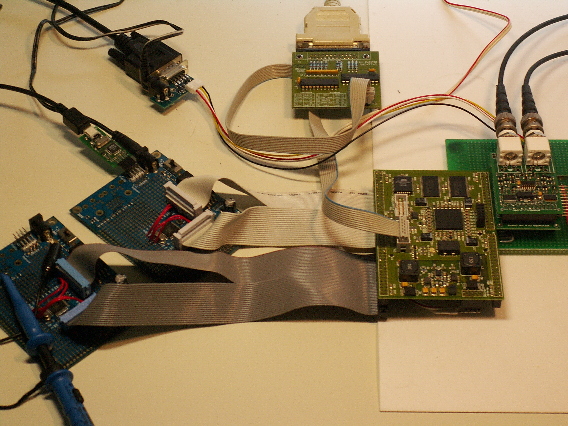

The heart of my super prop is an·FPGA module with an·Altera 1C12,·that has 2 banks of 256K16 SRAM and 4x20 I/O pins.

See http://www.elektor.com/products/kits-modules/modules/flexibele-fpga-bouwsteen-(040477-91).91417.lynkx

Two ports are occupied by·props, that each have a 16 bit data path to the FPGA·and a memory bank. They can talk to each other through a 4k16 dual port memory in the FPGA. This gives me 16 COGs, 40 + 2x8 = 56 free I/O pins.·I am now testing·the RCOGNEW·(R for remote) software.·Close to PropII, is'n it?

The target of this experiment is·to·learn·programming FPGA's using Verilog and Quartus.·Right now I am·using only one·prop to control and test my Verilog code in·the·FPGA·that acts as a glorified data switch. But it is fun to have·PropII functionality as a design target.

The third port is already connected to·a 2 channel·100 MSPS 8 bit A/D·http://www.fpga4fun.com/Hands-on_Flashy.html·that·in the future must make·video signal acquisition possible. But that is·a lot more Verilog learning,·coding·and testing to go.

Nico Hattink

The heart of my super prop is an·FPGA module with an·Altera 1C12,·that has 2 banks of 256K16 SRAM and 4x20 I/O pins.

See http://www.elektor.com/products/kits-modules/modules/flexibele-fpga-bouwsteen-(040477-91).91417.lynkx

Two ports are occupied by·props, that each have a 16 bit data path to the FPGA·and a memory bank. They can talk to each other through a 4k16 dual port memory in the FPGA. This gives me 16 COGs, 40 + 2x8 = 56 free I/O pins.·I am now testing·the RCOGNEW·(R for remote) software.·Close to PropII, is'n it?

The target of this experiment is·to·learn·programming FPGA's using Verilog and Quartus.·Right now I am·using only one·prop to control and test my Verilog code in·the·FPGA·that acts as a glorified data switch. But it is fun to have·PropII functionality as a design target.

The third port is already connected to·a 2 channel·100 MSPS 8 bit A/D·http://www.fpga4fun.com/Hands-on_Flashy.html·that·in the future must make·video signal acquisition possible. But that is·a lot more Verilog learning,·coding·and testing to go.

Nico Hattink

Comments

Congrats!!!

I like to view the Prop in biologic terms... so, I see the Prop as the rough equivalent of a brainstem and motor cortex.

The natural question is what do we use for the brain? I think you have just hooked a primative brain to your Prop. Since I have a limited

bandwidth myself, I was originally stuck trying to figure out: "do I study the PROP or dive into FPGA's?" I chose the Prop figuring that

someone would make a path from there to an FPGA. It's nice to see my intuition confirmed[noparse]:)[/noparse]

Please look at http://www.terasic.com.tw/cgi-bin/page/archive.pl?Language=English&No=50#section. Terasic is a well funded start-up company with

offices in South Korea, China, Taiwan, Singapore, St. Petersburg, etc.

There may be opportunities available.

Rich

Nico Hattink