How to generate pulses shorter than your processor can

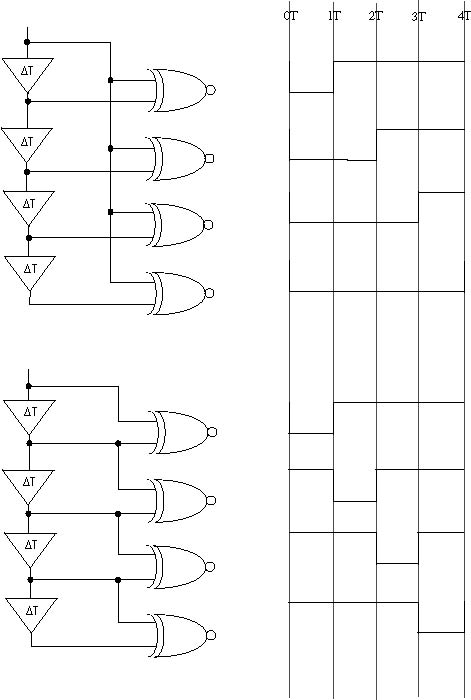

I needed to figure out a way to generate a write pulse on a fast SRAM to enable writing to it at full speed of the processor ,which requires pulsing the /WE low for a fraction of a clock pulse. I think the solution is of general enough utility that I decided to share it. It consists of combining a delay line and tapping the delays with an XNOR (exclusive nor). For an active high pulse (inverse of waveforms shown in figure) use an XOR. The figure shows two different ways of tapping the delays, but it should be clear that any width and offset is possible.

For my application, I am running at 50MHz (20ns cycle) and needed a 12ns pulse. I went with the Dallas DS1100Z-20ns 5-Tap·Serial Delay Line and the SN741G57 which is a configurable single logic gate·and I configured as an XOR. The logic gate·has a 3nS propagation delay, so 0T in the figure starts 3ns after the signal comes in. I tapped the input and the 3rd output so the pulse is from 3ns to 15ns after the input changes. The pulse is sent every time the input changes logic level.

Other parts will work, such as using a buffer instead of the delay line, and using different logic families will produce different delays.

Post Edited (Paul Baker) : 3/26/2005 5:01:36 AM GMT

For my application, I am running at 50MHz (20ns cycle) and needed a 12ns pulse. I went with the Dallas DS1100Z-20ns 5-Tap·Serial Delay Line and the SN741G57 which is a configurable single logic gate·and I configured as an XOR. The logic gate·has a 3nS propagation delay, so 0T in the figure starts 3ns after the signal comes in. I tapped the input and the 3rd output so the pulse is from 3ns to 15ns after the input changes. The pulse is sent every time the input changes logic level.

Other parts will work, such as using a buffer instead of the delay line, and using different logic families will produce different delays.

Post Edited (Paul Baker) : 3/26/2005 5:01:36 AM GMT