P2 Smart Pin Pulse Mode Silicon Bug Report

Goal: Output a group of 16 pulses to drive a step driver module with the Smart Pin Pulse Mode and then output the next group. With only a very small gap due to the time needed for new setup.

Problem: Although the smartpin mode is completely stopped after every group (see code) the pulse stream is not realigned to the setting intervals. (Which are timed with waitct1)

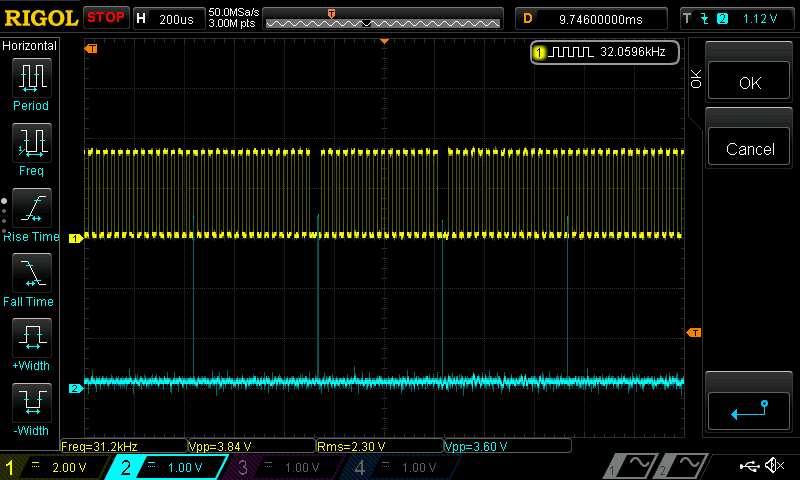

To show the bug in this case setting interval is 17 cycles. So you would always expect a gap of slightly more than one output cycle. Instead the start of the next group shifts in relation to the setting and sometimes the gap is there and sometimes not.

Blue is port 48 to show the relation.

PRIMI(startPulses) { // ( x y pin -- ) starts smart mode pulses

_pinh(48);

int pin= TOS; _drop();

int y = TOS; _drop();

int x= TOS; _drop();

_pinclear(pin);

_pinstart(pin,P_OE | P_PULSE, x, y);

_pinl(48);

}

compiles to:

04b50 | __startPulses 04b50 59 60 64 FD | drvh #48 04b54 E0 D7 02 F6 | mov arg01, pr0 04b58 04 C8 87 F1 | sub pr4, #4 04b5c E4 C1 03 FB | rdlong pr0, pr4 04b60 E0 DD 02 F6 | mov arg04, pr0 04b64 04 C8 87 F1 | sub pr4, #4 04b68 E4 C1 03 FB | rdlong pr0, pr4 04b6c E0 DB 02 F6 | mov arg03, pr0 04b70 04 C8 87 F1 | sub pr4, #4 04b74 E4 C1 03 FB | rdlong pr0, pr4 04b78 50 D6 62 FD | fltl arg01 04b7c 6B 01 08 FC | wrpin #0, arg01 04b80 40 D6 62 FD | dirl arg01 04b84 6B 91 08 FC | wrpin #72, arg01 04b88 6B DB 12 FC | wxpin arg03, arg01 04b8c 6B DD 22 FC | wypin arg04, arg01 04b90 41 D6 62 FD | dirh arg01 04b94 58 60 64 FD | drvl #48 04b98 | __startPulses_ret 04b98 2D 00 64 FD | ret

(If you are using the IN bit of the smart pin to restart the group you always loose one output cycle.)

Neither wrpin #0 nor dirl does really stop the smart pin.

Please verify and include this to the known Bugs. It has cost me some hours.

Christof