Smart Pin A/D D/A Precision (# bits) vs Sample Rate

in Propeller 2

Is there an existing reference here or elsewhere that benchmarks performance of the various Smart Pin A/D and D/A configurations, at least in theory? For example, for 8 bit precision, what is the highest A/D sample rate (Fs) possible on a Smart Pin. If I need only 6 bits of precision (and if this is possible on a Smart Pin), will the maximum Fs increase over the 8 bit case - by how much?

In the other extreme, can I run very slow Fs and achieve much higher A/D precision, say beyond 16-20 bits. What is highest precision possible (what limits this performance?)

Are these limits also true for Smart Pin D/A's?

Comments

Using SINC2 sampling mode, you can get N bits of resolution in POWER (2,N-1) clocks. For example, you can get 6-bit-resolution samples every 32 clocks. At 320MHz, that would be 10 Msamples/second.

You can practically go up to 8,192 clocks to get 14-bit samples, but 1/f noise is limiting your ability to go any further.

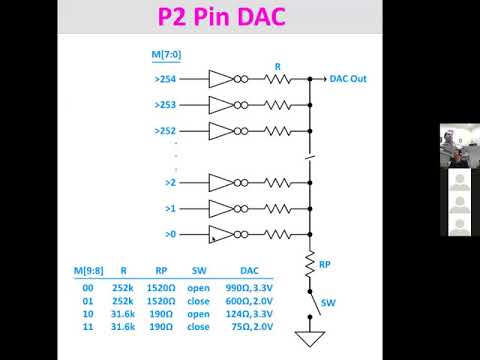

OK Chip - I now understand how SINC2 trades Fs against A/D precision with the 14 bit precision limitation. The D/A side is a different mechanism - best reference I found is your video at Thanks for your help!

Thanks for your help!

Chip,

Where did you find that formula?

You mean this?

An N-bit sample requires POWER (2,N-1) clocks

That's just how the SINC2 filter works.

Well, the Sinc2 hardware generates a doubling of bits so that an N-bit sample only requires POWER (2,N/2) clocks. Eg: 32 clocks can accumulate up to a maximum of 1024 steps. Ie: Where a Sinc1 would need a single 5-bit accumulator, for Sinc2 you need two 10-bit accumulators.

The effective number of bits is what I'm talking about. You wind up throwing away lots of LSBs to get your sample, right?

The smartpins have 27-bit Sinc2/Sinc3 accumulators. The 1/f numbers you've documented don't come close. There must be factors other than "just how Sinc works".

I'd like to know more. How is that calculated?

It was from some document I read about SINC2 and SINC3 during the FPGA work. Our hardware does work as the document advertised. I relayed all this in our own documentation about the SINC smart pin mode.

Evanh, didn't you bring all this SINC filtering up originally here on the forum? I think you were doing a lot of numerical simulations. Saucy Soliton was invloved, too. Maybe I'm forgetting somebody.

I certainly did! I was really keen on it because I knew it was the go to easy method just from scanning FPGA examples. But I had absolutely no idea of how it performed. The maths swamps me too often. Saucy Soliton went way ahead of me once he had the model.

Yes, I did some simulations, but they were only for proving out bugs in the different models we looked at. There was no frequency analysis from me.

Okay, I've found a reference in Jon Titus's document on smartpins - https://www.dspguide.com/ch16.htm I'll have a look at that tomorrow after work and sleep. I'm on evening shift this week.