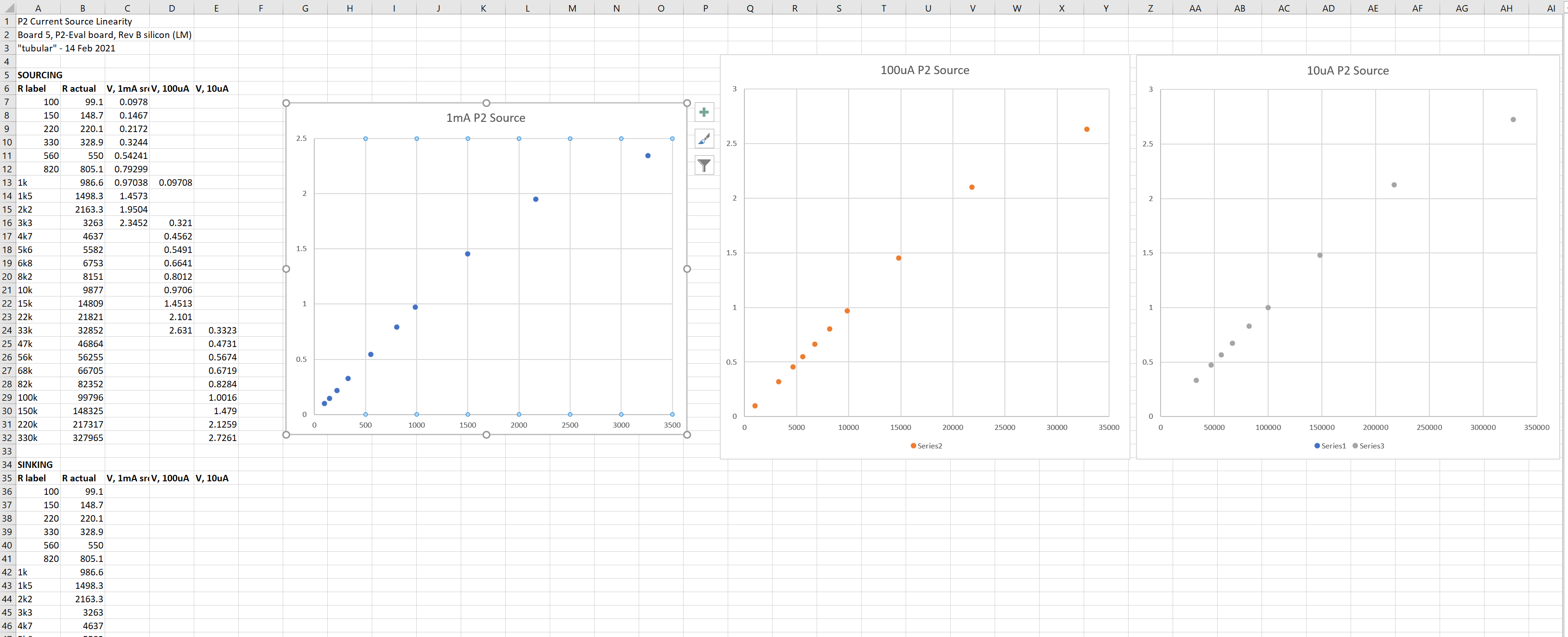

P2 Current Source Linearity

Tubular

Posts: 4,774

Tubular

Posts: 4,774

in Propeller 2

Here's some preliminary data on linearity of P2 current sources when in sinking mode.

In summary, at 2 volts the 10uA and 100uA sources are still fairly linear, while the 1mA source seems short on headroom

Comments

Would the linearity be easier to visualize if the graphs showed current (Y) vs voltage (X)? Those should produce flat lines that drop down on one side. Such graphs for the resistive drive load would show a straight line, I'd think.

Thanks for checking this out, Lachlan.

Hopefully the below approximates what you had in mind, Chip

There wasn't enough data shown for the current sinking - @Tubular, could you post raw data please?

The zipped Excel sheet is attached. It is surprisingly annoying to coax Excel not to be totally daft when it comes to charts... I swear that some decades-old DOS software like Harvard Graphics was more intelligent about this stuff.

Very nicely done thanks Kuba. Yes ill get you some more data this morning

Since P2 is basically an analog powerhouse but doesn't undergo the typical analog trim that many of the "typical" analog building blocks like op-amps and DACs go through, it may be of some advantage to make it easier for the user to do that. Of course this can all be tweaked by software calibration, but there could also be some fixed-function Verilog added to each pin to use, say, a polynomial approximation, where the user could load the coefficients if they wanted to do an in-house analog calibration; they'd default to 1,0,0,0,... on power-up. The "2nd stage" bootloader that resides on the EEPROM could be amended to load those from a table if present, and we could even make a chip calibration fixture with a ZIF socket where you could insert a P2 and an EEPROM, and the analog calibration would be done and loaded into the EEPROM at some fixed address or otherwise marked so future firmware updates would leave that alone. This could be even done today, except that there'd be no fixed-function logic to do the linearization, and instead the location, format and meaning of the calibration constants would be "by agreement" and its use would be optional. Just an idea.

Good job, Guys.

Yes, all this analog is untrimmed.

Coming up with a correction curve for the ADCs would be really cool. I really wish I had done the calibration switches differently, so it would have used a common resistor for GIO, VIO, and 1X.

@cgracey It's still pretty cool how far you got things in this "lowly crazy microcontroller" - taking it a bit further begins to really encroach on a lot of discrete analog<->digital silicon, and those are typically big-budget big-name "put together by nude greybeard wizards" operations as far as I'm concerned. I'm sure there's talent out there that can design a good CMOS ADC or DAC and a microcontroller that goes with it, but it's not all that common, I'd think. You're in a rather select club, Chip I'm sure you'll have lots of useful ideas for the next "iteration", whatever it may be. I'm already quite happy with what we got!

I'm sure you'll have lots of useful ideas for the next "iteration", whatever it may be. I'm already quite happy with what we got!

@kuba here are the corresponding 'sinking' readings, using the same resistor wheel and P2 board on same pin P0

I don't have time to do any more on this for a while, but if you can graph these then great

For these I took a couple more lower readings eg 1k5 2k2 on the 100uA and 15k 22k on the 10uA scale

Start date: 02/19/2021

Reading # Reading

1 0.143280

2 0.095446

4 0.212059

5 0.316816

6 0.529755

7 0.774731

8 0.948521

9 1.432251

10 1.961419

11 2.354391

12 0.009856

13 0.097172

14 0.147512

15 0.225672

16 0.321269

17 0.456637

18 0.549608

19 0.664797

20 0.802165

21 0.971830

22 1.454244

23 2.120321

24 2.654527

25 0.098641

26 0.147772

27 0.217568

28 0.327243

29 0.466096

30 0.558966

31 0.661981

32 0.815859

33 0.986863

34 1.457115

35 2.105272

36 2.727449

Err sorry those first two, 150R and 100R on the 1mA scale are transposed

The 1st and 4th values for 100uA look out of whack likely due to transcription/experimental error I guess.

The updated Excel file with all the data thus far is attached.

WOW! What more can I say. Well done

The Source and Sink curves are surprisingly close to the spec uA levels, I wonder how much that varies from pin to pin, and how much it varies by temperature ?

More measurement points close the knee would be useful as once you have > 1.5V across the current element, it is essentially flat.

It looks like the 1uA & 100uA would be ok for up to about 70~80% of VCC span

Ah yeah that reading 12 was on the wrong P2 dac range and should have been deleted, sorry. As for the 4th reading I don't know but will get back to it in coming days

At the moment I'm doing some urgent work with H11F1 optofets used as attenuators, here's a quick graph off the resistance-vs-P2 DAC level. As you can see there are around 5 decades of useful resistances there. The measurements quirks are likely due to the unpowered circuit the fet is hooked up to, or could be the multimeter switching ranges and not settling before the P2 commands the next reading. In any case I'm not worried about that region. The optofet starts to conduct around level 81 and is fairly "logarithmically linear) down to dac level 101, giving about 20 useful attenuation setpoints across 4 decades.

I hope to get some time to hook up the H1F11 as a programmable resistive load so that we can get finer curves and sharper knee detail. May not be this weekend though

Interesting, but could be a challenge with temperature - maybe using a pair could help there, one for feedback, and one for the load.

Ideally that would all be in one package, but I think there are no dual H11F1? Maybe SMD ones from the same tape can be next best thing ?

Hmm maybe we can switch the ADC on and measure the forward voltage of the optofets led while operating, deduce temperature from that, and adjust accordingly

To be honest the circuit its driving also has a tempco, perhaps the whole thing can be stabilised overall. Its nice to have options