Propeller 2 Update: Engineering Change Order (ECO) for A/D Performance Schedule

Ken Gracey

Posts: 7,420

Ken Gracey

Posts: 7,420

Hello Community,

Today, Parallax met with ON Semiconductor to review the improvement Chip requested to the latest silicon. I'd like to bring you current on what this means for Parallax and you, our valued community. The live development of the P2 goes with real transparency, so here it is.

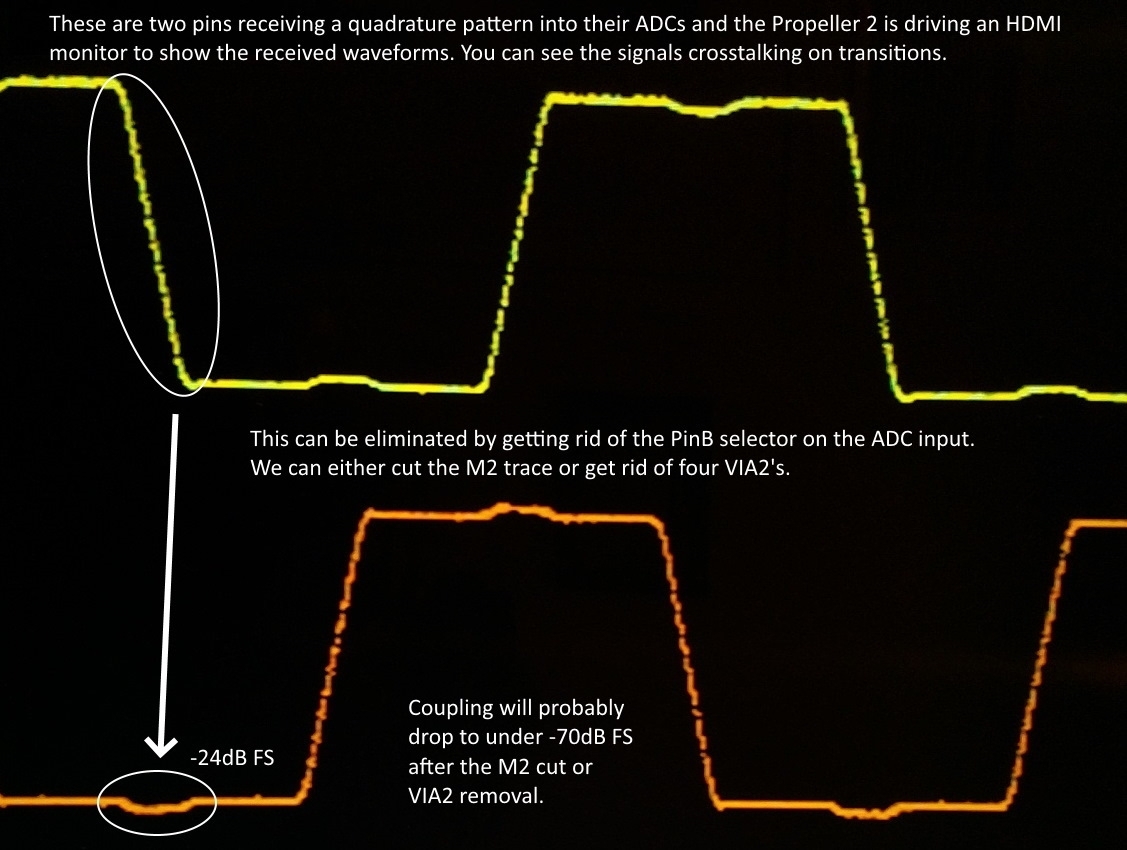

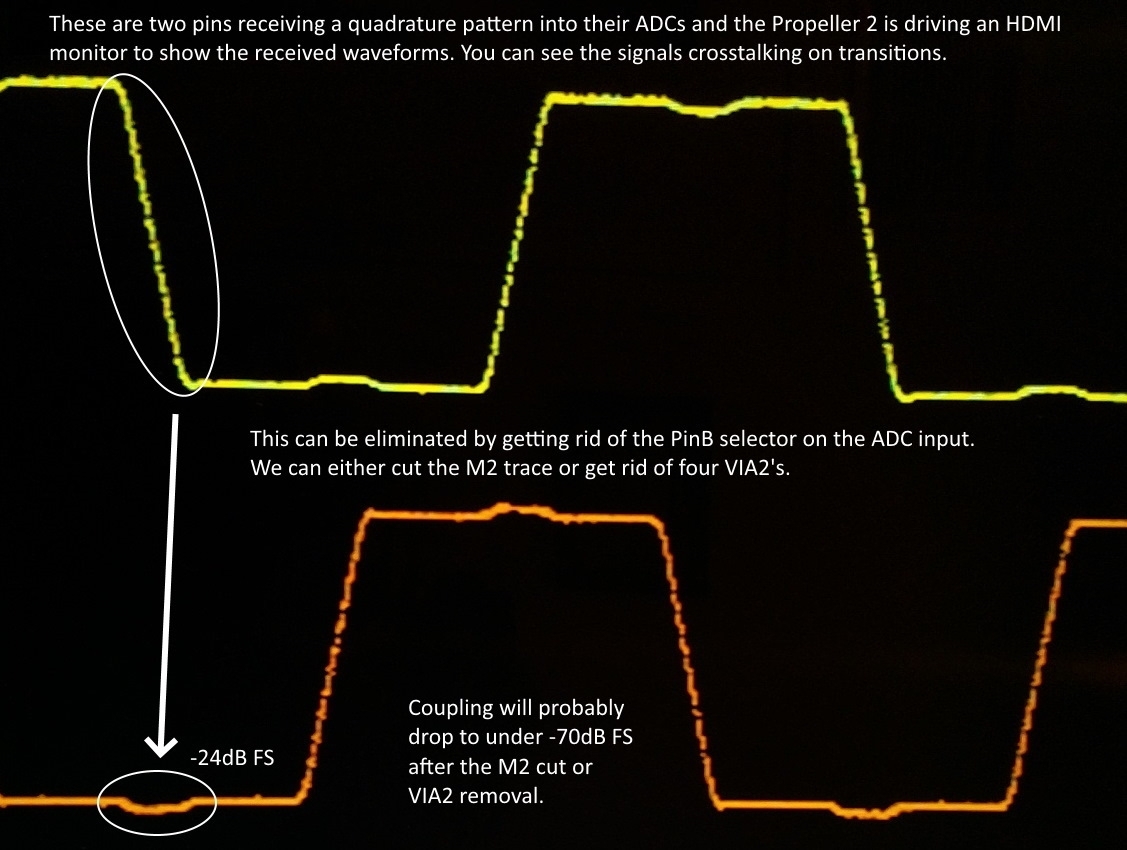

First, a bit of background on the engineering issue. I'm the business guy, so if you want real engineering details you'll need to read the many posts from Chip on the forum or whatever community replies are made below. Shortly after we approved the Revision B silicon for production Chip discovered a performance issue with the A/D where neighboring inputs were causing some capacitive coupling, reducing the resolution of the A/D to something low - like four bits instead of 14 bits. The ways around this were to couple A/D pins together, skip A/D inputs to every other pin (and ground the ones in between), or just accept slow frequency sampling. While these workarounds exist, there's also a special scope mode built into P2 hardware that uses sequential pins to generate signals. Simply cutting a trace or dropping a via on the mask set fixes this issue with 100% certainty. I understood it really well with "imagine being in a library where you were trying to study and somebody was screaming next to you". If you want to focus there's not much you can do except put the screamer in another room with two walls between you.

In today's meeting, we reviewed two courses of action. First, the current course of action called the non-ECO route which involves receiving production volumes of the P2 in April. This schedule has some parallel processes built into it, like some final packaging qualifications being done by ON Semiconductor while we order chips at-risk (read: our risk, like the chips you have, at a significant per-unit cost to Parallax). The ECO route (with the A/D improvement) starts the 22-week countdown for Rev C production parts in April, for an October release but maybe a bit earlier. It also provides us with another at-risk delivery of Rev C chips, potentially in April. ON Semiconductor has had weekly to month project management meetings with us for several years now and looks for parallel efforts whenever possible (their team is superior to all prior efforts I've been in for P2). For example, today we made a good-faith commitment to continue with the ECO and sign contracts as soon as ready. This allowed them to pull a few in-process wafers planned for the packaging qualification and modify them for the A/D trace cut pretty easily.

Bottom line: Rev C P2 silicon nearly certain by April, production parts planned by October 2020. We are proceeding with the ECO. You, Parallax and ON are *all in*. The ECO comes at a significant engineering cost (much more than discussed here) and with a longer timeline and more at-risk purchases. But it's clear: we've got to do this! Simply hearing Chip describe the issue is enough; no marketing hogwash or datasheet nonsense can bury this performance issue.

We will rely heavily on the community to help us bring this to market, as we don't have the resources internally (we're down to a team of 20). Your numerous contributions are more important than ever. Chip is now working to complete Spin2 so a wider number of users can get started. Some of our team was working on P2 projects but I am turning their attention back towards educational customers (teacher workshops, educational support, robotics, software improvements, some new products). Parallax is still making some internal efforts to plan for the P2, like moving OBEX to GitHub and making a complete repository where your work can be hosted, making a simple P2 web site from propeller.parallax.com and keeping the parts moving into your hands. We'll also plan a P2 module when we see that the Rev C silicon is well underway.

Customers should certainly get started with their current P2 chips. They'll run the same code, speed and memory! Believe in what we're doing at Parallax and you'll have production chips by the time you finish your coding and PCB.

Thanks,

Ken Gracey

Today, Parallax met with ON Semiconductor to review the improvement Chip requested to the latest silicon. I'd like to bring you current on what this means for Parallax and you, our valued community. The live development of the P2 goes with real transparency, so here it is.

First, a bit of background on the engineering issue. I'm the business guy, so if you want real engineering details you'll need to read the many posts from Chip on the forum or whatever community replies are made below. Shortly after we approved the Revision B silicon for production Chip discovered a performance issue with the A/D where neighboring inputs were causing some capacitive coupling, reducing the resolution of the A/D to something low - like four bits instead of 14 bits. The ways around this were to couple A/D pins together, skip A/D inputs to every other pin (and ground the ones in between), or just accept slow frequency sampling. While these workarounds exist, there's also a special scope mode built into P2 hardware that uses sequential pins to generate signals. Simply cutting a trace or dropping a via on the mask set fixes this issue with 100% certainty. I understood it really well with "imagine being in a library where you were trying to study and somebody was screaming next to you". If you want to focus there's not much you can do except put the screamer in another room with two walls between you.

In today's meeting, we reviewed two courses of action. First, the current course of action called the non-ECO route which involves receiving production volumes of the P2 in April. This schedule has some parallel processes built into it, like some final packaging qualifications being done by ON Semiconductor while we order chips at-risk (read: our risk, like the chips you have, at a significant per-unit cost to Parallax). The ECO route (with the A/D improvement) starts the 22-week countdown for Rev C production parts in April, for an October release but maybe a bit earlier. It also provides us with another at-risk delivery of Rev C chips, potentially in April. ON Semiconductor has had weekly to month project management meetings with us for several years now and looks for parallel efforts whenever possible (their team is superior to all prior efforts I've been in for P2). For example, today we made a good-faith commitment to continue with the ECO and sign contracts as soon as ready. This allowed them to pull a few in-process wafers planned for the packaging qualification and modify them for the A/D trace cut pretty easily.

Bottom line: Rev C P2 silicon nearly certain by April, production parts planned by October 2020. We are proceeding with the ECO. You, Parallax and ON are *all in*. The ECO comes at a significant engineering cost (much more than discussed here) and with a longer timeline and more at-risk purchases. But it's clear: we've got to do this! Simply hearing Chip describe the issue is enough; no marketing hogwash or datasheet nonsense can bury this performance issue.

We will rely heavily on the community to help us bring this to market, as we don't have the resources internally (we're down to a team of 20). Your numerous contributions are more important than ever. Chip is now working to complete Spin2 so a wider number of users can get started. Some of our team was working on P2 projects but I am turning their attention back towards educational customers (teacher workshops, educational support, robotics, software improvements, some new products). Parallax is still making some internal efforts to plan for the P2, like moving OBEX to GitHub and making a complete repository where your work can be hosted, making a simple P2 web site from propeller.parallax.com and keeping the parts moving into your hands. We'll also plan a P2 module when we see that the Rev C silicon is well underway.

Customers should certainly get started with their current P2 chips. They'll run the same code, speed and memory! Believe in what we're doing at Parallax and you'll have production chips by the time you finish your coding and PCB.

Thanks,

Ken Gracey

Comments

It will be good to have this fixed.

How many April delivery parts ?

Hear Ye, Hear Ye!

That's the spirit! Board the spaceship!

Thanks,

Ken Gracey

Probably 1K units.

Ken Gracey

Does this mean the expo is delayed also?

Yes.

Ken Gracey

One in particular would be fixing the PLL clock source select de-glitch circuit.

No. We unloaded the FIB machine several years ago. It was expensive to maintain and we were years away from needing it.

This change is so trivial that it's not even worth trying at any likely expense using existing chips. We need new wafers without the PinB connection into the ADC resistor array. That will solve the problem.

It just takes more money and time now. It's funny to think how I could have made that edit in one minute back when I was working on the layout, but I had no idea.

Otherwise at 1000 it's just vaporware. We had momentum on those rev B boards, which if allowed to fizzle we're all done here. No variants in the P2 family. What if the 64 i/o chip can only do 32 analog in? Still impressive.

It's like, the way it was presented, just $5K and a simple low risk change, and still April. And now massive expense and October 2020? Good grief.

It's like the story where the contact margin bought the work truck, but the change orders bought the yacht and trailer being towed. I think despite how "nice" it's still gouging, like an eccentric millionaire using their life savings to build the "perfect " mansion.

It's going to cost $25k to fix this. We can order more parts, but our unit cost is 2x normal pricing.

If someone wants more chips, we can get them, if we know, but I think it will realistically take people 6 months to a year to have their first products designed, so that they will need any volume.

In the meantime, we can support development efforts with probably little difference than if we had infinite chips to sell.

I had thought it was only going to cost around $5K and no delay

But it is what it is.

That would cost a lot to address, like maybe $60k, and it would take extra months. Even adding the guard rings around the offending N-wells would cost $60k.

Although I want (need) the P2 to be released for business reasons. I fully understand and support this change.

I have an existing design that uses the P1 and I am making great progress in converting it to the P2 with much better specs.

I don't know if it is possible, but I would be willing to buy some more of the Rev B chips at the $25 price.

Bean

For that reason, it probably makes sense to get it right.

However, to me, it seems like Parallax went forward too fast with the production order.

Personally, I would have waited even a bit longer than now for that...

I just can't believe that everything has been tested yet.

On the other hand, everything that I care about seems to work...

EDIT2: Chip's original hope was to insert the change without any samples being made. On Semi have obviously said a clear no to that idea.

If we can continue to get a dribble of P2 Rev B silicon for dev purposes, this delay wont be that painful for me. Product development efforts can continue, and about the time the Rev C chips hit, I’ll be ready for them. And in the meantime, those all-important reference docs can get some attention, and the toolsets can progress further towards maturity.

IMHO, Parallax is making a tough but correct choice here.

Bean

Go, go, go! April will be here before you know it.

Hello Ken,

could you please explain theese workarounds a bit more? The coupling is capacitive, so if I understand correctly there is no DC error. And if I have enough spare pins I could ground every second pin between the ADC inputs and the error could be neglected?

For example, if I drive a motor with a PWM power stage and measure the winding current with hall current sensors and if I sample the analogue voltage over a complete PWM cycle then all capacitively coupled errors should be cancelled out, right?

I'm currently designing a new product and I have to decide if I give the P2 another chance or not. Waiting until Oct 2020 is a no-go. I can live with some restrictions as long as there are workarounds. But I'd need engineering samples ASAP and at least small production volume (~100 units) the next 1/2 year.