P2 (circa 2013) versus 1st working silicon

in Propeller 2

Interesting to compare where we are now versus 6 years ago...

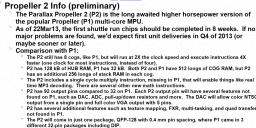

Here's what I wrote on my website about P2 way back then (attached image).

We blew past the 2X clock speed, but at 2 clocks per instruction instead of 1. Guess this evens out.

Got way more RAM, 512 kB versus 128 kB.

256 longs of "stack" RAM became 512 longs of "LUT" RAM.

#pins reduced from 92 to 64, but now they are "smart", so maybe that's OK.

Think we have texture mapping and FXR, I don't remember what that is.

Think we lost explicit multi-tasking, but have interrupts, so maybe that's the same.

I also forgot what "quad-transfer" was, but now we have the streamer, which I think is better.

The QFP-100 package may be slightly easier to deal with that the 0.4 mm spaced QFP-128.

Here's what I wrote on my website about P2 way back then (attached image).

We blew past the 2X clock speed, but at 2 clocks per instruction instead of 1. Guess this evens out.

Got way more RAM, 512 kB versus 128 kB.

256 longs of "stack" RAM became 512 longs of "LUT" RAM.

#pins reduced from 92 to 64, but now they are "smart", so maybe that's OK.

Think we have texture mapping and FXR, I don't remember what that is.

Think we lost explicit multi-tasking, but have interrupts, so maybe that's the same.

I also forgot what "quad-transfer" was, but now we have the streamer, which I think is better.

The QFP-100 package may be slightly easier to deal with that the 0.4 mm spaced QFP-128.

Comments