VESA Coordinated Video Timing Generator (CVT)

Tubular

Posts: 4,774

Tubular

Posts: 4,774

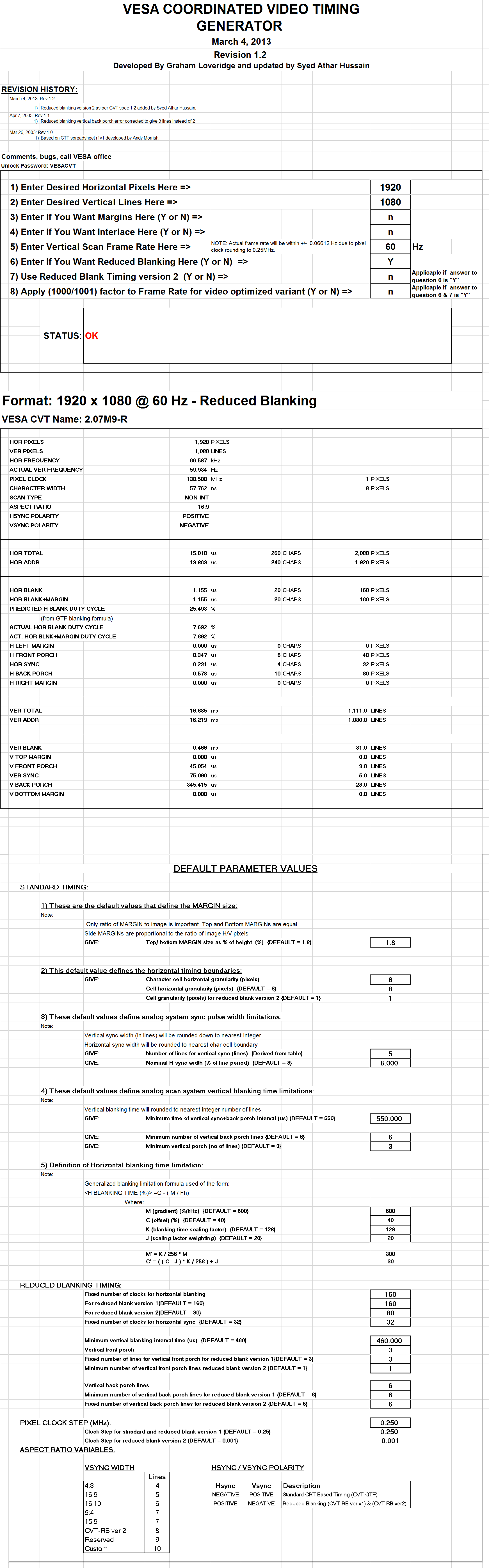

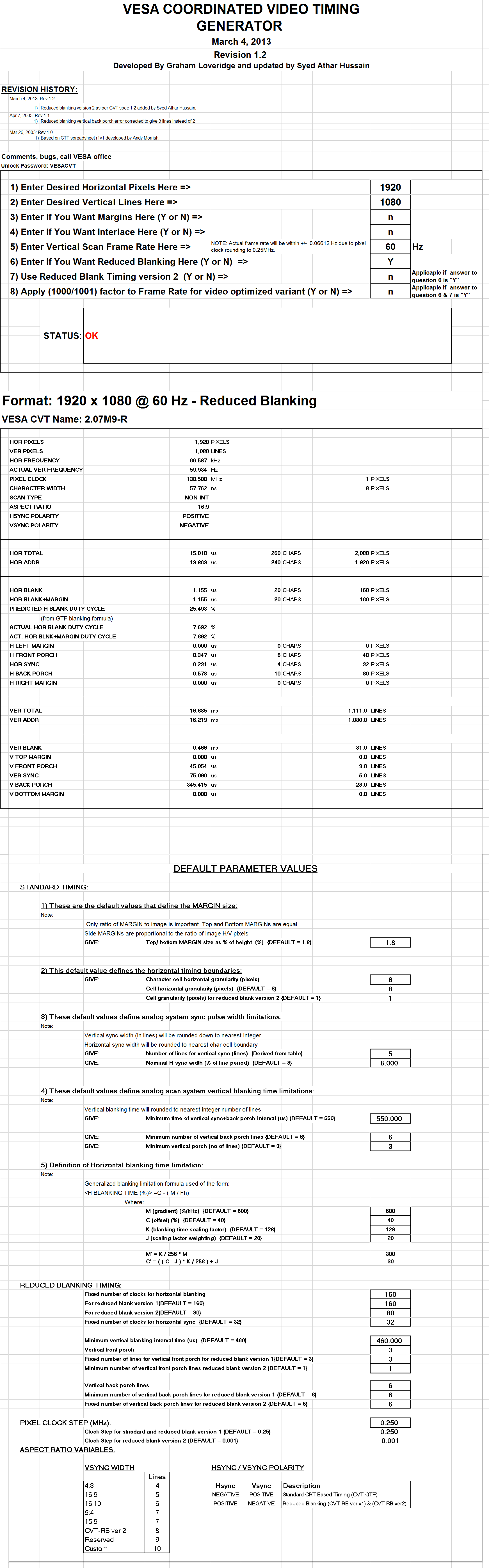

This is the video timing generator I use for finding suitable reduced blanking settings for P2. CVT spreadsheet is a free download from VESA.org, but you need to supply an email address to download.

The reduced blanking means we can run lower dot clocks, have less power consumption and less self heating. RB comes in 2 versions

1. RB Version 1 came out around 2003 I believe, drops the dot clock around 20% compared to no reduced blanking.

2. RB Version 2 came out around 2013 I believe, drops the dot clock around 24% compared to no reduced blanking.

For HD 1920x1080 60p, instead of 182.5 MHz the dot clocks become 138.5 (v1 RB) or 133.187 (v2 RB), with corresponding enery savings. In my opinion v1 is the one to use for now, because there are plenty of pre-2013 monitors still around

To modify, change the answers to questions 6,7,8 in the spreadsheet at the top

I think there is an error in bottom right corner where it talks about sync polarity. I believe H sync should be positive, regardless, but I need to find the other vesa document where I saw this information Its consistent with pdf description (download from same source as spreadsheet). However P2 is currently sending positive HSync by default.

The reduced blanking means we can run lower dot clocks, have less power consumption and less self heating. RB comes in 2 versions

1. RB Version 1 came out around 2003 I believe, drops the dot clock around 20% compared to no reduced blanking.

2. RB Version 2 came out around 2013 I believe, drops the dot clock around 24% compared to no reduced blanking.

For HD 1920x1080 60p, instead of 182.5 MHz the dot clocks become 138.5 (v1 RB) or 133.187 (v2 RB), with corresponding enery savings. In my opinion v1 is the one to use for now, because there are plenty of pre-2013 monitors still around

To modify, change the answers to questions 6,7,8 in the spreadsheet at the top

I think there is an error in bottom right corner where it talks about sync polarity. I believe H sync should be positive, regardless, but I need to find the other vesa document where I saw this information Its consistent with pdf description (download from same source as spreadsheet). However P2 is currently sending positive HSync by default.

Comments

Very cool! I had no idea people were optimizing blanking to take advantage of not having a CRT in the mix!

Yes it's how the higher resolutions fit within the 165MHz DVI limit. Eg. 24 inch Dell 2405fpw can hit 1920x1200 60Hz over a single link DVI even though that would normally have required over 165MHz pixel clock in the original analog VGA world before reduced blanking came in.

These PLL wobbles we're seeing on VGA may be a complete non issue if we output a dot clock for LCDs, or HDMI or whatever.

Did you have a read of the CVT v1.2.pdf doc?

Rogloh has access to a fancy Sony analog CRT monitor that we'll give a try soon. No reduced blanking there, think it'll need a 267 MHz clock

I've got a SONY PVM that does all the 15Khz stuff, RGB, TTL RGBi, S-video, composite. Actually just looked, and that one does not do component. I've another one, a bit more crappy for that.

My other CRT is a VGA type one, not as nice as the Sony probably is, but it's good for ~1600 x ~1280. Some COMPAQ branded screen. I should open it up and find out who made it.

Reading the CVT doc now.

Here were some of the key specs from my old Sony monitor, not that fancy but it was capable of displaying 2048x1536 at 60Hz back in the day IIRC. It's horizontal scan maxes out at 130kHz which will be a limiting factor in the testing. Pixels at that resolution will be small and below the aperture grill pitch size, which may limit identifying small amounts of jitter, but still probably worth trying.

Full specs...

http://www.keithmay.org/equipment/Sony_CPD-G520/Sony_CPD-G520_Spec_sheet.pdf

If the test pattern is vertical bars of some pixels wide, the finite-rise edges can hit any fraction of a phosphor dot they like, and jitter should show as brightness modulation.

Do you know how the monitors extract/lock to these varying dot clocks ?

If they are as MHz tolerant as that range suggests, there may be multiple VCO choices ?

I had noticed that the H Porches could be trimmed significantly but no idea there was a standard. I still don't understand why we need them at all these days. A single VS should only be required, and a single HS for each line should only be necessary, or even a combined VS + HS single wire - there was a composite VS & HS but it ever took off

When I am back home I'll give these settings a go

Most of the good recent info I've learned came from the CVT v1.2.pdf doc accompanying the spreadsheet. It also goes into the naming of the modes - I've seen some monitors list these names eg "2.07MA" etc.

The monitors themselves seem to lock onto a pretty wide range, and I've also seen them track a wandering PLL quite effectively (enough to fool the viewer, until eventually and 'autoadjust' takes place). In the doc there is discussion about a 0.25MHz Pixel Clock Step, though.

I read somewhere that in most cases, monitors internally XOR HS & VS, and you can use a single wire. Easy enough to try.... ?

Yes definitely give them a go

I think also we can create our own modes, to suit available hub memory

I'm inverting VSync nowadays to signal the reduced blanking. Hsync seems to already be 'positive'. This seems to be the way to go.

I've noticed some of the monitors take quite some time to lock onto the video settings, and perhaps getting everything lined up with the VESA CVT RB specs will help.

Great find. Must read doc, IMHO.