P2_Eval Crystal Startup and Capacitance setting tests

Switching from RCFAST (~ 23MHz) to Xtal (20.000MHz) is tested, and the Xtal Cap settings also tested

Xtal: TSX-3225 20.0000MF20G-AC3 EPSON CRYSTAL 20.0000MHZ 9PF SMD 20MHz ±20ppm ±10ppm 9pF 60 Ohms

Docs have

HUBSET ##%0000_000E_DDDD_DDMM_MMMM_MMMM_PPPP_CCSS 'set clock mode

CC Xtal pins mode

SS Osc Select : RCFAST : RCSLOW : XI : PLL

Taqoz test script, to Enable PWM, then switch clock sources (after this a reset is needed to recover TAQOZ & autobaud).

Tests confirm switching without any delay is not reliable.

it may be that before the Xtal amplitude is large enough, that noise/illegal clock widths can come from Xtal Osc.

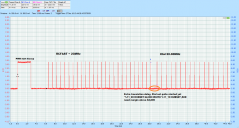

Scope image shows the boundary/marginal case, were the starting delay is too small (2.7ms here at 62,000) and the Xtal has not fully started - there is visible a longer delay, as the clock source handover occurs.

When the WAITX is sufficiently large, there is no extra delay, as the switch over is done in 1 SysCLK.

Xtal oscillates in all 3 Cap modes, even minimum C, and the %10 mode has < 10ppm error.

TAQOZ PWM has a couple of issues :

a) It generates a wide initial pulse, before the user pulses appear after ~ 6ms

b) It seems to be off-by-2, ie the output numbers, are half the sysCLK - is that a Smart Pin bug, or a TAQOZ bug ?]

... Ahh, buried far away from the PWM examples, is mention of SAW, (no examples) & some trials reveals

'16 PIN 200 10000 1 SAW',$0D

removes the unexpected 2x error & also changes the pulse hiccups.

In SAW mode, the 2.6ms HI is still present, but there is much less delay in the pulse train repeats, after the falling edge. Prr of 433us has first low of 442us

Looks like the TAQOZ docs need some corrections & clarifications on actual SysCLK cycle counts and modes.

Changed to 160MHz to look for jitter, and also measured ppm temperature effects

160MHz is SAWtooth /10k of

1-16k/15999.836 = -10.250ppm

Then change to 20MHz Xtal, and measure over next 5 mins

1-1k/999.9900 = -10.000ppm

1-1k/999.9908 = -9.200ppm

1-1k/999.9913 = -8.700ppm

1-1k/999.9922 = -7.800ppm ....cooling down,

Xtal: TSX-3225 20.0000MF20G-AC3 EPSON CRYSTAL 20.0000MHZ 9PF SMD 20MHz ±20ppm ±10ppm 9pF 60 Ohms

Docs have

HUBSET ##%0000_000E_DDDD_DDMM_MMMM_MMMM_PPPP_CCSS 'set clock mode

CC Xtal pins mode

SS Osc Select : RCFAST : RCSLOW : XI : PLL

%CC XI status XO status XI/XO Z XI/XO caps Measures ppm change %00 ignored float Hi-Z OFF %01 input 600-ohm drive 1M-ohm OFF -> 1000.1439Hz +144 ppm %10 input 600-ohm drive 1M-ohm 15pF per pin -> 999.9933Hz -6.700 ppm << operating point. %11 input 600-ohm drive 1M-ohm 30pF per pin -> 999.9472Hz -53 ppm %SS Clock Source Notes %11 PLL CC != %00 and E=1, allow 10ms for crystal+PLL to stabilize before switching to PLL %10 XI CC != %00, allow 5ms for crystal to stabilize before switching to XI %01 ~20kHz ~20kHz, can be switched to at any time, low-power %00 20MHz+ 20MHz+, can be switched to at any time, used on boot-up.

Taqoz test script, to Enable PWM, then switch clock sources (after this a reset is needed to recover TAQOZ & autobaud).

Tests confirm switching without any delay is not reliable.

it may be that before the Xtal amplitude is large enough, that noise/illegal clock widths can come from Xtal Osc.

// Reset target '> '[esc] enables TAQOZ $3E,$20,$1B // wait appx 250ms needed, for TAQOZ to load '16 PIN 200 10000 1 PWM',$0D // wait ~5ms for ok echo, // Then Enable Xtal Osc, VAR delay for Osc Start, and switch to Xtal source. '%11_00 HUBSET 62,000 WAITX %11_10 HUBSET',$0D

Scope image shows the boundary/marginal case, were the starting delay is too small (2.7ms here at 62,000) and the Xtal has not fully started - there is visible a longer delay, as the clock source handover occurs.

When the WAITX is sufficiently large, there is no extra delay, as the switch over is done in 1 SysCLK.

Xtal oscillates in all 3 Cap modes, even minimum C, and the %10 mode has < 10ppm error.

TAQOZ PWM has a couple of issues :

a) It generates a wide initial pulse, before the user pulses appear after ~ 6ms

b) It seems to be off-by-2, ie the output numbers, are half the sysCLK - is that a Smart Pin bug, or a TAQOZ bug ?]

... Ahh, buried far away from the PWM examples, is mention of SAW, (no examples) & some trials reveals

'16 PIN 200 10000 1 SAW',$0D

removes the unexpected 2x error & also changes the pulse hiccups.

In SAW mode, the 2.6ms HI is still present, but there is much less delay in the pulse train repeats, after the falling edge. Prr of 433us has first low of 442us

Looks like the TAQOZ docs need some corrections & clarifications on actual SysCLK cycle counts and modes.

Changed to 160MHz to look for jitter, and also measured ppm temperature effects

160MHz is SAWtooth /10k of

1-16k/15999.836 = -10.250ppm

Then change to 20MHz Xtal, and measure over next 5 mins

1-1k/999.9900 = -10.000ppm

1-1k/999.9908 = -9.200ppm

1-1k/999.9913 = -8.700ppm

1-1k/999.9922 = -7.800ppm ....cooling down,

Comments

Now I am really wondering something. You are like a perpetual volcano of questions. Now that you've got a P2 board, you are going to start answering a lot of your own questions. This will probably elicit lots of other questions which you will get answers to. What I am wondering about is whether this whole process is going to be exothermic or endothermic. You could be on your way to supernova or neutron star.

Jmg armed and dangerous

I hope neither

My scope seems not quite good enough to catch the jitter, is has a bug in large +ve offsets, and I suspect large -ve offsets might not be all they claim either...

An initial state I am ok with, it is the 2.9ms HI then 3.5ms low I was not expecting, as well as the mysterious off by 2 effect. Hopefully, that is not in the pin ?

ie the asked for clocks, seem to be 2x time expected from sysCLK value ?

This is where the real fun is.

I am in a position to make measurements, the best answers will come from the TAQOZ author, as the issue is either in TAQOZ, or in the pin itself (hopefully not).

I can see 2 PWM modes, maybe TAQOZ chose the triangle PWM, not the sawtooth PWM ? - the docs are unclear on that detail.

Addit : see updated #1 post - as suspected, PWM uses triangle, and there is another keyword, SAW, that must be used to give sysclk correct results.

This is the current ROM code for PWM which you can see happens to be the triangle waveform,whether that's a good thing or not, it is what I initially used to play with PWM. Feel free to rearrange these words or just interact with the smartpin word by word ;

BTW, The PWM word falls through to the next word PWM1 which just happens to be a common routine for both PWM and SAW. Even though SAW "calls" PWM1 the actual compiled code executes this as a fast jump so that there is no need for a return or an EXIT

+1

This is the first thing I do, after starting TAQOZ and waiting 250ms

'32 PIN 200 10000 1 PWM',$0D

pulse start is the same = 2.8ms wide hi, then first pulse is at 6.56ms

'32 PIN 200 10000 1 SAW',$0D

has the same 2.8ms hi, and then pulses start from there (no trailing wide low)

32 PIN 100 1000 1 PWM has faster pulses, and that indicates the trailing low is until 5.773 ms