Switching from 20kHz RCSLOW to XTAL1@5MHz or RCFAST

Tracy Allen

Posts: 6,667

Tracy Allen

Posts: 6,667

I didn't want to hijack John's thread about generating 38kHz for an LED.

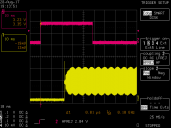

The following program alternates between RCSLOW and XTAL1 5MHz in a loop with about 1 second in each phase. Pin p3 is an indicator and trigger for the 'scope image attached, p3 is in red, and the 5MHz crystal output XO is in yellow. P3 goes high just before it enables the oscillator, and it goes low again once the Prop is operating at 5MHz. It happens that there is a 22ms delay before the first kick to the xtal, and then there is another 22+ ms delay before the chip switches over to operate at 5MHz. The crystal ramps up to speed in well under 10 ms. If you take out the two clkset instructions, the pair of outa[3] instructions generate an pulse of less than 1ms duration. So my question is, why do the two clkset instructions take so long?

The following program alternates between RCSLOW and XTAL1 5MHz in a loop with about 1 second in each phase. Pin p3 is an indicator and trigger for the 'scope image attached, p3 is in red, and the 5MHz crystal output XO is in yellow. P3 goes high just before it enables the oscillator, and it goes low again once the Prop is operating at 5MHz. It happens that there is a 22ms delay before the first kick to the xtal, and then there is another 22+ ms delay before the chip switches over to operate at 5MHz. The crystal ramps up to speed in well under 10 ms. If you take out the two clkset instructions, the pair of outa[3] instructions generate an pulse of less than 1ms duration. So my question is, why do the two clkset instructions take so long?

CON

_clkmode = RCSLOW

'

PUB main

dira := $ffff ' all pins are outputs

outa := $3000 ' all pins except 28,29 (scl,sda) are low

ctra := %00100<<26 ' NCO on p0

frqa := 32641751 ' 26.315us, 38.000.85 kHz o=.1us

'

repeat

waitcnt(clkfreq+cnt)

outa[3]~~ . ' pin p3 goes high to trigger 'scope

clkset(%0_01_01_001, 20_000) ' xtal 5MHz oscillator on, no PLL, still operating on RCslow

' no additional delay needed here in Spin '

clkset(%0_01_01_010, 5_000_000) ' switch to operate on 5MHz xtal, no PLL

outa[3]~

waitcnt(clkfreq+cnt) . ' one second generating 38kHz.

clkset(%0_00_00_001, 20_000) ' drop to RCSLOW at ~20 KHz

Comments

Have you tried the equivalent in pasm? Just curious, to definitively narrow down whether it's the nature of the prop or if it's pasm vs spin. I don't have the prop manual/datasheet in front of me so dunno - clkset by its very nature doesn't take a longer time than other instructions does it?

Cheers,

Jesse

I do think I'll try the pasm version when I get to the shop. On the surface, as a Spin hub instruction, it only has to read in the two parameters and use those to update the clkfreq long at location 0 and the clock mode byte at location 4. The manual says there is an obligatory ~75 microsecond delay any time the clock mode register is written. I recall reading somewhere in the forum that the changeover of clock source is always somehow synced by the 20kHz clock source (~50 microsecond period).

When you try PASM, can you check Slow <-> Fast RC osc changes, to see if the ~22ms is just on Xtal entry, or all mode changes ?

Program attached.

0.82ms from pin high to first kick to crystal. Yellow trace is xtal XO.

2.55ms from there to p3 high. Part of that is a programmed delay of 32 clock cycles at 20kHz.

The green trace, channel 4, shows the p0 output from a cog counter running at maximum frequency.

The orange trace, time zoomed, shows the 10kHz ctra output followed by the sync into 2.5 MHz, with cycles dropped at the points where the clkset instruction is executed.

The transition code:

832 microseconds in pasm

33 milliseconds in spin

The third 'scope shot is simply pin p3 going high and low in pasm with two outa[] instructions. 4 clock cycles, compared with 17 clock cycles for the first 'scope shot, which includes the clkset instruction. So the clkset instruction is adding 13 clock cycles, consistent with a hub instruction in a longer loop.

32/20k = 1.6ms, so this could reduce with a resonator, to 0.82ms + ~0.1ms Resonator start time ?

I wonder is there any way to measure/calibrate the RCSlow and RCFast, from the Xtal ?

AFAIK there is no way to measure/calibrate RCSLOW or RCFAST from the Xtal. That would be nice. Tricks? I usually have an RTC with a 1pps heartbeat attached, so serves as calibration reference.

The resonator should start inside that 400us, and a NOP could always be added if scope says not-quite.

I wonder if you can run a counter via PLL (max or min limit ?) and read that 3 ways ?

This would assume the PLL does not change between modes.

-Phil