Operation of Counter/PLL

in Propeller 1

Hey all. I'm attempting to generate a VGA video signal via Counter A in PLL mode. I just want to verify that I'm understanding the operation of this thing:

1. Load FRQA with a value which will be added to PHSA, where the MSB (bit 31) of PHSA is used as the clock input for the PLL in such a way that:

2. Load CTRA with the appropriate CTRMODE and PLLDIV to start the counter in video PLL internal (video mode).

Also, I understand that if FRQ1 isn't a power of 2 then there will be jitter inherent in PLL_in. But I also understand that the PLL is supposed to remove these jitters?

So, for example, with a target PLL_in of 8 MHz to achieve a maximum PLL_out:

@ CLK_FREQ = 80 MHz,

PLL_in = 8 MHz = (FRQA * 80 MHz)/(2^32) => FRQA = 429496730

Therefore, PLL_out = 16 * (1/1) *[(429496730 * 80 MHz)/(2 ^ 32) => PLL_out = 128 MHz

Where, PLLDIV = %111 = VCO/1

And this result, 128 MHz is the fastest possible clock output of the PLL, and therefore the fastest possible pixel clock rate when used by the video generator, correct?

Thank you for the help!

1. Load FRQA with a value which will be added to PHSA, where the MSB (bit 31) of PHSA is used as the clock input for the PLL in such a way that:

a. PLL_in = (FRQA * CLK_FREQ)/(2^32) where CLK_FREQ will be 80 MHz and 4 MHz <= PLL_in <= 8 MHz

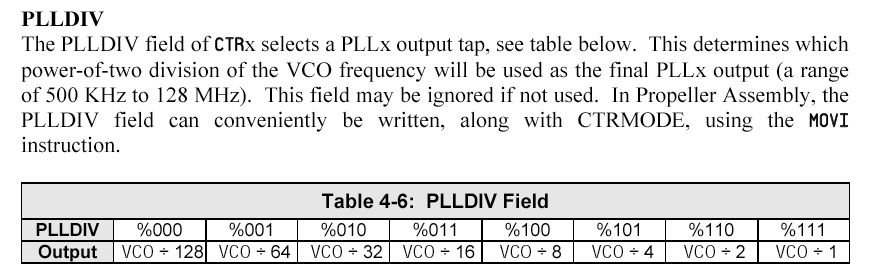

b. PLL_out = 16 * PLLDIV * [(FRQA * CLK_FREQ)/(2^32)], where PLLDIV is one of the dividers from the following table...

2. Load CTRA with the appropriate CTRMODE and PLLDIV to start the counter in video PLL internal (video mode).

Also, I understand that if FRQ1 isn't a power of 2 then there will be jitter inherent in PLL_in. But I also understand that the PLL is supposed to remove these jitters?

So, for example, with a target PLL_in of 8 MHz to achieve a maximum PLL_out:

@ CLK_FREQ = 80 MHz,

PLL_in = 8 MHz = (FRQA * 80 MHz)/(2^32) => FRQA = 429496730

Therefore, PLL_out = 16 * (1/1) *[(429496730 * 80 MHz)/(2 ^ 32) => PLL_out = 128 MHz

Where, PLLDIV = %111 = VCO/1

And this result, 128 MHz is the fastest possible clock output of the PLL, and therefore the fastest possible pixel clock rate when used by the video generator, correct?

Thank you for the help!

Comments

The PLL does some smoothing, but not as much as I would like. It does cause issues with TV broadcast mode. I've never done VGA with the Propeller so I don't know how much VGA monitors are affected by jitter.

Generally the output is fairly clean with the rule:

FRQx=(2^32)/(N/M) where M is a small number, maybe 1-3 is a good range

For example, N=32, M=3

80/(32/3) = 7.5 MHz

7.5MHz * 16 = 120 MHz VCO freq

FRQx=402653184

I haven't tested this value recently to know how clean the signal is.

128MHz would be a good limit for production systems. For experiments, go ahead and overclock it.