Bypass capacitors for the P8X32A-Q44

Hi everyone,

I am porting a multi-prop project to a board using the 44 pin P8X32A-Q44.

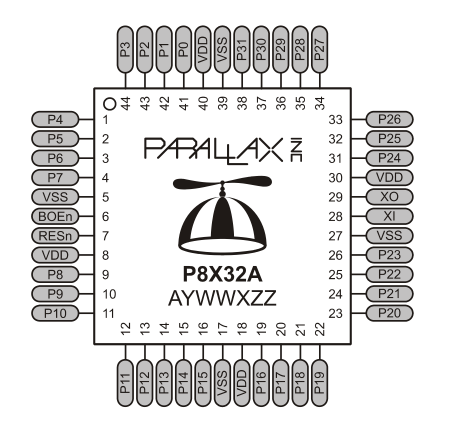

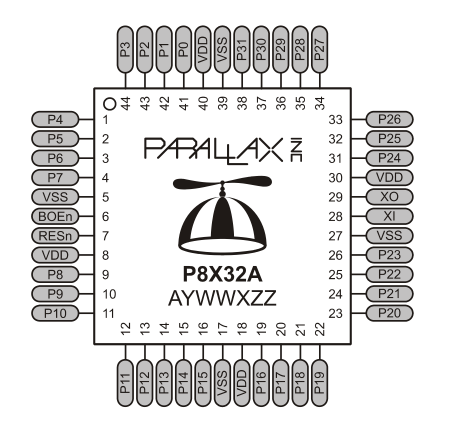

It has a VDD and a VSS on each of the four sides.

This seems to be an opportunity to maximize bypass capacitors.

The thought of putting four equal ones on each side seems appealing, but they might be "in parallel," and in addition to this the Propeller Demo Board and other boards only use one bypass capacitor.

My question is whether it would be advantageous to add a second (or third or fourth) bypass capacitor of a different value?

For example, pins 8 and 5 (of the 44) could have a 1uF and pins 40 and 39 could have a 0.1uF...or any combination on the four sides.

What is the very best that can be done?

I appreciate the input !!

I am porting a multi-prop project to a board using the 44 pin P8X32A-Q44.

It has a VDD and a VSS on each of the four sides.

This seems to be an opportunity to maximize bypass capacitors.

The thought of putting four equal ones on each side seems appealing, but they might be "in parallel," and in addition to this the Propeller Demo Board and other boards only use one bypass capacitor.

My question is whether it would be advantageous to add a second (or third or fourth) bypass capacitor of a different value?

For example, pins 8 and 5 (of the 44) could have a 1uF and pins 40 and 39 could have a 0.1uF...or any combination on the four sides.

What is the very best that can be done?

I appreciate the input !!

Comments

-Phil

Yes, it is always best to add decoupling capacitors to EVERY VSS, VDD connection on the Prop.

It does away with PLL failures.

EDIT: Again Phil types faster than I do.

I'm using Diptrace and manually placing the bypass capacitors as close to the pins as possible.

Using the "auto placement" does not always do this little perfection.

I imagine that one should favour a close + positive over a close - negative...

At other times, when capacitors are filtering noise, it is beneficial to have a sweep of values.

Do you think this is worth the effort? Just use bigger values exclusively?

I am trying to create a pretty nastily little multi-prop...

Here's a board I'm working on for a friend. the caps and resistors are 0805s to facilitate building by hand.

Very nice !! One could say even inspiring!

The philosophers ascribe beauty to proportion...

BTW I am now using 0603 0.1uF caps and i find they are easy to hand solder - just make the pads extend out a bit further and a little wider. I put them on my extended 0805 pads but they are a bit too big and not quite close enough between the centers.

I use a 4x10K resistor pack for SDL, SCK, RESET and WP pullups.

I yu use the ssop fine pitch eeprom, make sure you extend the pads out for hand soldering.

-Phil

If my regulator only supplies the prop then my regulator is next to the prop and the 10uF can be shared for the regulator and prop.

If the regulator supplies more than the prop, then the regulator will have its own 10uF, the prop will have its own 10uF, and if you use an SD/microSD it also requires its own 10uF plus 0.1uF.

My ground plane on the top under the prop extends at the 4 corners to meet the underneath ground plane outside the prop using 4 vias. The power plane under the prop feeds each of the 4 0.1uF caps and then feeds vias which go to the prop solder pads. This makes each 0.1uF cap actually as close to each power and ground pad as possible, and each 0.1uF is really providing that power/ground pin set.

Note the use of X7R capacitors. Z5U are much lower spec, yet there is almost no difference in price. For 10uF use tantalum or you can use 10uF X7R but not Z5U.

Just want to say: this is my first post and look at the fantastic and helpful discussion.

Love it. Thanks.

Massimo

But you've neglected to use wide traces to the decoupling capacitors

as having the caps close to the chip. That basically means wide traces, 32mil or more ideally.

BTW the reason for wide traces in supply and ground wire is usually for low inductance, not because of the

higher current, since most chips take a few tens of mA and the resistance of a 10 mil trace wouldn't be an

issue, but the doubling of the inductance that represents compared to a 32 mil trace is important for decoupling.

I find its usually rather cramped fitting the caps in, and a few signals have to cross under the chip just to

complicate the ground and/or vcc planes:

As you see I often put vias on the chip pads to save space, and often these are the only

components on the underside so can be hand soldered (tombstoning not an issue!). This

is my best example, often I rely on the planes to distribute the decoupling and only have 3 caps.

[Oh, and I often use three 0.1uF and one 1uF or similar combination]

Thanks for the feedback.

Massimo

the bible I read at an impressionable age. Explains how digital logic really works (each gate switching

slams a current transient onto the supply rails which causes a voltage due to the impedance of the

supply wiring. Ultimately too much voltage and your chip glitches. The goal of decoupliing is to

put a stiff voltage source near to the chip (near means low inductance path), that can absorb the

current pulse without buckling.

Pretty much the only property of the capacitor that matters is its series inductance for this reason.

Well, it has to be stiff enough until the voltage regulator can notice and react to the load-change.

For CMOS the load doesn't change much in the long term, but if you drive high current stuff like

LEDs then larger caps are needed as well as the ubiquitous 100nF as the load changes are more than

short term spikes, and the voltage regulator takes time to adjust measured in microseconds.

That book is where I first learn of Oliver Heaviside, an unsung hero of electromagnetic theory...

-Phil

It is available online, seems to be legitimate site:

http://www.ivorcatt.org/digital-hardware-design.htm

C.W.

Although some of his ideas on EM theory are said to be a bit questionable, if not crackpot, by the academic community.

Lol, that wasn't a comment on Mr. Catt. I meant that it doesn't look like it's just some schmuck posting someone else's work on the interwebs...

C.W.

http://www.ultracad.com/article_outline.htm

May be more than you want to know!

But with MLCC, I'm not sure this is true anymore. A 1uF cap is really about the same thing as 10 of 0.1uF caps stacked on top of each other...

I suppose I could check the rated ESL values, but my hunch is that there is little difference...

Well this book is just applying Heaviside's telegraph equations to logic signals, and explaining why TTL works

at all when inadequately decoupled. Its from an era when analog trained engineers were designing digital logic

boards and getting it wrong (!).

When it comes to physical circuits there is no such thing as "digital". The electrons and fields don't know anything about "digital". It has been said that modern fast digital designers are basically working on analog RF circuits.

I once had a new team of engineers design a new product independently of which they were very proud of as they showed off their wonderful pcb, so full of chips, it must be good, but nary was there a cap in sight. Since they didn't comprehend my head shaking and mutterings I connected the PCB to the scope to show them what the problem was and there was so much noise to be seen, the spikes on the logic rails were measured in volts. See! I said, fully expecting them to go cowering into the corner in shame but to my surprise they still didn't see what the problem was. Ah, ignorance is bliss, but it took them a long long time to sort out all those "software bugs"