Multi-cog timing questions - providing pixel data for VGA display

Wossname

Posts: 174

Wossname

Posts: 174

Any VGA / multi-cog gurus out there?

I've been trying to modify the VGA demo (512x384 with tile driver method) in order to get full access to all the individual pixels and with some success too, so far so good.

However I'd like to have my code fetch a 32-bit value out of an off-board SRAM module - an operation that takes about 50 instructions. Doing that inline with the 67Hz VGA signal generation code causes the signal to lose sync (due to the extra time taken to get through the loop) and the LCD monitor shuts down into power saving mode (because it doesn't recognise the broken signal).

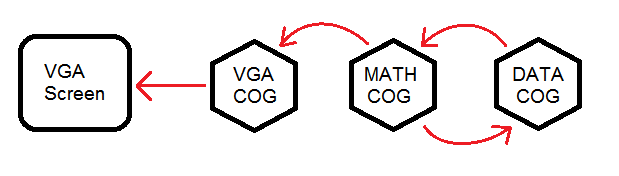

So I was wondering - if I do all my SRAM stuff in a separate cog I can use wrlong/rdlong to pass the data to the VGA cog. But how do I let the SRAM cog know that the VGA cog is ready to accept another set of 32 bits? If I set a flag then the SRAM cog would somehow have to wait for it to be set. And to add further annoyance, a third cog will be talking to the SRAM module as well and reads/writes are mutually exclusive!

What would be a sensible approach to this problem? I'm not looking for code particularly, just a strategy.

Thanks for reading

I've been trying to modify the VGA demo (512x384 with tile driver method) in order to get full access to all the individual pixels and with some success too, so far so good.

However I'd like to have my code fetch a 32-bit value out of an off-board SRAM module - an operation that takes about 50 instructions. Doing that inline with the 67Hz VGA signal generation code causes the signal to lose sync (due to the extra time taken to get through the loop) and the LCD monitor shuts down into power saving mode (because it doesn't recognise the broken signal).

So I was wondering - if I do all my SRAM stuff in a separate cog I can use wrlong/rdlong to pass the data to the VGA cog. But how do I let the SRAM cog know that the VGA cog is ready to accept another set of 32 bits? If I set a flag then the SRAM cog would somehow have to wait for it to be set. And to add further annoyance, a third cog will be talking to the SRAM module as well and reads/writes are mutually exclusive!

What would be a sensible approach to this problem? I'm not looking for code particularly, just a strategy.

Thanks for reading

Comments

What I did there is define a buffer in HUB RAM that one cog fills with bitmap data and the TV driver then uses for output...