Medium Frequency Sine Waves (1~3MHz) using PASM into a R2R network

Tubular

Posts: 4,772

Tubular

Posts: 4,772

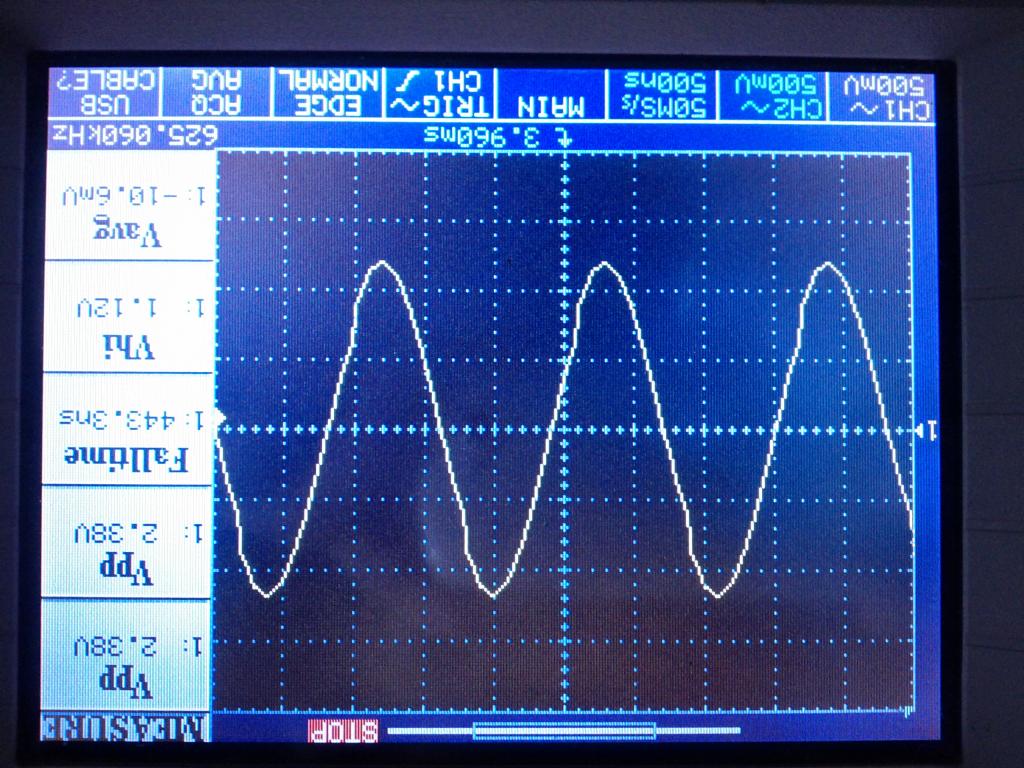

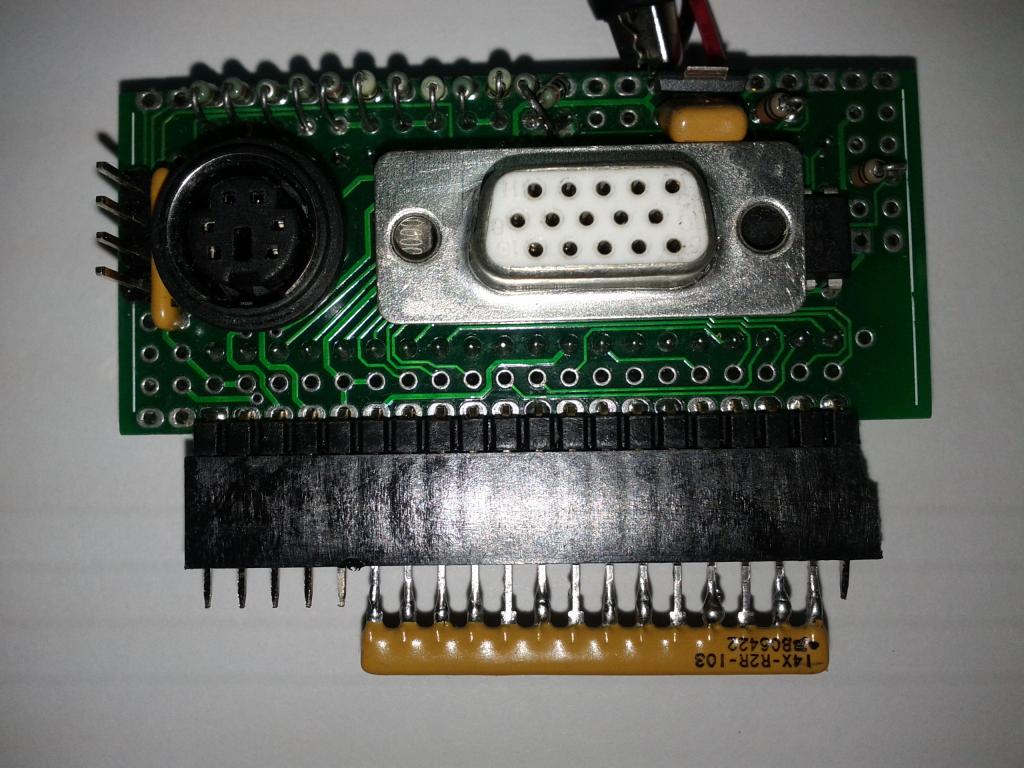

I've placed a new object for generating sine waves ~1 to 3 MHz into a R2R network.

It uses a kind of 'pre calculated DDS, so clips along at 4 CLK per sample (20/25MHz output rate). There is some secret sauce to eliminate the normal blind sample associated with the loop repeat JMP instruction (read the comments in the object)

This is my first original PASM program, so I'm pretty chuffed that it works.

I've used N=16 to give a reasonable quality of sine wave, but the theory should apply for N=3 to ..about N=328. More than 1 cycle can optionally occupy the N samples. Its a pity there isn't enough room in the cog to store instructions+data for N=360 but N=240 is usefully divisable by all sorts of factors.

It uses a kind of 'pre calculated DDS, so clips along at 4 CLK per sample (20/25MHz output rate). There is some secret sauce to eliminate the normal blind sample associated with the loop repeat JMP instruction (read the comments in the object)

This is my first original PASM program, so I'm pretty chuffed that it works.

I've used N=16 to give a reasonable quality of sine wave, but the theory should apply for N=3 to ..about N=328. More than 1 cycle can optionally occupy the N samples. Its a pity there isn't enough room in the cog to store instructions+data for N=360 but N=240 is usefully divisable by all sorts of factors.

Comments

The sine waveform does not quite look as good as it could, but that may be sample aliasing effects ?

Seems to be a larger change ~ 60' ?

With 12 bits on the Y axis, and a fixed 4 on the X, it's a little 'unbalanced'.

Better might be 8bits on Y, which should match the video streaming, and code playback to be from a larger, pre-loaded buffer, for

software frequency control.

With control on both the sample-repeat, and the cycle-count, you can get quite accurate frequencies (small granularity).

eg Running some simple maths, with ~ 8192 samples ceiling, you can generate any of 4000 frequencies between Fs/12 +/- 8%

to an average error of ~0.4ppm., and a worst case of ~60ppm.

Next step is to extend the buffer to 240 samples, as 240 samples + 121 for the cosine data values will mostly fill a cog. 300 samples + 151 data might also fit. Then look at how to do some self modifying code to change where the JMP jumps back to (to optionally shorten the buffer to any arbitrary length < 300). And then see if its possible to have some spin code automatically calculate the correct buffer sample values from the prop's sine lookup table (or cordic??)

Having some fun with this, and its oddly addictive.

If there is a delay at the FrameClocks value, then your 'place at the flat' idea might avoid that.

I've attached a plot of yet another way to generate sines - here, instead of dumping a RAM array at fixed rate, you always increment/decrement the voltage the same, and instead vary the duration of each step. So you use all possible DAC values.

It is tuned to give 45' slopes, matching the sine at the highest step rates, and then swallows counts, at others.

The Grey line is the Wait-Load values & load times, to pause a triangle counter, which then magically becomes sine. It is designed for Logic, where counters are cheap, but Memory is not.

Frequency of course is now some maths-value.

You need to add a LC low-pass filter to cleanup the output, it will benefit a lot. Also 14 bits is overkill, 8 would be plenty

A while back I had a play with the AD9851 which does DDS at 180MHz and 10bits, can generate any frequency from DC to 60MHz and of course allows phase and frequency modulation... There are DDS chips upto 1GHz but expensive still.

How about seeing you can work out a way to dynamically change phase (and then frequency)?

I haven't gotten stuck into the video generators for the "high frequency" gen partly because I've hit the target I need for the current job. But I'd still like to try it for completeness sake.

Mark_T I've played with the 4CH AD9959 which adds the amplitude control too. The eval board for that chip used to be under $300, and combined with its software, it's a great bit of test equipment let alone evaluation board. I think they realized that and bumped the price a bit.

The phase change on the fly - isn't easy within the same cog. Thats the disadvantage of having such a pre-calculated unrolled loop with no conditions in it... you can't adjust on the fly. However one idea would be to set up a second cog with the new phase/amplitude/frequency ready to go, and cut over by stopping the first cog (and set a lock?) or something. You could possibly do phase shift keying that way. You could also exit the loop at that flat spot and disable the first cog's DIRA output setting within a few clock cycles, not sure if that would be good enough, and it would have to occur at that flat bit of the waveform. Or perhaps just killing the first cog is an option..