FPGA I/O for the propeller: vision (unfinished)

I dont read much of the post on this forum debating microcontroller architectures and languages, more enjoy the posts where fun people try to expand the propeller horizon. Here my (unsuccessful until now) attempt to give the propeller better vision.

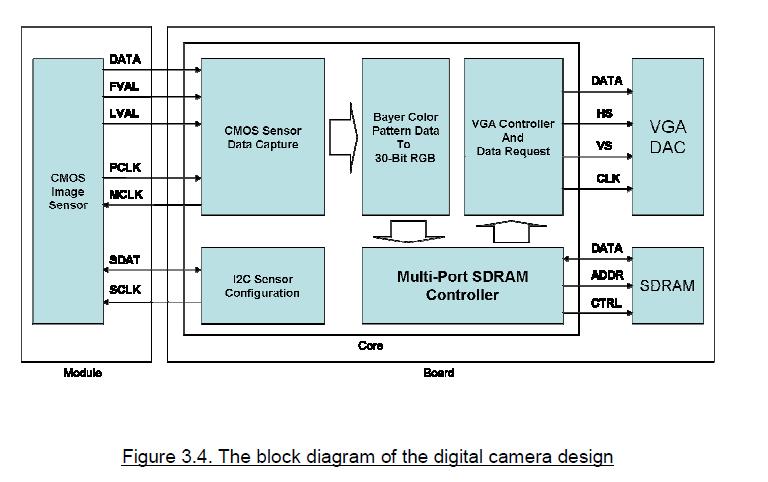

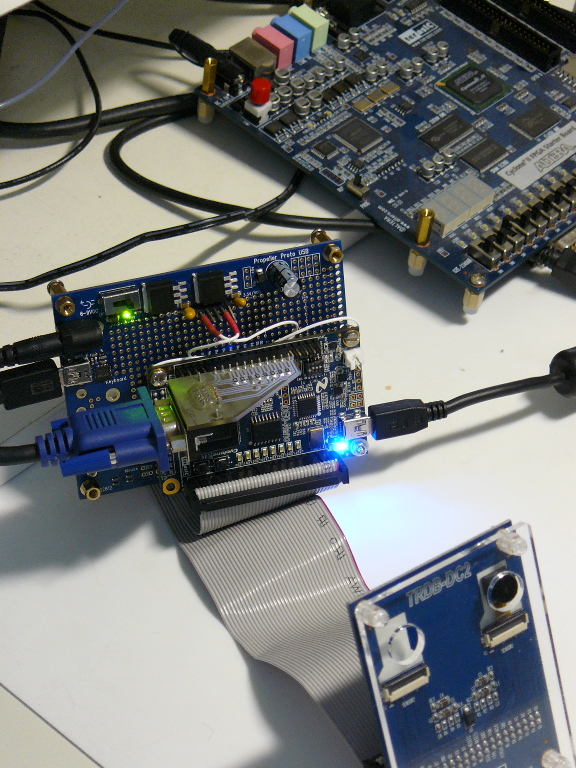

Days ago my Terasic DE0-nano board arrived, in a matter of hours it was married to a propeller protoboard, and running the soft- COG project presented earlier at this forum. Next attempt was to port a digital camera demo from the DE1 board (background) to the nano. Ttiming and clocking seems OK because there is a picture, but with bad colours and contrast. How to debug a problem like that? Because the only essential difference between the DE1 and the nano board (for this application) lies in the SDRAM chip, I played with the settings and inputs for the SDRAM controller, but to no avail.

There must be something else, the I2C control block, an error in pin definitions? I probably have to dig out the logic analyser and start tracking signals through the different IP function blocks. There is an extra block in the Verilog code compared to the diagram: a module that swaps columns left to right. Wait, my bad picture is left-right exchanged .

Food for thought at APEW? I feel the nano is great value, it can be used as a flexible peripheral into high end applications that the propeller cannot handle natively as large memory, high speed serial interfaces, machine vision etc.

Regards

Nico Hattink

Days ago my Terasic DE0-nano board arrived, in a matter of hours it was married to a propeller protoboard, and running the soft- COG project presented earlier at this forum. Next attempt was to port a digital camera demo from the DE1 board (background) to the nano. Ttiming and clocking seems OK because there is a picture, but with bad colours and contrast. How to debug a problem like that? Because the only essential difference between the DE1 and the nano board (for this application) lies in the SDRAM chip, I played with the settings and inputs for the SDRAM controller, but to no avail.

There must be something else, the I2C control block, an error in pin definitions? I probably have to dig out the logic analyser and start tracking signals through the different IP function blocks. There is an extra block in the Verilog code compared to the diagram: a module that swaps columns left to right. Wait, my bad picture is left-right exchanged .

Food for thought at APEW? I feel the nano is great value, it can be used as a flexible peripheral into high end applications that the propeller cannot handle natively as large memory, high speed serial interfaces, machine vision etc.

Regards

Nico Hattink