Cascaded core clocking to achieve sub nanosecond measurements.(this concept has

Clock Loop

Posts: 2,069

Clock Loop

Posts: 2,069

I had an idea the other day and posted it in the 10 ns memory access thread, but its more multi-core related.

Basically, why don't processor manufactures put each core on its own clock, so we can specify each cores clock rate independently?

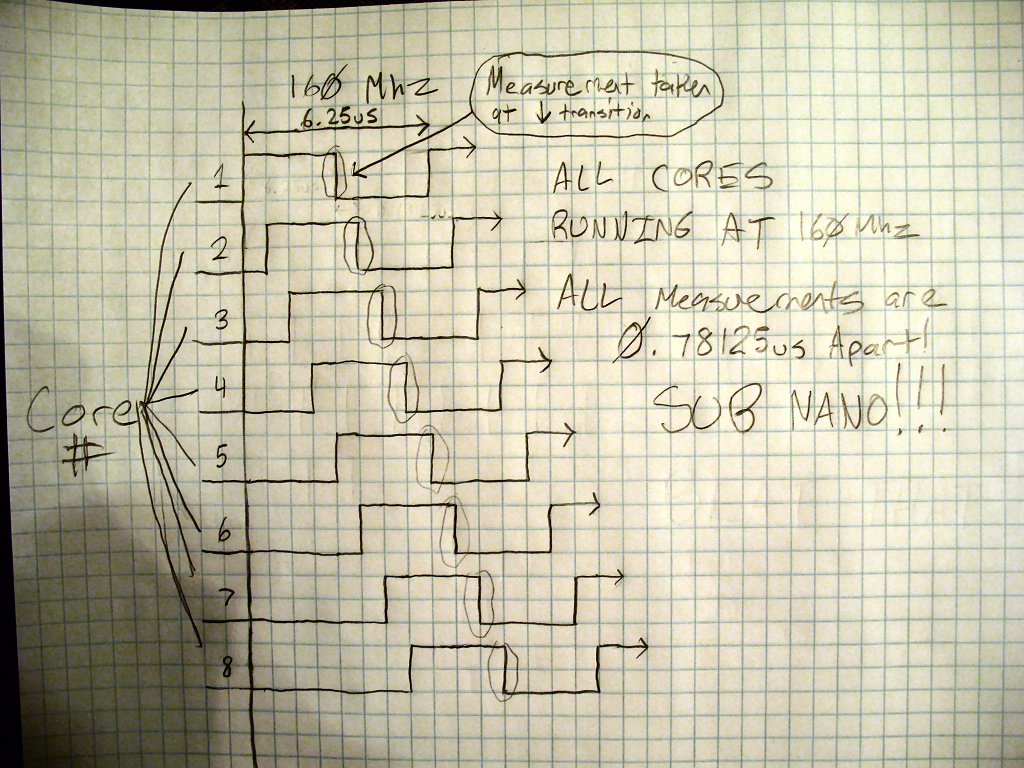

The reason I ask and suggest that the prop2 have this feature is because cascaded clocking of cores allows SUB nanosecond measurements to be made, and I think anyone would Smile their pants if the prop2 could work with that kind of speed.

Its possible I am over looking something in saying that because it is a big claim, but ...

Example.

Lets take a car and road analogy.

The prop has 8 cores that are clock locked, they use the same clock source.

I would say this is like 8 cars traveling down the road, side by side, at the same speed, and they all started out at the same time.

They all arrive at the finish line, at the same time.

(this would be 8 cores measuring signals all at exactly the same time.)

If those 8 cars were followed by 8 more, all cars would pass the finish line at the same time.

But there is a gap when NO cars are passing the finishline

(aka, the props 8 cores are all in transition, getting ready to make another measurement)

Now if I started all 8 cars out at the same time. But this time each car is 1 inch behind the other. (they are side by side still)

These cars all pass the finish line, but 1 inch behind the one ahead.

(this would be 8 cores measuring signals just a hair behind the core that started first.)

Now if THESE 8 cars are followed by 8 more, then at ANY given moment, a car is always passing the finishline.

Now if the road that the 8 cars are traveling on is a circle, and is slightly shorter than the 8th car, then the first car is now slightly behind the 8th car.

(this would be all 8 cores measuring sub-nanosecond signals, and looping to have continuous measurements)

So basically I ended up making a prop2 that can measure a signal at a rate much higher than its own clock speed because I cascaded the clocks so each measurement was taken a few ns after the first one.

Whats wrong with this?

▔▔▔▔▔▔▔▔▔▔▔▔▔▔▔▔▔▔▔▔▔▔▔▔

TERMS OF USE: MIT License

"Permission is hereby granted, free of charge, to any pers...........................

..............................OMITTED FOR FORUM...............................................

.................. OF OR IN CONNECTION WITH THE SOFTWARE OR THE USE OR OTHER DEALINGS IN THE SOFTWARE. "

The dsp/fpga king is dead, long live the prop.

Post Edited (Clock Loop) : 12/5/2009 3:28:51 AM GMT

Basically, why don't processor manufactures put each core on its own clock, so we can specify each cores clock rate independently?

The reason I ask and suggest that the prop2 have this feature is because cascaded clocking of cores allows SUB nanosecond measurements to be made, and I think anyone would Smile their pants if the prop2 could work with that kind of speed.

Its possible I am over looking something in saying that because it is a big claim, but ...

Example.

Lets take a car and road analogy.

The prop has 8 cores that are clock locked, they use the same clock source.

I would say this is like 8 cars traveling down the road, side by side, at the same speed, and they all started out at the same time.

They all arrive at the finish line, at the same time.

(this would be 8 cores measuring signals all at exactly the same time.)

If those 8 cars were followed by 8 more, all cars would pass the finish line at the same time.

But there is a gap when NO cars are passing the finishline

(aka, the props 8 cores are all in transition, getting ready to make another measurement)

Now if I started all 8 cars out at the same time. But this time each car is 1 inch behind the other. (they are side by side still)

These cars all pass the finish line, but 1 inch behind the one ahead.

(this would be 8 cores measuring signals just a hair behind the core that started first.)

Now if THESE 8 cars are followed by 8 more, then at ANY given moment, a car is always passing the finishline.

Now if the road that the 8 cars are traveling on is a circle, and is slightly shorter than the 8th car, then the first car is now slightly behind the 8th car.

(this would be all 8 cores measuring sub-nanosecond signals, and looping to have continuous measurements)

So basically I ended up making a prop2 that can measure a signal at a rate much higher than its own clock speed because I cascaded the clocks so each measurement was taken a few ns after the first one.

Whats wrong with this?

▔▔▔▔▔▔▔▔▔▔▔▔▔▔▔▔▔▔▔▔▔▔▔▔

TERMS OF USE: MIT License

"Permission is hereby granted, free of charge, to any pers...........................

..............................OMITTED FOR FORUM...............................................

.................. OF OR IN CONNECTION WITH THE SOFTWARE OR THE USE OR OTHER DEALINGS IN THE SOFTWARE. "

The dsp/fpga king is dead, long live the prop.

Post Edited (Clock Loop) : 12/5/2009 3:28:51 AM GMT

Comments

-Phil

However, In the PropII, each instruction only takes 2 clocks, so you could offset a pair of cogs to get 1 clock sampling. You are not going to achieve anything better than this, because the props have to synchronise to the hub.

▔▔▔▔▔▔▔▔▔▔▔▔▔▔▔▔▔▔▔▔▔▔▔▔

Links to other interesting threads:

· Home of the MultiBladeProps: TriBlade,·RamBlade,·SixBlade, website

· Single Board Computer:·3 Propeller ICs·and a·TriBladeProp board (ZiCog Z80 Emulator)

· Prop Tools under Development or Completed (Index)

· Emulators: CPUs Z80 etc; Micros Altair etc;· Terminals·VT100 etc; (Index) ZiCog (Z80) , MoCog (6809)

· Search the Propeller forums·(uses advanced Google search)

My cruising website is: ·www.bluemagic.biz·· MultiBladeProp is: www.bluemagic.biz/cluso.htm

One could use 8 props to do this, but im sure other issues arrive.

Now I know why I keep coming back to this forum.

Its chock full of smart people to throw ideas at.

Post Edited (Clock Loop) : 12/5/2009 3:25:08 AM GMT