strange adc (TLC1549) problems - Solved

Hello,

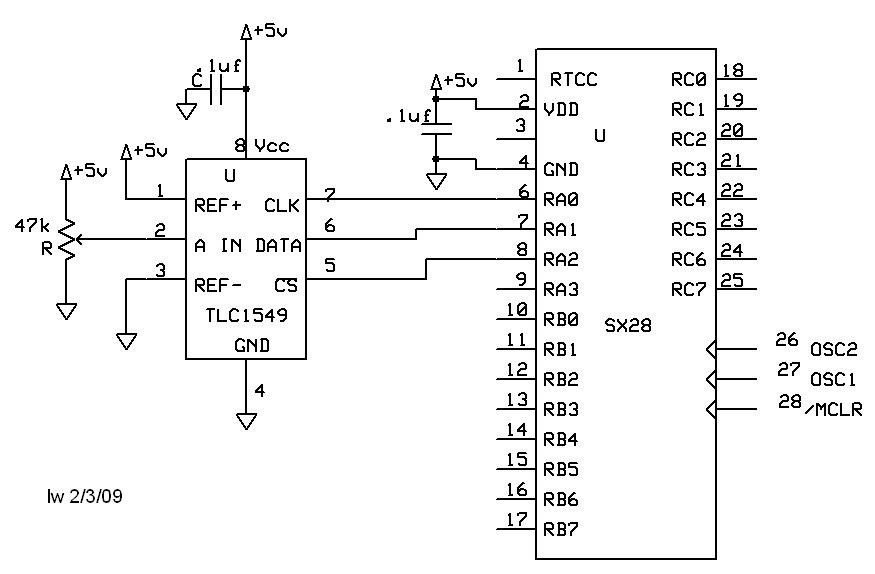

I'm having a problem interfacing a Texas Inst TLC1549 to an SX28 (in an existing product) . to get it it working i am using a sx tech board and the circuit attached.

The problem is i get exactly two full scale readings. With Ref+ tied to +5 in debug mode i can see the output of the adc go from 0 to ~1022 when vin ~2.5, roll over to 0 (say just above 2.5) and continue on to 1023 when vin +5.0

trying to figure it out i have buffered the input with an op amp, same behavior. also i have tied the ref+ to 3.0 v and that changed the roll over point to 1.5 v

attached it the sample programming, the macros have been mainlined in the program.

any ideas?

thank you for you time

link

Post Edited (lincoln) : 2/5/2009 5:31:33 PM GMT

I'm having a problem interfacing a Texas Inst TLC1549 to an SX28 (in an existing product) . to get it it working i am using a sx tech board and the circuit attached.

The problem is i get exactly two full scale readings. With Ref+ tied to +5 in debug mode i can see the output of the adc go from 0 to ~1022 when vin ~2.5, roll over to 0 (say just above 2.5) and continue on to 1023 when vin +5.0

trying to figure it out i have buffered the input with an op amp, same behavior. also i have tied the ref+ to 3.0 v and that changed the roll over point to 1.5 v

attached it the sample programming, the macros have been mainlined in the program.

any ideas?

thank you for you time

link

Post Edited (lincoln) : 2/5/2009 5:31:33 PM GMT

Comments

Your readings are probably shifted to the left one bit.

Bean.

▔▔▔▔▔▔▔▔▔▔▔▔▔▔▔▔▔▔▔▔▔▔▔▔

- - - - - - - - - - - - - - - - - - - - - - - - - - - - - - -

·The next time you need a hero don't look up in the sky...Look in the mirror.

·

That was (well still is) my thinking originally.

the TLC1549 will take clock inputs up to 16 bits, the first 10 are used to transfer the the previous conversion, the extra clocks are used for timing the next conversion in a long mode. During the extra 11 to 16 clocks the output is held low. (if i understand the data sheet correctly)

if i _shiftinw for 11 or 12 bits i get the right number of trailing 0, (in a binary number)

the only think i can think of is to hookup a j/k flip flop, witch should reed a bit pattern of 101010101 depending on the starting state...

link

thanks

link