Some info merged from:

Propeller2DetailedPreliminaryFeatureList-v2.pdf

Some info merged from: From diverse thread's

<sup>&#</sup>x27;SPECIAL REGISRERS

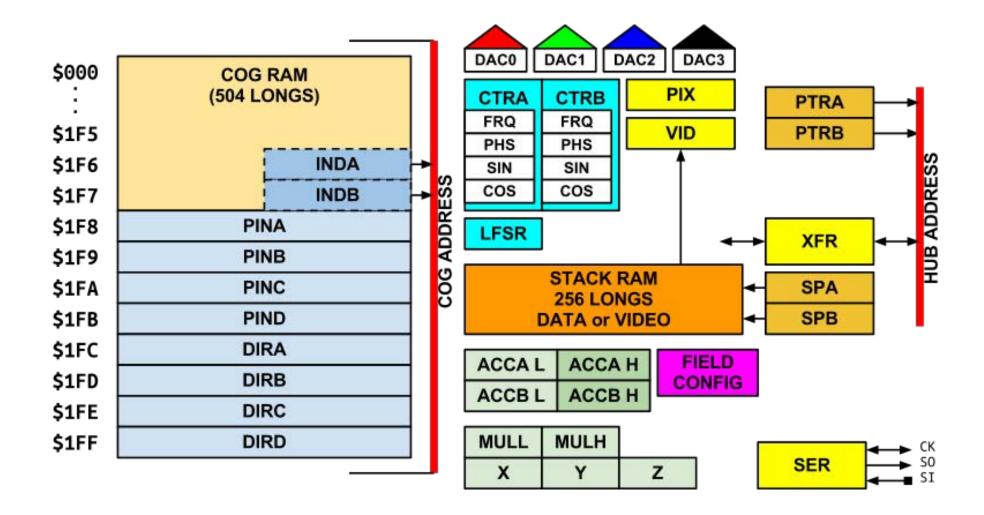

"Nutson - Sapieha. I remember Chip saying there were more than 40 registers now. ' We will get a full description in due time. 'Just read the preliminary feature list and made this list for my own reference: ' I added some more. 'There are 10 memory mapped registers that allow control over I/O pins and indirection: INDA/INDB 0x1F6 - 0x1F7'Indirect registers access to COG memory PINA/PINB/PINC/PIND 0x1F8 - 0x1FB 'Read / write I/O ports DIRA/DIRB/DIRC/DIRD 0x1FC - 0x1FF'Enables or disables the output functionally of PORTA. 'Input reading is never disabled. 'All other registers can be accessed only with specialised instructions PTRA/PTRB 'Pointer for hub access 'CLUT (stack) pointer SPA/SPB CNT 'System time counter 'Each have FRQ, PHS, SIN and COS register CTRA/CTRB (FRQ, PHS, SIN, COS) MULLL/MULLH 'etc, registers to acces the multiply, divide, SQRT and CORDIC ooperations DAC0/DAC1/DAC2/DAC3 'configuration and data for the DAC's LFSR 'Random number generator MACA/MACB 'Accu for 64 bit MAC operation (ACCA 64-bit) 'Multiply Accumulator A. (ACCB 64-bit) 'Multiply Accumulator B. CCCC 'Condition bit pattern (not available for instructions using indirect addressing) 'destination encoding for all instructions that support indirect addressing AΑ INDA/INDB 'source encoding for all instructions that support indirect addressing BB INDA/INDB CCCC inda/indb - CCCC=1111 after first stage of pipeline if inda/indb used (indx=inda/indb) xxAAxx00source indx source indx++ xx01xx10source indx--

```

xx11

source ++indx

BBxx

00x

destination indx

destination indx++

01xx

10xx

destination indx--

11xx

destination ++indx

Instruction

Encoding

D(estination),S(ource)

D(estination),S(ource)

MNEMONIC D,S

---- 0 1111 DDDDDDDD SSSSSSSS

----- 1 1111 DDDDDDDDD nnnnnnnn

MNEMONIC D,#n

[COND] MNEMONIC D,S [WZ] [WC] [NR]

---- ZCR 1 CCCC DDDDDDDDD SSSSSSSS

MNEMONIC INDA,S [WZ] [WC] [NR]

---- ZCR 0 AA00 111110110 SSSSSSSS

---- ZCR 0 AA00 111110110 nnnnnnnn

MNEMONIC INDA, #n [WZ] [WC] [NR]

MNEMONIC D, INDA [WZ] [WC] [NR]

---- ZCR 0 00AA DDDDDDDDD 111110110

MNEMONIC INDA, INDB [WZ] [WC] [NR]

---- ZCR 0 AABB 111110110 111110111

_____

Example

RDBYTE D,S

000000 0 01 0 1111 DDDDDDDDD SSSSSSSS

RDBYTE D,PTR

000000 0 01 1 CCCC DDDDDDDDD SUPNNNNN

RDBYTE D,S [WZ]

000000 Z 01 0 CCCC DDDDDDDDD SSSSSSSS

[COND]

[COND]

RDBYTE D,PTR [WZ]

000000 Z 01 1 CCCC DDDDDDDDD nnnnnnnn

INDA,S [WZ]

000000 Z 01 0 AA00 111110110 SSSSSSSS

RDBYTE

RDBYTE INDA, PTR [WZ]

000000 Z 01 1 AA00 111110110 SUPNNNNNN

RDBYTE

D, INDA [WZ]

000000 Z 01 0 00AA DDDDDDDDD 111110110

000000 Z 01 0 AABB 111110110 1111110111

RDBYTE INDA, INDB [WZ]

SSSSSSSS

source operand

SSSSSSSS

register

#SSSSSSSS immediate, zero-extended

'Zero effect

'Carry effect

'Register effect

'Immediate effect

```

```

effects

ZCR

000

nz, nc, nr

001

nz, nc, wr

010

nz, wc, nr

011

nz, wc, wr

100

wz, nc, nr

101

wz, nc, wr

110

wz, wc, nr

111

wz, wc, wr

Effect

Result

[[(default)] meaning of zero flag set to 1]

WZ

WC

[[(default)] meaning of carry flag set to 1]

[[(default)] meaning of value written to register]

WR

COGINIT D

000011 000 0 1111 DDDDDDDDD SSSSSSSS

[COND] COGINIT D,S [WZ] [WC] [WR]

000011 ZCR 0 CCCC DDDDDDDDD SSSSSSSS

COGSTOP D

000011 000 1 1111 DDDDDDDDD 000000011

[COND] COGSTOP D [WZ] [WC] [WR]

000011 ZCR 0 CCCC DDDDDDDDD 000000011

```

# PROPELLER 2 MEMORY

-----

In the Propeller 2, there are two primary types of memory:

#### HUB MEMORY

128K bytes of main memory shared by all cogs

- cogs launch from this memory

- cogs can access this memory as bytes, words, longs, and quads (4 longs)

- \$00000..\$00E7F is ROM contains Booter, SHA-256/HMAC, and Monitor

- \$00E80..\$1FFFF is RAM for application usage

```

COG MEMORY (8 instances)

512 longs of register RAM for code and data usage

- simultaneous instruction, source, and destination reading, plus writing

- last eight registers are for I/O pin control

256 longs of stack RAM for data and video usage

- accessible via push and pop operations

- video circuit can read data simultaneously and asynchronously

XXXXXX XXX X XXXX DDDDDDDDD SSSSSSSS

S Source field in instruction

Destination field in instruction

PTRA and PTRB are only for pointing to HUB memory .

INDA and INDB are for pointing to COG memory .

SPA and SPB are for pointing to CLUT/stack memory .

'If you want to read longs quickly into registers,

it's simplest to just do 'RDLONGC INDA++,PTRA++'.

' Less stuff to think about that way.

PTR EXPRESSIONS:

-32 .. +31

INDEX

Simple offset

0 .. 31

++ Auto-increments range

INDEX

0 .. 32

-- Auto-decrement range

INDEX

SCALE

1

BYTE

SCALE

WORD

SCALE

4

LONG

SCALE

16

QUAD

HUB MEMORY INSTRUCTIONS

```

These instructions read and write HUB memory .

All instructions use D as the data conduit, except WRQUAD/RDQUADC, which uses the four QUAD registers. The QUADs can be mapped into COG register space using the SETQUAD instruction or kept hidden, in which case they are still useful as data conduit and as a read cache. If mapped, the QUADs overlay four contiguous COG registers. These overlaid registers can be read and written as any other registers, as well as executed. Any write via D to the QUAD registers, when mapped, will affect the underlying COG registers, as well. A RDQUAD/RDQUADC will affect the QUAD registers, but not the underlying COG registers.

The cached reads RDBYTEC/RDWORDC/RDLONGC/RDQUADC will do a RDQUAD if the current read address is outside of the 4-long window of the prior RDQUAD. Otherwise, they will immediately return cached data. The CACHEX instruction invalidates the cache, forcing a fresh RDQUAD next time a cached read executes.

Hub memory instructions must wait for their COG's HUB cycle, which comes once every 8 clocks. The timing relationship between a COG's instruction stream and its HUB cycle is generally indeterminant, causing these instructions to take varying numbers of clocks. Timing can be made determinant, though, by intentionally spacing these instructions apart so that after the first in a series executes, the subsequent HUB memory instructions fall on HUB cycles, making them take the minimal numbers of clocks. The trick is to write useful code to go in between them.

```

WRBYTE/WRWORD/WRLONG/WRQUAD/RDQUAD

RDBYTE/RDWORD/RDLONG

RDBYTEC/RDWORDC/RDLONGC

RDQUADC

complete on the HUB cycle, making them take 1..8 clocks.

complete on the 2nd clock after the HUB cycle, making them take 3..10 clocks.

take only 1 clock if data is cached, otherwise 3..10 clocks.

takes only 1 clock if data is cached, otherwise 1..8 clocks.

```

Floating QUAD 'window does not copy its contents to the underlying registers.

After a RDQUAD, mapped QUAD registers are accessible via D and S after three clocks:

\_\_\_\_

```

RDQUAD hubaddress 'read a quad into the QUAD registers mapped at quad0..quad3

NOP 'do something for at least 3 clocks to allow QUADs to update

NOP

NOP

CMP quad0,quad1 'mapped QUADs are now accessible via D and S

```

```

----

```

```

After a RDQUAD, mapped QUAD registers are executable after three clocks and one instruction:

SETQUAD #quad0

'map QUADs to quad0..quad3

Floating QUAD window does not copy its contents to the underlying registers.

RDQUAD hubaddress

'read a quad into the QUAD registers mapped at quad0..quad3

NOP

'do something for at least 3 clocks to allow QUADs to update

NOP

NOP

NOP

'do at least 1 instruction to get QUADs into pipeline

quad0

NOP

'QUAD0..QUAD3 are now executable

quad1

NOP

NOP

quad2

quad3

NOP

After a SETQUAD, mapped QUAD registers are writable immediately, but original contents are

readable via D and S after 2 instructions:

SETQUAD #quad0

'map QUADs to quad0..quad3 (new address)

'do at least two instructions to queue up QUADs

NOP

NOP

```

On cog startup, the QUAD registers are cleared to 0's.

quad0,quad1

CMP

instructions clocks

000000 000 0 CCCC DDDDDDDDD SSSSSSSS WRBYTE D,S write lower byte in D at S 1..8

'mapped QUADS are now accessible via D and S

| 000000 000 1 CCCC DDDDDDDDD SUPNNNNN  | WRBYTE D,PTR  | write lower byte in D at PTR                | 18         |                                |

|---------------------------------------|---------------|---------------------------------------------|------------|--------------------------------|

| 000000 Z01 0 CCCC DDDDDDDDD SSSSSSSS  | RDBYTE D,S    | read byte at S into D                       | 310        |                                |

| 000000 Z01 1 CCCC DDDDDDDDD SUPNNNNN  | RDBYTE D,PTR  | read byte at PTR into D                     | 310        |                                |

| 000000 Z11 0 CCCC DDDDDDDDD SSSSSSSS  | RDBYTEC D,S   | read cached byte at S into D                | 1, 310     |                                |

| 000000 Z11 1 CCCC DDDDDDDDD SUPNNNNN  | RDBYTEC D,PTR | read cached byte at PTR into D              | 1, 310     |                                |

|                                       |               |                                             |            |                                |

| 000001 000 0 CCCC DDDDDDDDD SSSSSSSS  | WRWORD D,S    | <pre>write lower word in D at S</pre>       | 18         |                                |

| 000001 000 1 CCCC DDDDDDDDD SUPNNNNN  | WRWORD D, PTR | <pre>write lower word in D at PTR</pre>     | 18         |                                |

| 000001 Z01 0 CCCC DDDDDDDDD SSSSSSSS  | RDWORD D,S    | read word at S into D                       | 310        |                                |

| 000001 Z01 1 CCCC DDDDDDDDD SUPNNNNN  | RDWORD D, PTR | read word at PTR into D                     | 310        |                                |

| 000001 Z11 0 CCCC DDDDDDDDD SSSSSSSS  | RDWORDC D,S   | <pre>read cached word at S into D</pre>     | 1, 310     |                                |

| 000001 Z11 1 CCCC DDDDDDDDD SUPNNNNN  | RDWORDC D,PTR | <pre>read cached word at PTR into D</pre>   | 1, 310     |                                |

|                                       |               |                                             |            |                                |

| 000010 000 0 CCCC DDDDDDDDD SSSSSSSS  | WRLONG D,S    | write D at S                                | 18         |                                |

| 000010 000 1 CCCC DDDDDDDDD SUPNNNNN  | WRLONG D,PTR  | write D at PTR                              | 18         |                                |

| 000010 Z01 0 CCCC DDDDDDDDD SSSSSSSS  | RDLONG D,S    | read long at S into D                       | 310        |                                |

| 000010 Z01 1 CCCC DDDDDDDDD SUPNNNNN  | RDLONG D,PTR  | read long at PTR into D                     | 310        |                                |

| 000010 Z11 0 CCCC DDDDDDDDD SSSSSSSS  | RDLONGC D,S   | <pre>read cached long at S into D</pre>     | 1, 310     |                                |

| 000010 Z11 1 CCCC DDDDDDDDD SUPNNNNN  | RDLONGC D,PTR | <pre>read cached long at PTR into D</pre>   | 1, 310     |                                |

|                                       |               |                                             |            |                                |

| 000011 000 0 CCCC DDDDDDDDD 010110000 | WRQUAD D      | _                                           | 18         | (waits <b>for hub</b> )        |

| 000011 001 1 CCCC SUPNNNNNN 010110000 | WRQUAD PTR    | write QUADs at PTR                          | 18         | (waits <b>for hub</b> )        |

| 000011 000 0 CCCC DDDDDDDDD 010110001 | RDQUAD D      | read quad at D into QUADs                   | 18         | (waits <b>for hub</b> )        |

| 000011 001 1 CCCC SUPNNNNNN 010110001 | RDQUAD PTR    | read quad at PTR into QUADs                 | 18         | (waits <b>for hub</b> )        |

| 000011 010 0 CCCC DDDDDDDDD 010110001 | RDQUADC D     | <pre>read cached quad at D into QUADs</pre> | 1, 18      | (waits <b>for hub if</b> cache |

| miss)                                 |               |                                             |            |                                |

| 000011 011 1 CCCC SUPNNNNNN 010110001 | RDQUADC PTR   | read cached quad at PTR into QUADs          | 1, 18      | (waits for hub if cache        |

| miss)                                 |               |                                             |            |                                |

|                                       |               | Conditionally read into OUADs from          | hub memory | at D                           |

Conditionally read into QUADs from hub memory at D

### PTR EXPRESSIONS:

| INDEX | <b>-</b> 32 | +31 | Simple offset            |

|-------|-------------|-----|--------------------------|

| INDEX | 0           | 31  | ++ Auto-increments range |

| INDEX | 0           | 32  | Auto-decrement range     |

| SCALE | 1           |     | BYTE                     |

| SCALE | 2           |     | WORD                     |

```

SCALE

4

LONG

SCALE

16

QUAD

INDEX = -32...+31 for simple offsets, 0...31 for ++'s, or 0...32 for --'s

SCALE = 1 for byte, 2 for word, 4 for long, or 16 for quad

S = 0 for PTRA, 1 for PTRB

U = 0 to keep PTRx same, 1 to update PTRx

P = 0 to use PTRx + INDEX*SCALE, 1 to use PTRx (post-modify)

NNNNNN = INDEX

nnnnn = -INDEX

SUP NNNNNN

PTR expression

000 000000

PTRA

'use PTRA

100 000000

PTRB

'use PTRB

011 000001

PTRA++

'use PTRA,

PTRA += SCALE

111 000001

PTRB += SCALE

PTRB++

'use PTRB,

011 111111

PTRA--

'use PTRA,

PTRA -= SCALE

111 111111

PTRB--

'use PTRB,

PTRB -= SCALE

'use PTRA + SCALE,

010 000001

PTRA += SCALE

++PTRA

110 000001

'use PTRB + SCALE,

PTRB += SCALE

++PTRB

010 111111

--PTRA

'use PTRA - SCALE,

PTRA -= SCALE

110 111111

'use PTRB - SCALE,

--PTRB

PTRB -= SCALE

000 NNNNNN

PTRA[INDEX]

'use PTRA + INDEX*SCALE

100 NNNNNN

PTRB[INDEX]

'use PTRB + INDEX*SCALE

011 NNNNNN

PTRA++[INDEX]

'use PTRA,

PTRA += INDEX*SCALE

111 NNNNNN

'use PTRB,

PTRB++[INDEX]

PTRB += INDEX*SCALE

011 nnnnnn

PTRA--[INDEX]

'use PTRA,

PTRA -= INDEX*SCALE

111 nnnnnn

PTRB--[INDEX]

'use PTRB,

PTRB -= INDEX*SCALE

010 NNNNNN

++PTRA[INDEX]

'use PTRA + INDEX*SCALE, PTRA += INDEX*SCALE

110 NNNNNN

++PTRB[INDEX]

'use PTRB + INDEX*SCALE, PTRB += INDEX*SCALE

010 nnnnnn

--PTRA[INDEX]

'use PTRA - INDEX*SCALE, PTRA -= INDEX*SCALE

'use PTRB - INDEX*SCALE, PTRB -= INDEX*SCALE

110 nnnnnn

--PTRB[INDEX]

```

Examples:

```

000000 Z01 1 CCCC DDDDDDDD 000000000

'read byte at PTRA into D

RDBYTE D,PTRA

000001 000 1 CCCC DDDDDDDDD 111000001

'write lower word in D at PTRB,

PTRB += 2

WRWORD D, PTRB++

000010 Z01 1 CCCC DDDDDDDD 011111111

RDLONG D,PTRA--

'read long at PTRA into D,

PTRA -= 4

000011 001 1 CCCC 110000001 010110001

'read quad at PTRB+16 into QUADs,

RDQUAD

++PTRB

PTRB += 16

000000 000 1 CCCC DDDDDDDDD 010111111

WRBYTE D, --PTRA

'write lower byte in D at PTRA-1,

PTRA -= 1

000001 000 1 CCCC DDDDDDDDD 100000111

'write lower word in D to PTRB+7*2

WRWORD D,PTRB[7]

000010 Z11 1 CCCC DDDDDDDDD 011001111

RDLONGC D, PTRA++[15]

'read cached long at PTRA into D,

PTRA += 15*4

000011 001 1 CCCC 1111111101 010110000

WRQUAD PTRB--[3]

'write QUADs at PTRB,

PTRB -= 3*16

000000 000 1 CCCC DDDDDDDDD 010000110

'write lower byte in D to PTRA+6*1,

PTRA += 6*1

WRBYTE D,++PTRA[6]

000001 Z01 1 CCCC DDDDDDDD 110110110

RDWORD D,--PTRB[10]

'read word at PTRB-10*2 into D,

PTRB -= 10*2

```

#### Bytes, Words, Longs, and Quads 'are addressed as follows:

| address        | byte | word          | long      | quad                                 |

|----------------|------|---------------|-----------|--------------------------------------|

| 00000-         | 50   | <b>*</b> 7250 | *706F7250 | *0C7CCC03_0C7C2000_20302E32_706F7250 |

| 00001-         | 72   | 7250          | 706F7250  | 0C7CCC03_0C7C2000_20302E32_706F7250  |

| 00002-         | 6F   | *706F         | 706F7250  | 0C7CCC03_0C7C2000_20302E32_706F7250  |

| 00003-         | 70   | 706F          | 706F7250  | 0C7CCC03_0C7C2000_20302E32_706F7250  |

| 00004-         | 32   | *2E32         | *20302E32 | 0C7CCC03_0C7C2000_20302E32_706F7250  |

| 00005-         | 2E   | 2E32          | 20302E32  | 0C7CCC03_0C7C2000_20302E32_706F7250  |

| 00006-         | 30   | *2030         | 20302E32  | 0C7CCC03_0C7C2000_20302E32_706F7250  |

| 00007-         | 20   | 2030          | 20302E32  | 0C7CCC03_0C7C2000_20302E32_706F7250  |

| <b>-</b> 80000 | 00   | *2000         | *0C7C2000 | 0C7CCC03_0C7C2000_20302E32_706F7250  |

| 00009-         | 20   | 2000          | 0C7C2000  | 0C7CCC03_0C7C2000_20302E32_706F7250  |

| 0000A-         | 7C   | *0C7C         | 0C7C2000  | 0C7CCC03_0C7C2000_20302E32_706F7250  |

| 0000B-         | 0C   | 0C7C          | 0C7C2000  | 0C7CCC03_0C7C2000_20302E32_706F7250  |

| 0000C-         | 03   | *CC03         | *0C7CCC03 | 0C7CCC03_0C7C2000_20302E32_706F7250  |

| 0000D-         | CC   | CC03          | 0C7CCC03  | 0C7CCC03_0C7C2000_20302E32_706F7250  |

| 0000E-         | 7C   | *0C7C         | 0C7CCC03  | 0C7CCC03_0C7C2000_20302E32_706F7250  |

| 0000F-         | 0C   | 0C7C          | 0C7CCC03  | 0C7CCC03_0C7C2000_20302E32_706F7250  |

|                |      |               |           |                                      |

```

00010-

*0D7CC601 0C7CC601 0CFCB6E3 0DC1FE45

45

*FE45

*ODC1FE45

00011-

0D7CC601_0C7CC601_0CFCB6E3_0DC1FE45

FE

FE45

ODC1FE45

00012-

*0DC1

C1

ODC1FE45

0D7CC601_0C7CC601_0CFCB6E3_0DC1FE45

00013-

0D

0DC1

0DC1FE45

0D7CC601 0C7CC601 0CFCB6E3 0DC1FE45

00014-

*B6E3

0D7CC601 0C7CC601 0CFCB6E3 0DC1FE45

E3

*OCFCB6E3

00015-

В6

B6E3

OCFCB6E3

0D7CC601 0C7CC601 0CFCB6E3 0DC1FE45

00016-

FC

*OCFC

OCFCB6E3

0D7CC601 0C7CC601 0CFCB6E3 0DC1FE45

00017-

0C

0CFC

OCFCB6E3

0D7CC601_0C7CC601_0CFCB6E3_0DC1FE45

00018-

01

*C601

*0C7CC601

0D7CC601_0C7CC601_0CFCB6E3_0DC1FE45

00019-

C6

C601

0C7CC601

0D7CC601 0C7CC601 0CFCB6E3 0DC1FE45

0001A-

7C

*0C7C

0C7CC601

0D7CC601 0C7CC601 0CFCB6E3 0DC1FE45

0001B-

0C

0C7C

0C7CC601

0D7CC601_0C7CC601_0CFCB6E3_0DC1FE45

0001C-

*C601

0D7CC601 0C7CC601 0CFCB6E3 0DC1FE45

01

*0D7CC601

0001D-

C601

0D7CC601

0D7CC601_0C7CC601_0CFCB6E3_0DC1FE45

C6

0001E-

7C

*0D7C

0D7CC601

0D7CC601_0C7CC601_0CFCB6E3_0DC1FE45

0001F-

0D

0D7C

0D7CC601

0D7CC601 0C7CC601 0CFCB6E3 0DC1FE45

```

\* new word/long/quad

# PTRA/PTRB INSTRUCTIONS

-----

Each COG has two 17-bit pointers, PTRA and PTRB, which can be read, written, modified, and used to access HUB memory.

At COG startup, the PTRA and PTRB registers are initialized as follows:

```

PTRA = %X_XXXXXXXX_XXXXXXX, data from launching COG, usually a pointer

PTRB = %X_XXXXXXXX_XXXXXXX00, long address in HUB where COG code was loaded from

```

when COG starts, PTRA = PAR

PTRB = address of COG image

instructions clocks

000011 ZCR 1 CCCC DDDDDDDDD 000010010 GETPTRA D get PTRA into D, C = PTRA[16] 1

| 000011 | ZCR | 1 cccc | DDDDDDDDD | 000010011 | GETPTRB D  | get PTRB into D, C = PTRB[16] | 1 |

|--------|-----|--------|-----------|-----------|------------|-------------------------------|---|

| 000011 | 000 | 1 CCCC | DDDDDDDDD | 010110010 | SETPTRA D  | set PTRA to D                 | 1 |

| 000011 | 001 | 1 CCCC | nnnnnnnn  | 010110010 | SETPTRA #n | set PTRA to 0511              | 1 |

| 000011 | 000 | 1 CCCC | DDDDDDDDD | 010110011 | SETPTRB D  | set PTRB to D                 | 1 |

| 000011 | 001 | 1 CCCC | nnnnnnnn  | 010110011 | SETPTRB #n | set PTRB to 0511              | 1 |

|        |     |        |           |           |            |                               |   |

| 000011 | 000 | 1 CCCC | DDDDDDDDD | 010110100 | ADDPTRA D  | add D into PTRA               | 1 |

| 000011 | 001 | 1 CCCC | nnnnnnnn  | 010110100 | ADDPTRA #n | add 0511 into PTRA            | 1 |

| 000011 | 000 | 1 CCCC | DDDDDDDDD | 010110101 | ADDPTRB D  | add D into PTRB               | 1 |

| 000011 | 001 | 1 CCCC | nnnnnnnn  | 010110101 | ADDPTRB #n | add 0511 into PTRB            | 1 |

|        |     |        |           |           |            |                               |   |

| 000011 | 000 | 1 CCCC | DDDDDDDDD | 010110110 | SUBPTRA D  | subtract D from PTRA          | 1 |

| 000011 | 001 | 1 CCCC | nnnnnnnn  | 010110110 | SUBPTRA #n | subtract 0511 from PTRA       | 1 |

| 000011 | 000 | 1 CCCC | DDDDDDDDD | 010110111 | SUBPTRB D  | subtract D from PTRB          | 1 |

| 000011 | 001 | 1 cccc | nnnnnnnn  | 010110111 | SUBPTRB #n | subtract 0511 from PTRB       | 1 |

|        |     |        |           |           |            |                               |   |

QUAD-RELATED INSTRUCTIONS

-----

Each COG has four QUAD registers which form a 128-bit conduit between the HUB memory and the COG. This conduit can transfer four longs every 8 clocks via the WRQUAD/RDQUAD instructions. It can also be used as a 4-long/8-word/16-byte read cache, utilized by RDBYTEC/RDWORDC/RDLONGC/RDQUADC.

Initially hidden, these QUAD registers are mappable into COG register space by using the SETQUAD instruction to set an address where the base register is to appear, with the other three registers following. To hide the QUAD registers, use SETQUAD to set an address which is \$1F8, or higher.

SETQUAZ works just like SETQUAD, but also clears the four QUAD registers.

| instructions                                       |            |                                                          | clocks |

|----------------------------------------------------|------------|----------------------------------------------------------|--------|

| 000011 000 1 CCC 000000000 000001000               | CACHEX     | invalidate cache                                         | 1      |

| 000011 <b>Z01</b> 1 <b>CCCC DDDDDDDD</b> 000010001 | GETTOPS D  | get top bytes of QUADs into D (GETTOPS wc,nr = POLVID wc | 2) 1   |

| 000011 000 1 <b>CCCC DDDDDDDDD</b> 011100010       | SETQUAD D  | set QUAD base address to D                               | 1      |

| 000011 001 1 CCCC nnnnnnnn 011100010               | SETQUAD #n | set QUAD base address to 0511                            | 1      |

000011 010 1 CCCC DDDDDDDDDD 011100010 SETQUAZ D set QUAD base address to D and clears the QUAD registers. 1 set QUAD base address to 0..511 and clears the QUAD registers. 1

You can start the QUAD's at any register now and clear them at the same time, if you want.

HUB 'CONTROL INSTRUCTIONS

These instructions are used to control HUB circuits and cogs.

HUB instructions must wait for their COG's HUB cycle, which comes once every 8 clocks. In cases where there is no result to wait for (ZCR = %000), these instructions complete on the HUB cycle, making them take 1..8 clocks, depending on where the HUB cycle is in relation to the instruction. In cases where a result is anticipated (ZCR <> %000), these instructions complete on the 1st clock after the HUB cycle, making them take 2..9 clocks.

# COGINIT D,S

COGINIT is used to start cogs. Any COG can be (re)started, whether it is idle or running. A COG can even execute a COGINIT to restart itself with a new program.

COGINIT uses D to specify a long address in HUB memory that is the start of the program that is to be loaded into a COG, while S is a 17-bit parameter (usually an address) that will be conveyed to PTRA of the started COG. PTRB of the started COG will be set to the start address of its program that was loaded from HUB memory.

SETCOG must be executed before COGINIT to set the number of the COG to be started (0...7). If SETCOG sets a value with bit 3 set (%1xxx), this will cause the next idle COG to be started when COGINIT is executed, with the number of the COG started being returned in D, and the C flag returning 0 if okay, or 1 if no idle COG was available. Upon COG startup, SETCOG is initialized to %0000.

When a COG is started, \$1F8 contiguous longs are read from HUB memory and written to COG registers \$000..\$1F7. The COG will then begin execution at \$000. This process takes 1,016 clocks.

#### Example:

```

COGID

'what COG am I?

COGNUM

'set my COG number

SETCOG COGNUM

COGINIT COGPGM, COGPTR

'restart me with the ROM Monitor

'address of the ROM Monitor

COGPGM LONG

$0070C

tx = P90, rx = P91

COGPTR LONG

90 < < 9 + 91

COGNUM RES

'If you want to inspect hub memory after your program has run,

' just put the following code at the end of your program:

Code:

coginit monitor_pgm,monitor_ptr 'relaunch cog0 with monitor

monitor pqm long

'monitor program address

$70C

'monitor parameter (conveys tx/rx pins)

monitor ptr long

90<<9 + 91

'This will launch the ROM Monitor and let you view what your program did to hub memory.

' The monitor only affects the hub memory when you give it a command to do so. So, when

' the monitor starts up, hub memory is just as your program left it, ready to be inspected.

CLKSET D

CLKSET writes the lower 9 bits of D to the HUB clock register:

%R MMMM XX SS

R = 1 for hardware reset, 0 for continued operation

MMMM = PLL multiplying factor for XI pin input:

% 0000 for PLL disabled

% 0001..% 1111 for 2..16 multiply (XX must be set for XI input or XI/XO crystal oscillator)

MMMM = PLL mode:

```

```

% 0000 for disabled, else XX must be set for XI input or XI/XO crystal oscillator

% 0001 for multiply XI by 2

% 0010 for multiply XI by 3

% 0011 for multiply XI by 4

% 0100 for multiply XI by 5

% 0101 for multiply XI by 6

% 0110 for multiply XI by 7

% 0111 for multiply XI by 8

% 1000 for multiply XI by 9

% 1001 for multiply XI by 10

% 1010 for multiply XI by 11

% 1011 for multiply XI by 12

% 1100 for multiply XI by 13

% 1101 for multiply XI by 14

% 1110 for multiply XI by 15

% 1111 for multiply XI by 16

XX = XI/XO pin mode:

00 for XI

reads low, XO floats

01 for XI

input, XO floats

10 for XI/XO

crystal oscillator with 15pF internal loading and 1M-ohm feedback

crystal oscillator with 30pF internal loading and 1M-ohm feedback

11 for XI/XO

SS = Clock selector:

00 for RCFAST (~20MHz)

01 for RCSLOW (~20KHz)

10 for XTAL

(10MHz-20MHz)

11 for PLL

```

Because the the clock register is cleared to % 0\_0000\_00\_00 on reset, the chip starts up in RCFAST mode with both the crystal oscillator and the PLL disabled. Before switching to XTAL or PLL mode from RCFAST or RCSLOW, the crystal oscillator must be enabled and given 10ms to stabilize. The PLL stabilizes within 10us, 'so it can be enbled at the sime time as the crystal oscillator. Once the crystal is stabilized, you can switch between XTAL and RCFAST/RCSLOW without any stability concerns. If the PLL is also enabled, you can switch freely among PLL, XTAL, and RCFAST/RCSLOW modes. You can change the PLL multiplier while being in PLL mode, but beware that some frequency overshoot and undershoot will occur as the PLL settles to its 'new frequency. This only poses a hardware problem if you are switching upwards and the resulting overshoot 'might exceed the speed limit of the chip.

```

COGID D

------

COGID returns the number of the COG (0..7) into D.

COGSTOP D

-----

COGSTOP stops the COG specified in D (0..7).

LOCKNEW D

LOCKRET D

LOCKCLR D

------

```

There are eight semaphore locks available in the chip which can be borrowed with LOCKNEW, returned with LOCKRET, set with LOCKSET, and cleared with LOCKCLR.

While any COG can set or clear any lock without using LOCKNEW or LOCKNEW and LOCKRET are provided so that COG programs have a dynamic and simple means of acquiring and relinquishing the locks at run-time.

When a lock is set with LOCKSET, its state is set to 1 and its prior state is returned in C. LOCKCLR works the same way, but clears the lock's state to 0. By having the HUB perform the atomic operation of setting/clearing and reporting the prior state, cogs can utilize locks to insure that only one COG has permission to do something at once. If a lock starts out cleared and multiple cogs vie for the lock by doing a 'LOCKSET locknum wc', the COG to get C=0 back 'wins' and he can have exclusive access to some shared resource while the other cogs get C=1 back. When the winning COG is done, he can do a 'LOCKCLR locknum' to clear the lock and give another COG the opportunity to get C=0 back.

LOCKNEW returns the next available lock into D, with C=1 if no lock was free.

LOCKRET frees the lock in D so that it can be checked out again by LOCKNEW .

LOCKSET sets the lock in D and returns its prior state in C.

LOCKCLR clears the lock in D and returns its prior state in C.

| instructions            |                                  |          |                                  | clocks |

|-------------------------|----------------------------------|----------|----------------------------------|--------|

| 000011 ZCR 0 CCCC DDDDI | DDDDD SSSSSSSS CO                | INIT D,S | 'launch COG at D, COG PTRA = S   | 19     |

| 000011 000 1 CCCC DDDDI | <b>DDDDD</b> 000000000 <b>CL</b> | SET D    | 'set clock to D                  | 18     |

| 000011 001 1 CCCC DDDDI | DDDDD 000000001 CO               | ID D     | 'get COG number into D           | 29     |

| 000011 000 1 CCCC DDDDI | DDDDD 000000011 CO               | STOP D   | 'stop COG in D                   | 18     |

| 000011 ZC1 1 CCCC DDDDI | DDDDD 000000100 LO               | KNEW D   | 'get new lock into D, C = busy   | 29     |

| 000011 000 1 CCCC DDDDI | DDDDD 000000101 LO               | KRET D   | 'return lock in D                | 18     |

| 000011 0C0 1 CCCC DDDDI | DDDDD 000000110 LO               | KSET D   | 'set lock in D, C = prev state   | 19     |

| 000011 0C0 1 CCCC DDDDI | DDDDD 000000111 LO               | KCLR D   | 'clear lock in D, C = prev state | 19     |

#### 'INDIRECT REGISTERS

Each COG has two indirect registers: INDA and INDB. They are located at \$1F6 and \$1F7.

By using INDA or INDB for D or S, the register pointed at by INDA or INDB is addressed.

INDA and INDB each have three hidden 9-bit 'registers associated with them: the pointer, the bottom limit, and 'the top limit. The bottom and top limits are inclusive values which set automatic wrapping boundaries for the pointer. This way, circular buffers can be established within COG RAM and accessed using simple INDA/INDB references.

SETINDA/SETINDB is used to set or adjust the pointer value(S) while forcing the associated bottom and top limit(S) to \$000 and \$1FF, respectively.

FIXINDA/FIXINDB/FIXINDS sets the pointer(S) to an inital value, while setting the bottom limit(s) to the lower of the initial and terminal values and the top limit(S) to the higher.

'Because indirect addressing occurs very early in the pipeline and indirect pointers are affected earlier than the final stage where the conditional bit field (CCCC) normally comes into use, the CCCC field is repurposed for indirect operations. The top two bits of CCCC are used for indirect D and the bottom two bits are used

for indirect S . All 'instructions which use indirect registers will execute unconditionally, regardless of the CCCC 'bits.

Here is the INDA/INDB usage scheme which repurposes the CCCC field:

#### 000000 ZCR I CCCC DDDDDDDDD SSSSSSSS

```

xxxxxx xxx x 00xx 111110110 xxxxxxxxx

'use INDA

D = INDA

xxxxxx xxx x 00xx 111110111 xxxxxxxxx

D = INDB

'use INDB

xxxxxx xxx x 01xx 111110110 xxxxxxxxx

D = INDA++

'use INDA,

INDA += 1

xxxxxx xxx x 01xx 111110111 xxxxxxxxx

INDB += 1

D = INDB++

'use INDB,

xxxxxx xxx x 10xx 111110110 xxxxxxxxx

'use INDA,

INDA -= 1

D = INDA--

xxxxxx xxx x 10xx 111110111 xxxxxxxxx

D = INDB--

'use INDB

INDB -= 1

xxxxxx xxx x 11xx 111110110 xxxxxxxxx

INDA += 1

D = ++INDA

'use INDA+1,

xxxxxx xxx x 11xx 111110111 xxxxxxxxx

'use INDB+1,

INDB += 1

D = ++INDB

xxxxxx xxx 0 xx00 xxxxxxxxx 111110110

S = INDA

'use INDA

xxxxxx xxx 0 xx00 xxxxxxxxx 111110111

S = INDB

'use INDB

xxxxxx xxx 0 xx01 xxxxxxxxx 111110110

S = INDA++

'use INDA,

INDA += 1

xxxxxx xxx 0 xx01 xxxxxxxxx 111110111

S = INDB++

'use INDB,

INDB += 1

xxxxxx xxx 0 xx10 xxxxxxxxx 111110110

S = INDA--

'use INDA,

INDA -= 1

xxxxxx xxx 0 xx10 xxxxxxxxx 111110111

INDB -= 1

S = INDB--

'use INDB

xxxxxx xxx 0 xx11 xxxxxxxxx 111110110

S = ++INDA

'use INDA+1,

INDA += 1

xxxxxx xxx 0 xx11 xxxxxxxxx 111110111

S = ++INDB

'use INDB+1,

INDB += 1

```

If both D and S are the same indirect register, the two 2-bit fields in CCCC are OR'd together to get the post-modifier effect:

```

101000 001 0 0011 111110110 111110110 MOV INDA,++INDA 'Move @INDA+1 into @INDA, INDA += 1

100000 001 0 1100 111110111 111110111 ADD ++INDB,INDB 'Add @INDB into @INDB+1, INDB += 1

```

Note that only '++INDx,INDx'/'INDx,++INDx' combinations can address different registers from the same INDx.

Here are the instructions which are used to set the pointer and limit values for INDA and INDB:

```

instructions * clocks Descrinption

```

\_\_\_\_\_

```

| 'Set or adjust the pointer value(s) while forcing

111000 000 0 0001 000000000 AAAAAAAA

SETINDA #addrA

111000 000 0 0011 000000000 AAAAAAAA

SETINDA ++/--deltA

' the associated bottom and top limit(s)

' to $000 and $1FF, respectively.

111000 000 0 0100 BBBBBBBB 000000000

SETINDB #addrB

* addrA/addrB/terminal/initial

SETINDB ++/--deltB

111000 000 0 1100 BBBBBBBB 000000000

' = register address (0..511),

1

' deltA/deltB = 9-bit signed delta --256..++255

111000 000 0 0101 BBBBBBBB AAAAAAAA

SETINDS #addrB,#addrA

1

111000 000 0 0111 BBBBBBBB AAAAAAAA

SETINDS #addrB,++/--deltA

1

AAAAAAAA

addrA

SETINDS ++/--deltB,#addrA

111000 000 0 1101 BBBBBBBB AAAAAAAA

1

BBBBBBBB

addrB

111000 000 0 1111 BBBBBBBB AAAAAAAA

SETINDS ++/--deltB,++/--deltA

terminal

1

TTTTTTTTT

IIIIIIII initial

111001 000 0 0001 TTTTTTTT IIIIIII

FIXINDA #terminal, #initial

1

111001 000 0 0100 TTTTTTTT IIIIIIII

FIXINDB #terminal, #initial

111001 000 0 0101 TTTTTTTT IIIIIIII

FIXINDS #terminal, #initial

1

```

\* addrA/addrB/terminal/initial = register address (0..511), deltA/deltB = 9-bit signed delta --256..++255

#### INDIRECT POINTER Examples:

```

111000 000 0 0001 000000000 000000101

SETINDA #5

'INDA = 5, bottom = 0, top = 511

111000 000 0 0011 000000000 000000011

SETINDA ++3

'INDA += 3, bottom = 0, top = 511

111000 000 0 1100 1111111100 000000000

SETINDB --4

'INDB -= 4, bottom = 0, top = 511

111000 000 0 0111 000000111 000001000

SETINDS #7,++8

'INDB = 7, INDA += 8, bottoms = 0, tops = 511

'INDA = 8, bottom = 8, top = 15

111001 000 0 0001 000001111 000001000

FIXINDA #15,#8

111001 000 0 0100 000010000 000011111

FIXINDB #16,#31

'INDB = 31, bottom = 16, top = 31

111001 000 0 0101 001100011 000110010

FIXINDS #99,#50

'INDA/INDB = 50, bottoms = 50, tops = 99

```

#### STACK RAM

\_\_\_\_\_

When the video generator is **not** in use the **CLUT/RAM** may be used as a general-purpose **memory** scratch space, **or** as a 256 **Long** FIFO buffer, **or** as a **call stack and** evaluation **stack (at** the **same** time).

The **CLUT/RAM** has two pointers used to **index** it called **SPA** and **SPB**.

Each COG has a 256-long STACK RAM that is accessible via push and pop operations.

```

There are two STACK pointers called SPA and SPB which are used to address the STACK memory.

' Aside from automatically incrementing and decrementing on pushes and pops,

SPA and SPB 'can be set, added to, subtracted from, read back, and checked:

SETSPA D/#n

set SPA

SETSPB D/#n

set SPB

ADDSPA D/#n

add to SPA

ADDSPB D/#n

add to SPB

SUBSPA D/#n

subtract from SPA

SUBSPB D/#n

subtract from SPB

GETSPA D

get SPA, SPA==0 into Z, SPA.7 into C

get SPB, SPB==0 into Z, SPB.7 into C

GETSPB D

get SPA minus SPB, SPA==SPB into Z, SPA<SPB into C

GETSPD D

CHKSPA

check SPA, SPA==0 into Z, SPA.7 into C

CHKSPB

check SPB, SPB==0 into Z, SPB.7 into C

CHKSPD

check SPA minus SPB, SPA==SPB into Z, SPA<SPB into C

'Data can be pushed and popped in both normal and reverse directions:

PUSHA

D/#n

push using SPA

D/#n

PUSHB

push using SPB

PUSHAR D/#n

push using SPA, use pop addressing

PUSHBR D/#n

push using SPB, use pop addressing

POPA

pop using SPA

D

POPB

D

pop using SPB

POPAR

D

pop using SPA, use push addressing

POPBR

pop using SPB, use push addressing

'Aside from data, the program counter and flags can be pushed and popped using calls and returns:

CALLA

D/#n

call using SPA

CALLB

D/#n

call using SPB

CALLAD D/#n

call using SPA,

'delay branch until three trailing instructions executed

CALLBD D/#n

call using SPB,

'delay branch until three trailing instructions executed

RETA

return using SPA

RETB

return using SPB

RETAD

return using SPA, 'delay branch until three trailing instructions executed

RETBD

return using SPB, 'delay branch until three trailing instructions executed

```

The STACK RAM's contents are undefined at COG start.

| instructions (STACK RAM access is shown as [S       | SPx++] <b>and [</b> SP: | x]) clocks                                                                                                                                                                                                        |

|-----------------------------------------------------|-------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 000011 <b>zco</b> 1 <b>cccc</b> 000000000 000010101 | CHKSPD                  | SPA==SPB into Z, SPA <spb 1<="" c="" into="" th=""></spb>                                                                                                                                                         |

| 000011 <b>ZC1</b> 1 <b>CCCC DDDDDDDD</b> 000010101  | GETSPD D                | SPA-SPB into D, Z/C as CHKSPD 1 'Stores ((SPA - SPB) & 0x7F) in register "D (0-511)". FOR FIFO MODE.                                                                                                              |

| 000011 <b>ZCO</b> 1 <b>CCCC</b> 000000000 000010110 | CHKSPA                  | SPA==0 into Z, SPA.7 into C 1                                                                                                                                                                                     |

| 000011 <b>ZC1</b> 1 <b>CCCC DDDDDDDD</b> 000010110  | GETSPA D                | SPA into D, Z/C as CHKSPA 1 'Stores SPA in register "D (0-511)".                                                                                                                                                  |

| 000011 <b>zc0</b> 1 <b>cccc</b> 000000000 000010111 | CHKSPB                  | SPB==0 into Z, SPB .7 into C 1                                                                                                                                                                                    |

| 000011 <b>ZC1</b> 1 <b>CCCC DDDDDDDD</b> 000010111  | GETSPB D                | SPB into D, Z/C as CHKSPB 1 'Stores SPB in register "D (0-511)".                                                                                                                                                  |

| 000011 <b>ZC1</b> 1 <b>CCCC DDDDDDDD</b> 000011000  | POPAR D                 | <pre>read [SPA++] into D, MSB into C 1 'Store CLUT[SPA] in register "D (0-511)" and then increment SPA.</pre>                                                                                                     |

| 000011 <b>ZC1</b> 1 <b>CCCC DDDDDDDD</b> 000011001  | POPBR D                 | read [SPB++] into D, MSB into C 1  'Store CLUT[SPB] in register "D (0-511)" and then increment SPA.                                                                                                               |

| 000011 <b>ZC1</b> 1 <b>CCCC DDDDDDDD</b> 000011010  | POPA D                  | <pre>read [SPA] into D, MSB into C 1 'Decrement SPA and then store CLUT[SPA] in register "D (0-511)".</pre>                                                                                                       |

| 000011 <b>ZC1</b> 1 <b>CCCC DDDDDDDD</b> 000011011  | POPB D                  | read [SPB] into D, MSB into C 1 'Decrement SPB and then store CLUT[SPB] in register "D (0-511)".                                                                                                                  |

| 000011 ZCO 1 CCCC 000000000 000011100               | RETA                    | read [SPA] into Z/C/PC*  'Decrement SPA and then jump to instruction (CLUT[SPA] & 0x1FF).                                                                                                                         |

| 000011 <b>ZCO</b> 1 <b>CCCC</b> 000000000 000011101 | RETB                    | 'Flush pipeline before jump - results in a two-cycle loss.  read [SPB] into Z/C/PC*  'Decrement SPB and then jump to instruction (CLUT[SPB] & 0x1FF).  'Flush pipeline before jump - results in a two-cycle loss. |

| 000011 <b>zco</b> 1 <b>cccc</b> 000000000 000011110 | RETAD                   | read [SPA] into Z/C/PC* 1 'Decrement SPA and then jump to instruction (CLUT[SPA] & 0x1FF).                                                                                                                        |

| 000011 <b>zc0</b> 1 <b>cccc</b> 000000000 000011111 | RETBD         | 'Do not flush pipeline before jump - must be executed two 'instructions before intended jump space.  read [SPB] into Z/C/PC* 1 'Decrement SPB and then jump to instruction (CLUT[SPB] & 0x1FF). 'Do not flush pipeline before jump - must be executed two 'instructions before intended jump space. |

|-----------------------------------------------------|---------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 000011 000 1 CCCC DDDDDDDDD 010100010               | SETSPA D      | set SPA to D 1                                                                                                                                                                                                                                                                                      |

|                                                     |               | 'Set SPA to register "D (0-511)".                                                                                                                                                                                                                                                                   |

| 000011 001 1 CCCC 0nnnnnnnn 010100010               | SETSPA #n     | set SPA to n 1                                                                                                                                                                                                                                                                                      |

|                                                     |               | 'Set SPA to register "n (0-511)".                                                                                                                                                                                                                                                                   |

| 000011 000 1 CCCC DDDDDDDDD 010100011               | SETSPB D      | set SPB to D 1                                                                                                                                                                                                                                                                                      |

|                                                     |               | 'Set SPB to register "D (0-511)".                                                                                                                                                                                                                                                                   |

| 000011 001 1 CCCC 0nnnnnnnn 010100011               | SETSPB #n     | set SPB to n 1                                                                                                                                                                                                                                                                                      |

|                                                     |               | 'Set SPB to register "n (0-511)".                                                                                                                                                                                                                                                                   |

| 000011 000 1 CCCC DDDDDDDDD 010100100               | ADDSPA D      | add D into SPA 1                                                                                                                                                                                                                                                                                    |

|                                                     |               | 'Add to SPA register "D (0-511)"                                                                                                                                                                                                                                                                    |

| 000011 001 1 CCCC 0nnnnnnnn 010100100               | ADDSPA #n     | add n into SPA 1                                                                                                                                                                                                                                                                                    |

|                                                     |               | 'Add to SPA register "n (0-511)"                                                                                                                                                                                                                                                                    |

| 000011 000 1 CCCC DDDDDDDDD 010100101               | ADDSPB D      | add D into SPB 1                                                                                                                                                                                                                                                                                    |

|                                                     |               | 'Add to SPB register "D (0-511)"                                                                                                                                                                                                                                                                    |

| 000011 001 1 CCCC 0nnnnnnnn 010100101               | ADDSPB #n     | add n into SPB 1                                                                                                                                                                                                                                                                                    |

|                                                     |               | 'Add to SPB register "n (0-511)"                                                                                                                                                                                                                                                                    |

| 000011 000 1 CCCC DDDDDDDD 010100110                | SUBSPA D      | subtract D from SPA 1                                                                                                                                                                                                                                                                               |

|                                                     | -             | 'Subtract from SPA register "D (0-511)"                                                                                                                                                                                                                                                             |

| 000011 001 1 CCCC 0nnnnnnnn 010100110               | SUBSPA #n     | subtract n from SPA 1                                                                                                                                                                                                                                                                               |

|                                                     |               | 'Subtract from SPA register "n (0-511)"                                                                                                                                                                                                                                                             |

| 000011 000 1 CCCC DDDDDDDDD 010100111               | SUBSPB D      | subtract D from SPB 1                                                                                                                                                                                                                                                                               |

|                                                     |               | 'Subtract from SPB register "D (0-511)"                                                                                                                                                                                                                                                             |

| 000011 001 1 CCCC 0nnnnnnnn 010100111               | SUBSPB #n     | subtract <b>n</b> from SPB 1                                                                                                                                                                                                                                                                        |

|                                                     |               | 'Subtract from SPB register "n (0-511)"                                                                                                                                                                                                                                                             |

| 000011 000 1 CCCC DDDDDDDDD 010101000               | PUSHAR D      | write D into [SPA] 1 **                                                                                                                                                                                                                                                                             |

| 000011 000 1 0000 00000000 010101000                | 20011111      | 'Decrement SPA and then store register "D (0 511)"                                                                                                                                                                                                                                                  |

| 000011 001 1 <b>CCCC nnnnnnnn</b> 010101000         | PUSHAR #n     | write n into [SPA] 1 **                                                                                                                                                                                                                                                                             |

|                                                     | 2 002224 1122 | 'Decrement SPA and then store register "n (0 511)"                                                                                                                                                                                                                                                  |

| 000011 000 1 CCCC DDDDDDDDD 010101001               | PUSHBR D      | write D into [SPB] 1 **                                                                                                                                                                                                                                                                             |

|                                                     |               |                                                                                                                                                                                                                                                                                                     |

|                                             |          |    | 'Decrement SPB and then store register "D (0-511)"               |

|---------------------------------------------|----------|----|------------------------------------------------------------------|

| 000011 001 1 CCCC nnnnnnnn 010101001        | PUSHBR   | #n | write n into [SPB] 1 **                                          |

|                                             |          |    | 'Decrement SPB and then store register "n (0-511)"               |

| 000011 000 1 CCCC DDDDDDDD 010101010        | PUSHA    | D  | write D into [SPA++] 1 **                                        |

|                                             |          |    | 'Store register "D (0-511)" in CLUT[SPA] and then increment SPA. |

| 000011 001 1 <b>CCCC nnnnnnnn</b> 010101010 | PUSHA    | #n | write n into [SPA++] 1 **                                        |

| 000011 001 1 0000 111111111111111111111     |          |    | 'Store register "n (0-511)" in CLUT[SPA] and then increment SPA. |

| 000011 000 1 CCCC DDDDDDDDD 010101011       | PUSHB    | D  | write D into [SPB++] 1 **                                        |

|                                             |          |    | 'Store register "D (0-511)" in CLUT[SPB] and then increment SPB. |

| 000011 001 1 CCCC nnnnnnnn 010101011        | PUSHB    | #n | write n into [SPB++] 1 **                                        |

| 000011 001 1 0000 1                         | 1 00112  | "  | 'Store register "n (0-511)" in CLUT[SPB] and then increment SPB. |

|                                             |          |    |                                                                  |

| 000011 000 1 CCCC DDDDDDDDD 010101100       | CALLA    | D  | write Z/C/PC* into [SPA++], PC=D 4 **                            |

|                                             |          |    | 'Store the program counter (PC) in CLUT[SPA] and then increment  |

|                                             |          |    | ' SPA and then jump to the address in register "D (0-511)"       |

| 000011 001 1 <b>CCCC nnnnnnnn</b> 010101100 | CALLA    | #n | <pre>write Z/C/PC* into [SPA++], PC=n 4 **</pre>                 |

|                                             |          |    | 'Store the program counter (PC) in CLUT[SPA] and then increment  |

|                                             |          |    | ' SPA and then jump to the address in register "n (0-511)".      |

|                                             |          |    | ' Flush pipeline before jump - results in a two-cycle loss.      |

| 000011 000 1 CCCC DDDDDDDDD 010101101       | CALLB    | D  | write Z/C/PC* into [SPB++], PC=D 4 **                            |

|                                             |          |    | 'Store the program counter (PC) in CLUT[SPB] and then increment  |

|                                             |          |    | ' SPB and then jump to the address in register "D (0-511)"       |

| 000011 001 1 <b>CCCC nnnnnnnn</b> 010101101 | CALLB    | #n | write Z/C/PC* into [SPB++], PC=n 4 **                            |

|                                             |          |    | 'Store the program counter (PC) in CLUT[SPB] and then increment  |

|                                             |          |    | ' SPB and then jump to the address in register "n (0-511)".      |

|                                             |          |    | ' Flush pipeline before jump - results in a two-cycle loss.      |

| 000011 000 1 CCCC DDDDDDDD 010101110        | CALLAD   | D  | write Z/C/PC* into [SPA++], PC=D 1 **                            |

| 000011 000 1 0000 2222222 010101110         | 01111111 |    | 'Store the program counter (PC) in CLUT[SPA] and then increment  |

|                                             |          |    | ' SPA and then jump to the address in register "D (0-511)"       |

| 000011 001 1 <b>CCCC nnnnnnnn</b> 010101110 | CALLAD   | #n | write Z/C/PC* into [SPA++], PC=n 1 **                            |

| 000011 001 1 0000                           | 01111111 |    | 'Store the program counter (PC) in CLUT[SPA] and then increment  |

|                                             |          |    | ' SPA and then jump to the address in register "n (0-511)"       |

| 000011 000 1 CCCC DDDDDDDDD 010101111       | CALLBD   | D  | write Z/C/PC* into [SPB++], PC=D 1 **                            |

| 000011 000 1 0000 0000000 010101111         |          | _  | 'Store the program counter (PC) in CLUT[SPB] and then increment  |

|                                             |          |    | ' SPB and then jump to the address in register "D (0-511)"       |

| 000011 001 1 <b>CCCC nnnnnnnn</b> 010101111 | CALLBD   | #n | write Z/C/PC* into [SPB++], PC=n 1 **                            |

| 000011 001 1 0000                           |          |    | 'Store the program counter (PC) in CLUT[SPB] and then increment  |

|                                             |          |    | 20010 0110 F1051am Counted (10, 111 Chorista) and onen increment |

'SPB and then jump to the address in register "n (0-511)"

\* bit 10 is Z, bit 9 is C, bits 8..0 are PC, upper bits are ignored or cleared

\*\* if a STACK RAM write is immediately followed by a STACK RAM read, add one clock

#### BYTE/WORD FIELD MOVER

-----

Each COG has a field mover that can move a byte or word from any field in S into any field in D . To use the field mover, you must first configure it using SETF. Then, you can use MOVF to perform the moves.

SETF uses a 9-bit value to configure the field mover:

%W\_DDdd\_SSss

```

W = 1 for word mode, 0 for byte mode

DD = D field mode:

%00 = D field pointer stays same after MOVF

%01 = D field pointer stays same after MOVF, D rotates left by byte/word

%10 = D field pointer increments after MOVF

%11 = D field pointer decrements after MOVF

dd = D field pointer: %00 = byte 0 / word 0

%01 = byte 1 / word 0

%10 = byte 2 / word 1

%11 = byte 3 / word 1

SS = S field mode:

%0x = S field pointer stays same after MOVF

%10 = S field pointer increments after MOVF

%11 = S field pointer decrements after MOVF

ss = S field pointer: %00 = byte 0 / word 0

%01 = byte 1 / word 0

%10 = byte 2 / word 1

%11 = byte 3 / word 1

```

On COG startup, SETF is initialized to %0\_0100\_0000, so that MOVF will rotate D left by 8 bits and then fill the bottom byte with the lower byte in S.

| instruct | tions |      |           |           |      |      | clock                            | ເຮ          |

|----------|-------|------|-----------|-----------|------|------|----------------------------------|-------------|

| 000011   | 000 1 | CCCC | Wddddssss | 011001010 | SETF | D    | 'Configure field mover with D    | 1           |

| 000011   | 001 1 | CCCC | nnnnnnnn  | 011001010 | SETF | #n   | 'Configure field mover with 0511 | 1           |

| 000101   | 000 0 | CCCC | DDDDDDDDD | SSSSSSSS  | MOVF | D,S  | 'Move field from S into D        | 1           |

| 000101   | 000 1 | CCCC | DDDDDDDDD | nnnnnnnn  | MOVF | D,#n | 'Move field from 0511 into D     | 1           |

| 000101   | 000 1 | CCCC | DDDDDDDDD | nnnnnnnn  | MOVF | D,#n | 'Move field from                 | 0511 into D |

\_\_\_\_\_\_

#### MULTI-TASKING

-----

Each COG has four sets of flags and program counters (Z/C/PC), constituting four unique Tasks that can execute and switch on each instruction cycle.

'At COG startup, the tasks are initialized as follows:

# TASK Z C PC 0 0 0 \$000 1 0 0 \$001 2 0 0 \$002 3 0 0 \$003

There are 16 rotating time slots in the TASK register that determine TASK sequence. Initially, all time slots are set to 0, causing TASK 0 to execute exclusively, starting at address \$000:

time slots: 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

The two LSB's of TASK always determine which TASK will execute next. After each instruction cycle, the TASK register is rotated right by two bits, recycling slot 0 to slot 15 and getting the next TASK into the 2 LSB's.

To enable other Tasks, SETTASK is used to set the TASK register:

```

SETTASK D write D to the TASK register

SETTASK #n write {n[7:0], n[7:0], n[7:0]} to the TASK register

```

If a TASK is given no time slot, it doesn't execute and its flags and PC stay at initial values.

If a TASK is given a time slot, it will execute and its flags and PC will be updated at every instruction, or time slot. If an active TASK's time slots are all taken away, that TASK's flags and PC remain in the state where they left off, until it is given another time slot.

To immediately force any of the **four PC's to a new address**, **JMPTASK can be used. JMPTASK uses** a **4-bit mask** to select which **PC**'s are going to be written. Mask bits 0..3 represent PC's 0..3.

The **mask** value %1010 would **write PC** 3 and **PC** 1, **while** %0100 would **write PC** 2, only.

```

JMPTASK D, #mask force PC's in mask to D

JMPTASK #addr, #mask force PC's in mask to #addr

```

For every PC/TASK affected by a JMPTASK instruction, all affected-TASK instructions currently in the pipeline are cancelled. This insures that once JMPTASK executes, the next instruction from each affected TASK will be from the new address.

#### **JMPTASK**

'There are 4 program counters in each cog. They are initialized as follows:

```

PC0 = $000

PC1 = $001

```

PC2 = \$002

PC3 = \$003

```

'At first, the task register, which is 32 bits (16 two-bit fields), is cleared to 0,

' making all time slots execute task0.

JMPTASK sets up to all four PC's at once, using a bit field in S and an address in D.

JMPTASK #substart, #%1111 ... would set all PC's to substart

JMPTASK #substart, #%1000 ... would set PC3 to substart

JMPTASK #substart, #%0100 ... would set PC2 to substart

JMPTASK #substart, #%0010 ...would set PC1 to substart

JMPTASK #substart, #%0001 ... would set PC0 to substart

'Until SETTASK is executed (initialized to $00000000), only PCO is running, making the cog seem normal.

SETTASK #%%3210 ... 'would enable all tasks. If no JMPTASK was done,

'would begin execution from $001..$003 (better have some

JMP's there)

'When you do an immediate SETTASK #, the lower 8 bits of immediate data are replicated four times to fill 32 bits.

' To get more granularity, you could do a register, instead of an immediate,

' and 32 unique bits would be loaded into the task register, which rotates right after each instruction completion,

with the 2 LSB's determining which task to execute next.

Here is an example in which all four tasks are started and each TASK toggles an I/O pin at a

different rate:

```

#### ORG

|       | JMP         | #task0       | 'TASK  | 0  | begins  | here   | when   | the C           | OG  | starts (  | this JMP  | takes   | 4 c   | locks) |     |          |

|-------|-------------|--------------|--------|----|---------|--------|--------|-----------------|-----|-----------|-----------|---------|-------|--------|-----|----------|

|       | JMP         | #task1       | 'TASK  | 1  | begins  | here   | after  | TASK            | 0   | executes  | SETTASK   | (this   | JMP   | takes  | 1   | clock)   |

|       | JMP         | #task2       | 'TASK  | 2  | begins  | here   | after  | TASK            | 0   | executes  | SETTASK   | (this   | JMP   | takes  | 1   | clock)   |

|       | JMP         | #task3       | 'TASK  | 3  | begins  | here   | after  | TASK            | 0   | executes  | SETTASK   | (this   | JMP   | takes  | 1   | clock)   |

| task0 | SETTASK     | #%%3210      | 'enabl | Le | all ta  | sks (' | TASK = | * <b>%11_</b> : | 10_ | _01_00_11 | _10_01_00 | )_11_1( | 0_01_ | _00_11 | _1( | 0_01_00) |

| :loop | NOTP<br>JMP | #0<br>#:loop |        | _  | , toggl | _      |        | •               | oor | os every  | 8 clocks) | )       |       |        |     |          |

| task1 | NOTP<br>NOP | #1     | 'TASK 1, toggle pin 1     | (loops every 12 clocks) |

|-------|-------------|--------|---------------------------|-------------------------|

|       | JMP         | #task1 | '(this JMP takes 1 clock) |                         |

| task2 | NOTP        | #2     | 'TASK 2, toggle pin 2     | (loops every 16 clocks) |

|       | NOP         |        |                           |                         |

|       | NOP         |        |                           |                         |

|       | JMP         | #task2 | '(this JMP takes 1 clock) |                         |

| task3 | NOTP        | #3     | 'TASK 3, toggle pin 3     | (loops every 20 clocks) |

|       | NOP         |        |                           |                         |

|       | NOP         |        |                           |                         |

|       | NOP         |        |                           |                         |

|       | JMP         | #task3 | '(this JMP takes 1 clock) |                         |

NOTE: When a married househ instruction (TIP CALL DEF etc.) asserted in the fourth and final above of the

NOTE: When a normal branch instruction (JMP, CALL, RET, etc.) executes in the fourth and final stage of the pipeline, all instructions progressing through the lower three stages, which belong to the same TASK as the 'branch instruction, are cancelled. This inhibits execution of incidental data that was trailing the branch 'instruction.

The delayed branch instructions (JMPD, CALLD, RETD, etc.) don't do any pipeline instruction cancellation and exist to provide 1-clock branches to Single-Task programs, where the three instructions following the branch 'are allowed to execute before the new instruction stream begins to execute.

For Single-Task programs, normal branches take 4 clocks: 1 clock for the branch and 3 clocks for the 'cancelled instructions to come through the pipeline before the new instruction stream begins to execute.

For multi-tasking programs that use all four tasks in sequence (ie SETTASK #%%3210), there are never any Same-Task instructions in the pipeline that would require cancellation due to branching, so all branches take just 1 clock.

-----

Tips for coding multi-tasking programs

While all tasks in a multi-tasking program can execute atomic instructions without any Inter-Task conflict, remember that there's only one of each of the following COG resources and only one TASK can use it at a time:

```

SPA

SPB

INDA

INDB

PTRA

PTRB

ACCA

ACCB

32x32

multiplier

64/32

divider

64-bit

square rooter

CORDIC

computer

CTRA

CTRB

VID

PIX

(not usable in multi-tasking, requires single-task timing)

XFR

SER

I got the REPS/REPD working with multitasking now.

REPS/REPD

Any task can use it, but only one task at a time.

Bitfield mover

Using REPS with 511 for the loop count means loop forever,

so it should only fall out when the repeated section does a jmp/call .

```

When writing multi-task programs, be aware that instructions that take multiple clocks will stall the pipeline and have a ripple effect on the tasks' timing. This may be impossible to avoid, as some task might need to access HUB memory, and those instructions are not single-clock.

The WAITCNT/WAITPEQ/WAITPNE instructions should be recoded discretely using 1-clock instructions, to avoid stalling the pipeline for excessive amounts of time.

The following instructions (WC versions) will take 1 clock, instead of potentially many, and return 1 in C if they were successful:

SNDSER D WC

```

attempt to receive serial

RCVSER D WC

000011 ZCR 1 CCCC DDDDDDDDD 000110000

GETMULL D WC

attempt to get lower multiplier result (waits for mul if !wc)

attempt to get upper multiplier result (waits for mul if !wc)

000011 ZCR 1 CCCC DDDDDDDDD 000110001

GETMULH D WC

000011 ZCR 1 CCCC DDDDDDDDD 000110010

attempt to get divider quotient result (waits for div if !wc)

GETDIVQ D WC

000011 ZCR 1 CCCC DDDDDDDDD 000110011

GETDIVR D WC

attempt to get divider remainder result (waits for div if !wc)

000011 ZCR 1 CCCC DDDDDDDDD 000110100

attempt to get square root result

(waits for sqrt if !wc)

GETSORT D WC

000011 ZCR 1 CCCC DDDDDDDDD 000110101

attempt to get CORDIC X result

(waits for cordic if !wc)

GETOX

D WC

000011 ZCR 1 CCCC DDDDDDDDD 000110110

GETQY D WC

attempt to get CORDIC Y result

(waits for cordic if !wc)

000011 ZCR 1 CCCC DDDDDDDDD 000110111

attempt to get CORDIC Z result

(waits for cordic if !wc)

GETOZ D WC

```

#### 'Other instruction alternatives:

```

POLCTRA WC returns 1 in C if CTRA rolled over, use instead of SYNCTRA

POLCTRB WC returns 1 in C if CTRB rolled over, use instead of SYNCTRB

POLVID WC returns 1 in C if WAITVID is ready, use to execute WAITVID without stalling

000011 ZC0 1 CCCC DDDDDDDDDD 000001101 PASSCNT D (loops if (cnt[31:0] - D) msb set)

jumps to itself if some amount of time has not passed, use instead of WAITCNT

```

\_\_\_\_\_

The following instructions will **not** work **in** a **Multi-Tasking** program:

attempt to send serial

GETPIX needs steady pipeline delays for perspective divider time - Single-Task only

```

| Clocks | C

```

PIPELINE

-----

Each COG has a 4-stage pipeline which all instructions progress through, in order to execute:

```

1st stage - Read instruction

2nd stage - Determine indirect/remapped D and S addresses, update INDA/INDB

3rd stage - Read D and S

4th stage - Execute instruction, write D, Z/C/PC, and any other results

```

On every clock cycle, the instruction in each stage advances to the next stage, unless the instruction in the 4th stage is stalling the pipeline because it's waiting for something (i.e. WRBYTE waits for the HUB).

To keep D and S data current within the pipeline, the resultant D from the 4th stage is passed back to the 3rd stage to substitute for any obsoleted data being read from the COG register RAM. The same is done for instruction data in the 1st stage, but there is still a two-stage gap between when a register is modified and when it can be executed:

```

MOVD :inst,top9 'modify instruction

NOP '1...

NOP '2... at least two instructions in-between

inst ADD A,B 'modified instruction executes

```

Tasks that execute in at least every 3rd time slot don't need to observe this 2-instruction rule because their instructions will always be sufficiently spread apart in the pipeline.

When a branch instruction executes, all instructions in the pipeline belonging to that same task are cancelled, as the program counter has changed, rendering those instructions that were following the branch instruction invalid. A new instruction stream, beginning at the new PC value, must make its way through the pipeline before another instruction from that task will execute. For single-task programs, this means that branches take 4 clocks: 1 for the branch, and 3 for the cancelled instructions in stages 1..3 to make their way through the pipeline before the new instruction stream reaches the execution stage. For multi-tasking programs, branch delays are a function of time slot allocation.

## INSTRUCTION-BLOCK REPEATING

-----

Each **cog** has an instruction-block repeater that can variably **repeat** up to 64 instructions without any clock-cycle overhead.

**REPD and REPS** are used to initiate block repeats. These instructions specify how many **times** the trailing instruction block will be executed **and** how many instructions are **in** the block:

```

REPD #i - execute 1..64 instructions infinitely, requires 3 spacer instructions *

REPD D,#i - execute 1..64 instructions D+1 times, requires 3 spacer instructions *

REPD #n,#i - execute 1..64 instructions 1..512 times, requires 3 spacer instructions *

REPS #n,#i - execute 1..64 instructions 1..16384 times, requires 1 spacer instruction *

```

REPS differs from REPD by executing at the 2nd stage of the pipeline, instead of the 4th. By executing two stages early, it needs only one spacer instruction \*. Because of its earliness, no conditional execution is possible, so it always executes, allowing the CCCC bits to be repurposed, along with Z, to provide a 14-bit constant for the repeat count.

The instruction-block repeater will quit repeating the block **if** a branch instruction executes within the block. **This** rule does **not** currently apply to a **JMPTASK** which affects the **task** using the repeater - **this** will be fixed **at** the earliest opportunity.

\* Spacer instructions are required in 1-task applications to allow the pipeline to prime before repeating can commence. If REPD is used by a task that uses no more than every 4th time slot, no spacers are needed, as three intervening instructions will be provided by the other task(s). If REPS is used by a task that uses no more than every 2nd time slot, no spacers are needed.

# Example (1-task):