# **Open Preamplifier**

# **Preliminary specification**

Version 0.1

Last edited: 3/11/07 By: DEP

> By: Dave Paton Chris Savage Junkie

| 1   | Overview and Distribution | 3            | 3 |

|-----|---------------------------|--------------|---|

| 2   | Motherboard               | 3            | 3 |

| 2.1 | Design philosophy         | 3            | 3 |

| 2.2 | Physical specification    | 3            | 3 |

| ,   | 1 Connectors              | 3            | 3 |

| 2.3 | Electrical Specification  | 3            | 3 |

| ,   | 1 Signal Bus              | 3            | 3 |

|     | .3.1.1 Input Buffering    | 5            | 5 |

|     | .3.1.2 Switching          | 5            | 5 |

|     | .3.1.3 Level control      | 5            | 5 |

|     | .3.1.4 Output Buffering   | 5            | 5 |

|     | 2 Control Bus             | 5            | 5 |

|     | .3.2.1 Serial Control     | 5            | 5 |

|     | .3.2.2 Bitwise Control    | 5            | 5 |

|     | 3 Power Supply Bus        | 5            | 5 |

|     | .3.3.1 Supply 1: +/-15VDC |              |   |

|     | .3.3.2 Supply 2 +/-xxVDC  | 5            | 5 |

|     | .3.3.3 Supply 3 +5VDC     | 5            | 5 |

|     | .3.3.4 Grounding          | <i>6</i>     | 5 |

| 3   | Module Boards             | 6            | 5 |

| 3.1 | Design philosophy         | 6            | 5 |

| 3.2 | Physical specification    | 6            | 5 |

|     | 1 Connectors              | 6            | 5 |

| 3.3 | Electrical Specification  | <del>6</del> | 5 |

| 4   | Design Software           |              | 7 |

| 4.1 | Schematic Capture         |              | 7 |

| 4   | 1 EAGLE                   |              | 7 |

| 4.2 | PCB Layout                |              | 7 |

| 4   | 1 EAGLE                   |              | 7 |

| 5   | Control                   |              | 7 |

| 5.1 | Microcontroller selection |              | 7 |

| :   | 1 BASIC Stamp             |              |   |

| :   | 2 Parallax SX             |              |   |

| :   | 3 Parallax Propeller      |              | 7 |

| :   | 4 Atmel AVR               |              |   |

| :   | 5 Microchip PIC           |              |   |

| :   | 6 Intel 8051 family       |              | 7 |

| :   | 7 Other                   |              | 7 |

#### 1 Overview and Distribution

The OpenPreamp is designed to be modular, expandable, extensible, and easy to build and work on. It should be a platform for experimentation and a source of high quality audio for its user. It is intended as a learning tool and for private home use. Incorporation of concepts into commercial products is permissible, but wholesale copying in part or in whole for private commercial gain is prohibited. If you want to make kits, do it for the cost of making the kits. Anything beyond a small profit to cover the time invested in distributing the kids is selfish, and strongly frowned upon. Be nice. Give back to the community. We're all friends here.

Share the project freely, but in it's entirety. Everyone should learn from this.

(LGPL stuff goes here?)

## 2 Motherboard

## 2.1 Design philosophy

The design philosophy text goes here

## 2.2 Physical specification

The physical description summary goes here

#### 2.2.1 Connectors

The motherboard connector text goes here

# 2.3 Electrical Specification

Electrical specification goes here.

# 2.3.1 Signal Bus

The signal bus is a collection of 34 lines. It may be used in one of two ways, as a single ended bus or as a balanced bus.

In single ended form, it will comprise 8 stereo channels with individual grounds. In balanced form, it will comprise 6 stereo pairs, using the power supply bus for grounds.

| Pin | Single Ended | Balanced   | Alternate |

|-----|--------------|------------|-----------|

| 1   | L Signal 1   | L Hot 1    | TBD       |

| 2   | R Signal 1   | L Cold 1   | TBD       |

| 3   | GND 1        | R Hot 1    | TBD       |

| 4   | L Signal 2   | R Cold 1   | TBD       |

| 5   | R Signal 2   | L Hot 2    | TBD       |

| 6   | GND 2        | L Cold 2   | TBD       |

| 7   | L Signal 3   | R Hot 2    | TBD       |

| 8   | R Signal 3   | R Cold 2   | TBD       |

| 9   | GND 3        | L Hot 3    | TBD       |

| 10  | L Signal 4   | L Cold 3   | TBD       |

| 11  | R Singal 4   | R Hot 3    | TBD       |

| 12  | GND 4        | R Cold 3   | TBD       |

| 13  | L Signal 5   | L Hot 4    | TBD       |

| 14  | R Signal 5   | L Cold 4   | TBD       |

| 15  | GND 5        | R Hot 4    | TBD       |

| 16  | L Signal 6   | R Cold 4   | TBD       |

| 17  | R Signal 6   | L Hot 5    | TBD       |

| 18  | GND 6        | L Cold 5   | TBD       |

| 19  | L Signal 7   | R Hot 5    | TBD       |

| 20  | R Signal 7   | R Cold 5   | TBD       |

| 21  | GND 7        | L Hot 6    | TBD       |

| 22  | L Signal 8   | L Cold 6   | TBD       |

| 23  | R Signal 8   | R Hot 6    | TBD       |

| 24  | GND 8        | R Cold 6   | TBD       |

| 25  | L Signal 9   | L Hot 7    | TBD       |

| 26  | R Signal 9   | L Cold 7   | TBD       |

| 27  | GND 9        | R Hot 7    | TBD       |

| 28  | L Signal 10  | R Cold 7   | TBD       |

| 29  | R Signal 10  | L Hot 8    | TBD       |

| 30  | GND 10       | L Cold 8   | TBD       |

| 31  | L Signal 11  | R Hot 8    | TBD       |

| 32  | R Signal 11  | R Cold 8   | TBD       |

| 33  | GND11        | COMMON GND | TBD       |

| 34  | Unused       | COMMON GND | TBD       |

**Table 1: Signal Bus Pinout**

Only signals 1-4 are used for output modules, and that bus is separate from the input module bus.

# 2.3.1.1 Input Buffering

The signal bus should be buffered. Suggest buffers are the NE5532, OPA2604, or similar high quality op-amps with +/-15V rails.

## 2.3.1.2 Switching

Input switching should be done by one or more MPC507s or similar. Buffering on the output of the switching chip(s) is highly recommended. The switching chips like to see a very low source impedance and a very high load impedance. We suggest FET input op-amps for the switch output buffers.

#### 2.3.1.3 Level control

The level control is up to the designer, but suggested chips are the TI PGA2311 and Crystal Semiconductor CS3310 (beware the lower supply and I/O voltages on the CS3310).

## 2.3.1.4 Output Buffering

The final output buffering is up to the user, as two backplane connectors are provided for output drivers. High quality parts are recommended here.

#### 2.3.2 Control Bus

The control bus is common to input and output modules

#### 2.3.2.1 Serial Control

The output buffering text goes here

#### 2.3.2.2 Bitwise Control

The output buffering text goes here

## 2.3.3 Power Supply Bus

The power supply bus is common to input and output modules.

# 2.3.3.1 Supply 1: +/-15VDC

Main bipolar power supply for audio circuits. Asymmetric loading is permitted, but frowned upon. Try and keep the current on both sides relative equal.

# 2.3.3.2 Supply 2 +/-xxVDC

Alternate bipolar supply as required by the user.

# 2.3.3.3 Supply 3 +5VDC

Doubled up power and ground pins to supply large amounts of current to current hungry parts. Isolated from the +5V supply of the logic and front panel systems.

# 2.3.3.4 Grounding

Grounding for the audio analog systems will be a bus on the motherboard. Grounding for the control systems will be a separate bus on the motherboard. All ground busses will be starred together at the power supply, at a single bonding point. The only exception is for the balanced audio bus scenario, where the power supply ground is used as the signal ground.

## 3 Module Boards

# 3.1 Design philosophy

The design philosophy text goes here

# 3.2 Physical specification

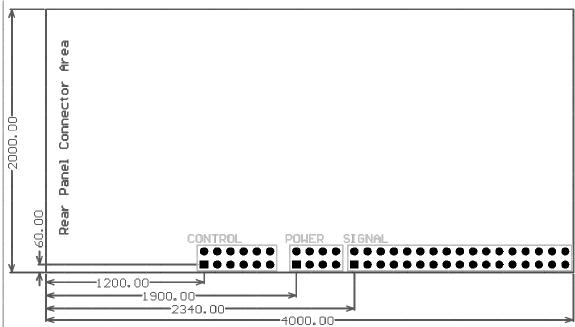

Module boards shall be 2" tall and as long as necessary for use. Common practice with the Lite version of EAGLE restricts the boards to 2" tall by 4" long. The connector positions are shown in the picture below.

Figure 1: Module Connector Placement. All dimensions are in mils (0.001")

#### 3.2.1 Connectors

The connectors for the signal bus are only populated for the channel(s) in use. By this, we mean that of the 34 pins possible for connection to the signal bus, only 6 pins must be stuffed for a standard stereo input module with a single ended bus, or 8 pins for the same on a balanced bus.

The connectors for the power and control bus should be populated completely.

# 3.3 Electrical Specification

See section 2.3.1.

# 4 Design Software

- 4.1 Schematic Capture

- 4.1.1 **EAGLE**

- 4.2 PCB Layout

- 4.2.1 **EAGLE**

## 5 Control

- 5.1 Microcontroller selection

- 5.1.1 BASIC Stamp

- 5.1.2 Parallax SX

- **5.1.3 Parallax Propeller**

- 5.1.4 Atmel AVR

- 5.1.5 Microchip PIC

- 5.1.6 Intel 8051 family

- 5.1.7 Other