# CFP5102 Data Sheet

Document No.:CFP5102 DataSheet v0.1Issue Date:2007-12-3

#### High Performance 8-bit RISC MCU

- DC-24MHz operation

- Compatible with 8051

- 160ns internal interrupt response at 24 MHz

- Single cycle per byte fetch

- All instructions are single-cycled except branching instructions

#### **Program Memory and Data Memory**

- 16K Bytes OTP program memory 384 Bytes internal SRAM for data/stack memory

- External 64K Bytes external memory interface compatibles to true 8051

- Two data pointers for indirect addressing

#### **Interrupt Features**

- 14 vectored interrupts

- 2-level interrupt priority

- External wakeup/interrupt capabilities on 3 GPIO pins and USB PHY

#### Flexible I/O

- 32 GPIO pins organized in 4 ports.

- Support open-drain or push-pull driving

- CMOS/TTL-level Schmitt triggered inputs

- Optional internal 20Kohm pull-up resistor

- 6mA sink/source current driving capability

#### **Digital Peripheral Features**

Two 16-bit timers compatible with 8051's timer0 timer1

Enhanced 8052's timer 2. Support

Capture/Reload, PWM mode and clock generation

- Real-time wake up for software clock implementation.

- Watchdog Timer with on-chip 16KHz RC oscillator

- High-speed full-duplex 8051-compatible serial port

Enhanced SPI with double-buffer for read

- and write. Operates up to 12Mb/s

- GPSI with 16-bit/32-bit packet header, for interfacing RF module, Ethernet PHY and for inter-chip communication

- Full-speed USB 2.0 Device controller module with 3 endpoints (including endpoint 0) and 208 bytes FIFO Endpoint 0: 16 bytes

Endpoint 1: IN 64 bytes / OUT 64 bytes

Endpoint 2: IN 32 bytes / OUT 32 bytes

#### **Analog Peripheral Features**

- 4~24MHz Crystal Oscillator

- 32,768 Hz Real-time Crystal Oscillator

- 16KHz RC oscillator

- Full-speed USB 2.0 Device PHY

- Digital PLL for 48MHz clock generation

- 8 channels 8-bit ADC

- Power-on reset

- On-chip regulator for 5V to 3.3V conversion

#### **Programming and Debugging Support**

- In-System Programming (ISP) support

- In-System Debugging (ISD) support

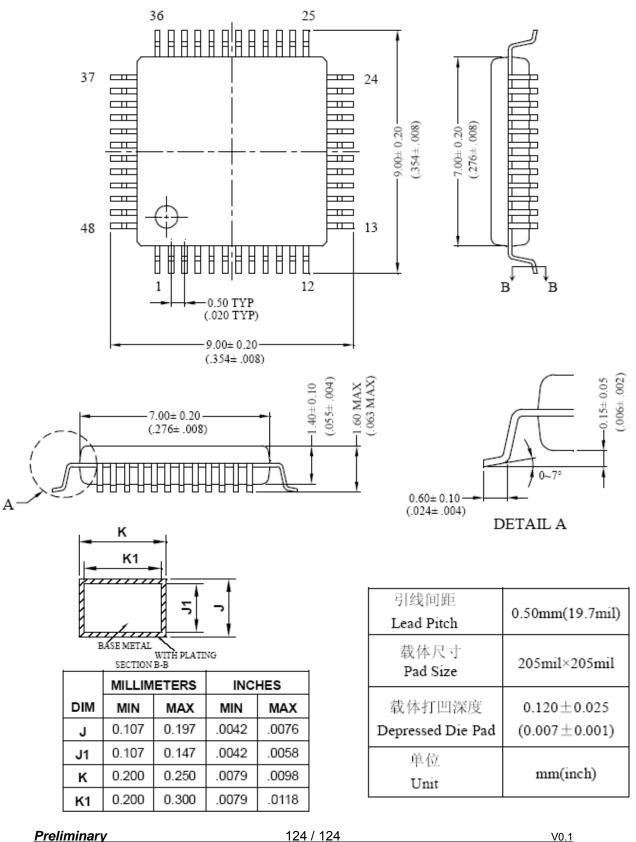

#### Packages

- 48-pin LQFP

- DIE form

V0.1

| 1 PRODUCT OVERVIEW                            | 1        |

|-----------------------------------------------|----------|

| 1.1 DESCRIPTION                               | 1        |

| 1.2 SYSTEM ARCHITECTURE                       | 2        |

| 1.2 SISTEMARCHITECTURE                        | 2        |

| 2 PIN INFORMATION                             | 3        |

|                                               |          |

| 2.1 PIN ASSIGNMENT                            | 3        |

| 2.2 PIN DESCRIPTION                           | 4        |

| <u>3</u> PROGRAMMING MODEL                    | 7        |

|                                               |          |

| 3.1 MEMORY ORGANIZATION                       | 7        |

| <b>3.2 PROGRAM MEMORY (CODE)</b>              | 7        |

| <b>3.3 DATA MEMORY (DATA)</b>                 | 10       |

| 3.4 GENERAL PURPOSE REGISTERS (REGISTER)      | 10       |

| 3.5 EXTENDED DATA MEMORY (XDATA)              | 11       |

| 3.6 PROGRAM STACK MEMORY (STACK)              | 12       |

| 3.7 CPU TIMING                                | 13       |

| 3.8 INSTRUCTION SET SUMMARY                   | 13       |

| 3.9 DUAL DATA POINTERS                        | 16       |

| 3.10 CPU REGISTERS                            | 18       |

| 3.11 SPECIAL FUNCTION REGISTERS (SFR)         | 20       |

| 3.11.1 SFR TABLE LISTED IN ALPHABETICAL ORDER | 20       |

| 3.11.2 SFR TABLE LISTED ACCORDING TO ADDRESS  | 23       |

| 4 EXTERNAL MEMORY INTERFACE (EMI)             | 26       |

|                                               |          |

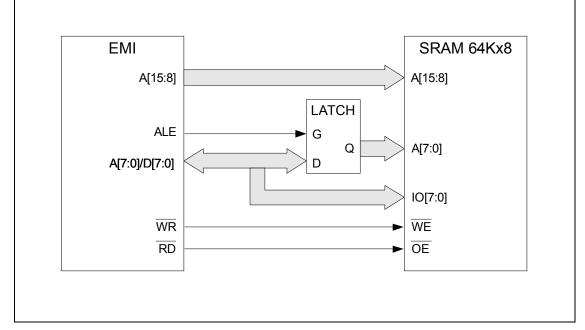

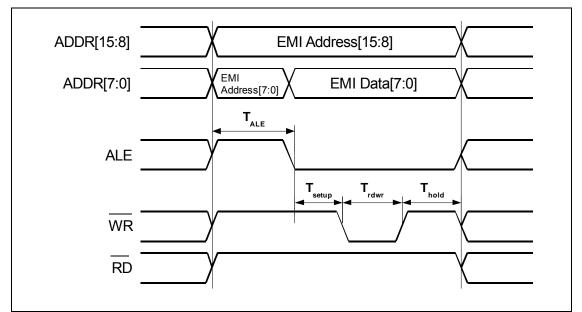

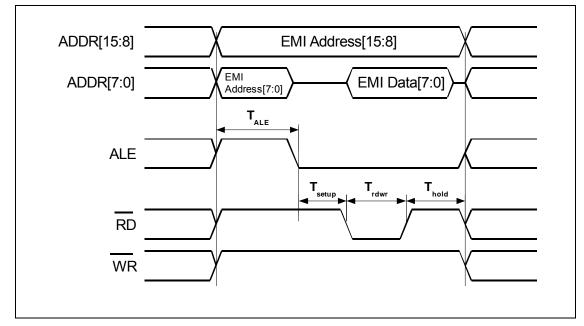

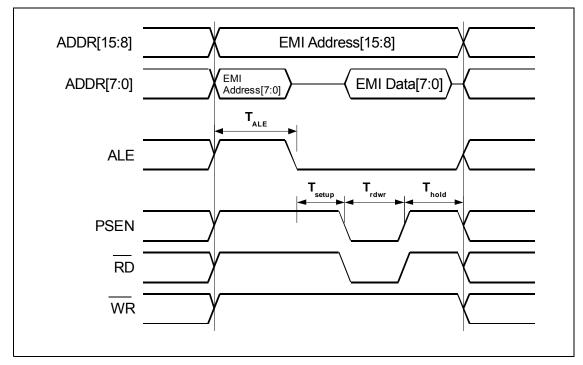

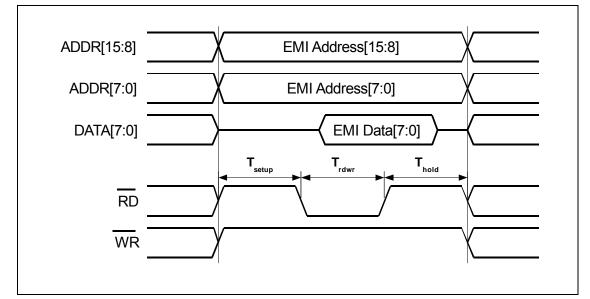

| 4.1 MULTIPLEXED ADDRESS MODE                  | 27       |

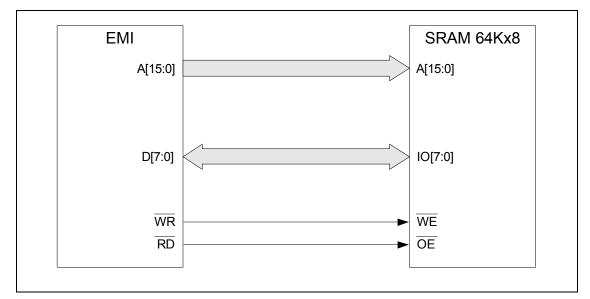

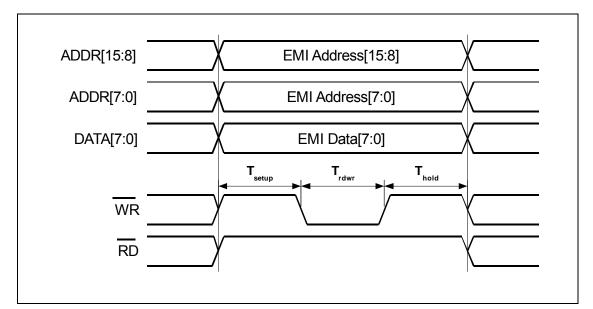

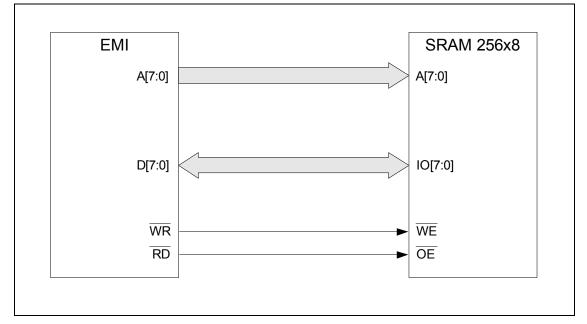

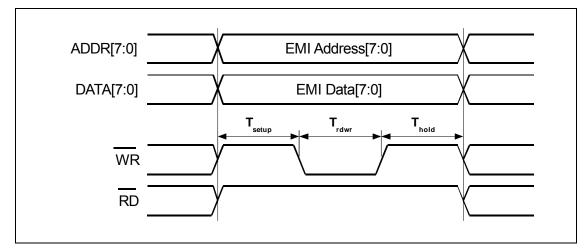

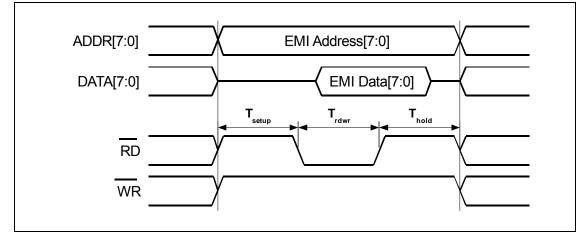

| 4.2 NON-MULTIPLEXED ADDRESS MODE              | 29       |

| 4.3 8-BIT ADDRESS MODE                        | 32       |

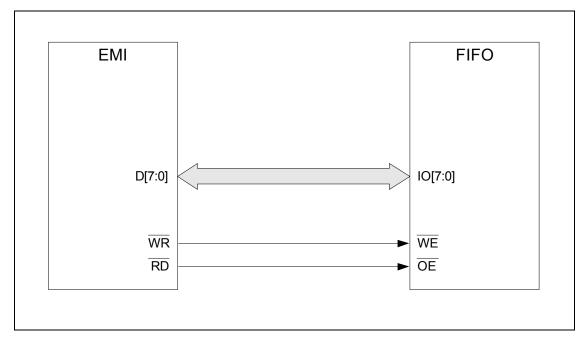

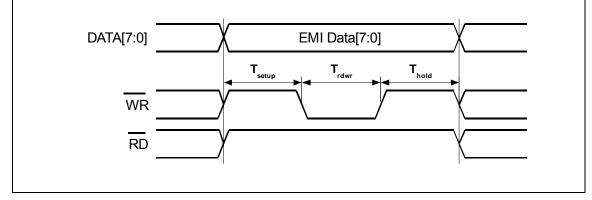

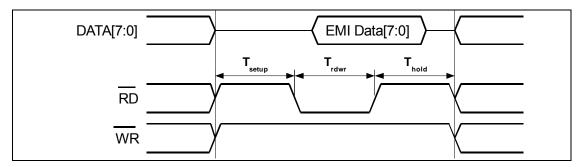

| 4.4 FIFO MODE                                 | 33       |

| 5 INTERRUPT PROCESSING                        | 35       |

|                                               |          |

| 5.1 INTERRUPT SOURCES AND VECTORS             | 36       |

| 5.2 INTERRUPT PRIORITIES                      | 36       |

| 5.3 INTERRUPT LATENCY                         | 37       |

| 6 CLOCKS AND RESETS AND POWER MANAGEM         | ENT 39   |

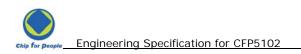

| 6.1 CLOCK SYSTEM                              | 39       |

| 6.1.1 CLOCK SYSTEM<br>6.1.1 CLOCK CONTROL     | 39<br>39 |

| 6.1.2 CLOCK GATING                            | 59<br>40 |

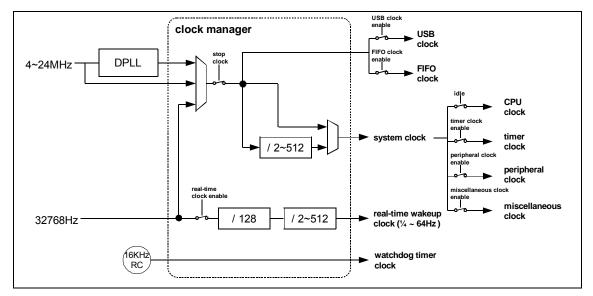

| 6.1.3 CRYSTAL OSCILLATORS                     | 40       |

| U.I.J CRISIAL OSCILLATORS                     | 41       |

### Preliminary

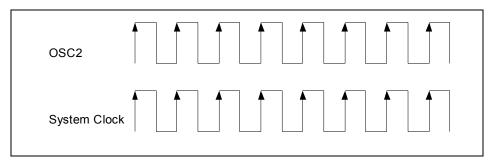

| 6.1.4      | USING EXTERNAL CLOCK GENERATORS      | 45 |

|------------|--------------------------------------|----|

| 6.1.5      | RC OSCILLATOR                        | 46 |

| 6.1.6      | DIGITAL PHASE LOCK LOOP              | 46 |

| 6.1.7      | REAL-TIME WAKEUP CLOCK               | 46 |

| 6.1.8      | SUPPLY CLOCK TO OFF-CHIP PERIPHERALS | 47 |

| <b>6.2</b> | RESETS                               | 48 |

| 6.2.1      | Reset Sequence                       | 48 |

| 6.2.2      | MASTER RESET                         | 48 |

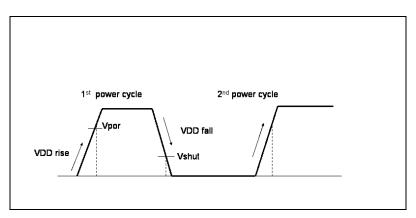

| 6.2.3      | POWER ON RESET                       | 48 |

| 6.2.4      | WATCHDOG TIMEOUT RESET               | 49 |

| <b>6.3</b> | POWER MANAGEMENT                     | 50 |

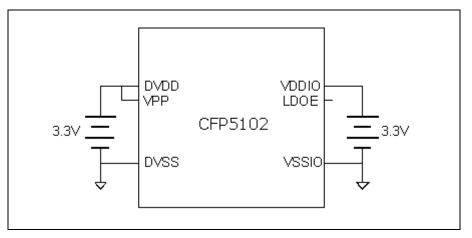

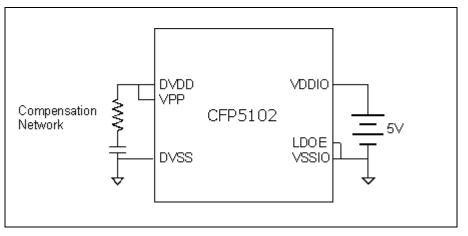

| 6.3.1      | OPERATING IN 3.3V OR 5V SYSTEMS      | 50 |

| 6.3.2      | ON-CHIP REGULATOR                    | 51 |

| 6.3.3      | IDLE MODE                            | 52 |

| 6.3.4      | HALT MODE                            | 52 |

| 6.3.5      | Power Down Mode                      | 53 |

| 6.3.6      | ADDITIONAL LOW POWER OPTIONS         | 54 |

|            |                                      |    |

### 7 PORTS AND PERIPHERALS

<u>55</u>

| 7.1 PORTS                                            | 55   |

|------------------------------------------------------|------|

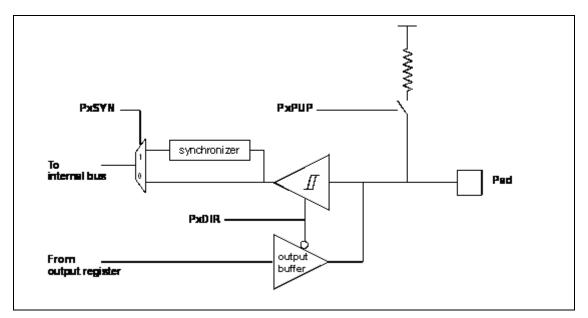

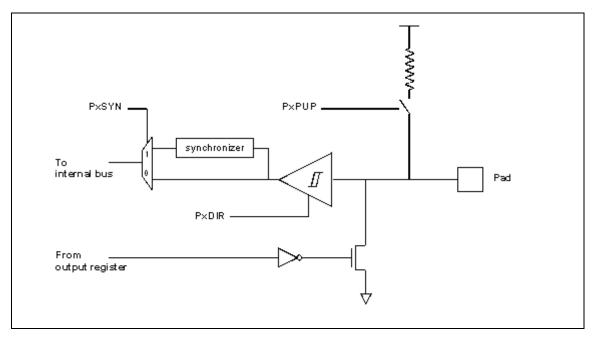

| 7.1.1 PUSH-PULL MODE AND OPEN-DRAIN MODE             | 55   |

| 7.1.2 SETTING PORT DIRECTION                         | 57   |

| 7.1.3 READING FROM AND WRITING TO PORT               | 58   |

| 7.1.4 USING PULL-UPS                                 | 59   |

| 7.1.5 CONFIGURING FOR ANALOG INPUT                   | 60   |

| 7.1.6 IO SHARED WITH PERIPHERALS                     | 61   |

| 7.1.7 INTERRUPT AND WAKEUP                           | 62   |

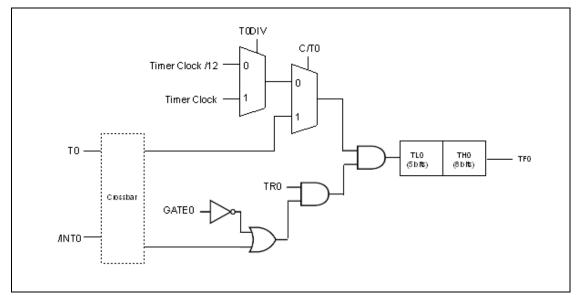

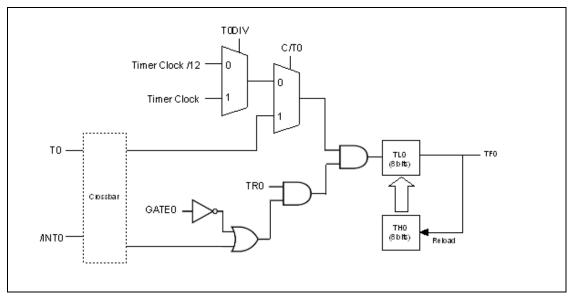

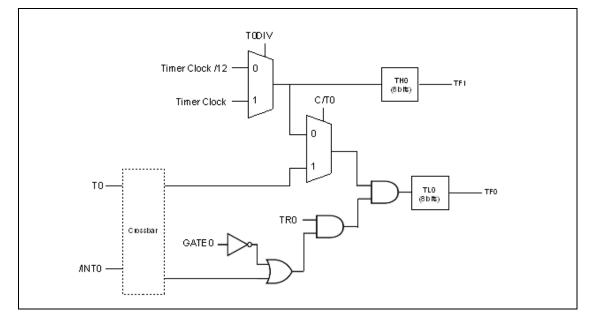

| 7.2 TIMER 0/1                                        | 66   |

| 7.2.1 MODE 0: 13-BIT COUNTER/TIMER                   | 66   |

| 7.2.2 MODE 1: 16-BIT COUNTER/TIMER                   | 66   |

| 7.2.3 MODE 2: 8-BIT COUNTER/TIMER WITH AUTO-RELOAD   | 67   |

| 7.2.4 MODE 3: TWO 8-BIT COUNTER/TIMERS (TIMER0 ONLY) | 67   |

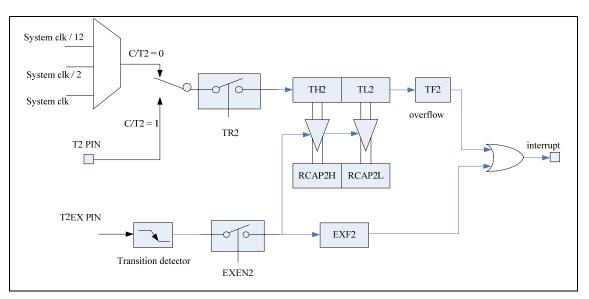

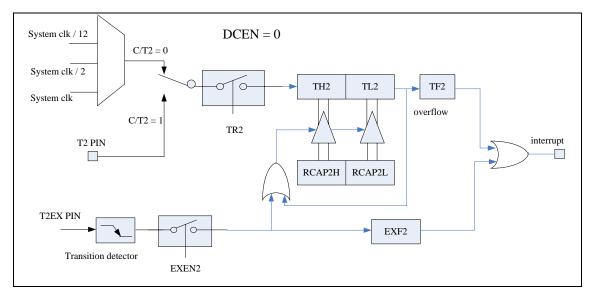

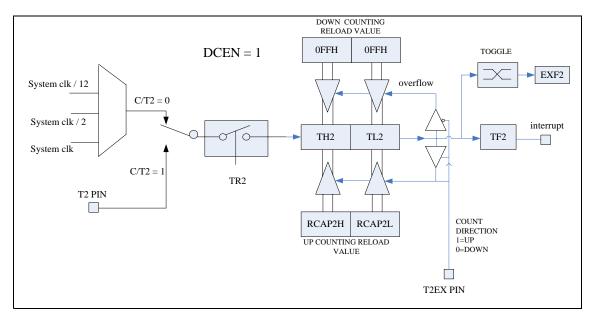

| 7.3 TIMER 2                                          | 71   |

| 7.3.1 CAPTURE MODE                                   | 71   |

| 7.3.2 AUTO-RELOAD MODE (UP OR DOWN COUNTER)          | 71   |

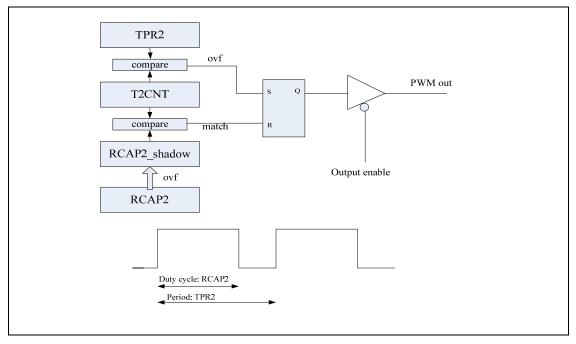

| 7.3.3 PULSE WIDTH MODULATION (PWM)                   | 73   |

| 7.3.4 OPERATION FLOW                                 | 77   |

| 7.4 REAL TIME WAKEUP                                 | 78   |

| 7.4.1 OPERATION FLOW                                 | 79   |

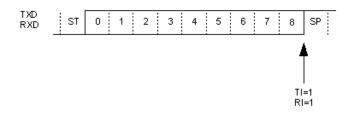

| 7.5 SERIAL PORT (UART)                               | 80   |

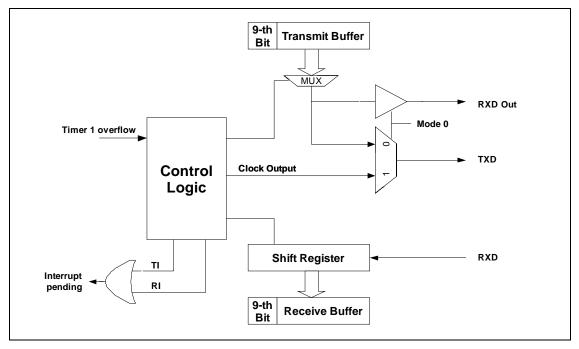

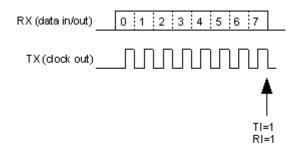

| 7.5.1 MODE 0                                         | 80   |

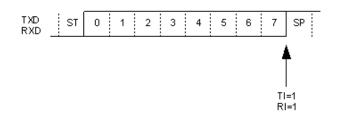

| 7.5.2 MODE 1                                         | 80   |

| 7.5.3 MODE 2                                         | 81   |

| 7.5.4 MODE 3                                         | 81   |

| 7.5.5 BAUDRATE SETTING                               | 83   |

| 7.5.6 INTERRUPT                                      | 83   |

| 7.5.7 OPERATION FLOW                                 | 84   |

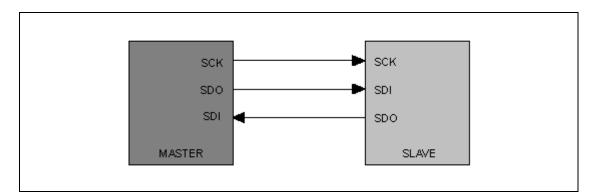

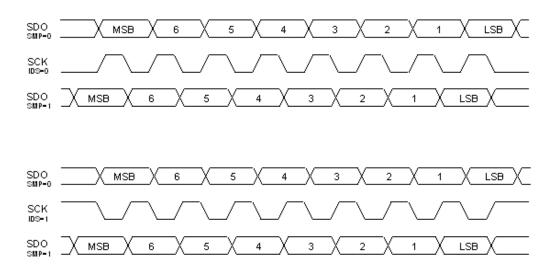

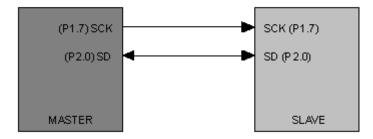

| 7.6 SERIAL PROTOCOL INTERFACE (SPI)                  | 86   |

| 7.6.1 MASTER MODE                                    | 87   |

| 7.6.2 SLAVE MODE                                     | 87   |

| Preliminary                                          | V0.1 |

### <u>Preliminary</u>

| 7.6.3 TWO-WIRE MODE                         | 87  |

|---------------------------------------------|-----|

| 7.6.4 RECEIVE-ONLY MODE                     | 88  |

| 7.6.5 BAUDRATE SETTING                      | 89  |

| 7.6.6 INTERRUPT                             | 90  |

| 7.6.7 OPERATION FLOW                        | 90  |

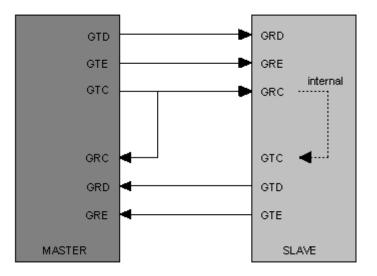

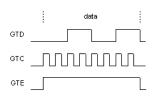

| 7.7 GENERAL PURPOSE SERIAL INTERFACE (GPSI) | 92  |

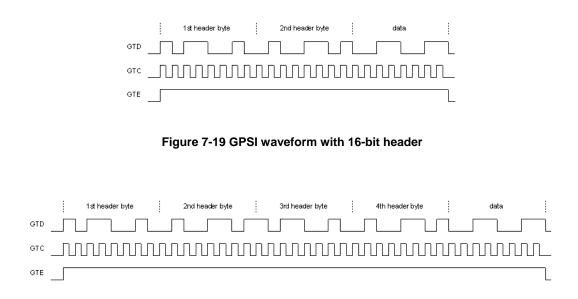

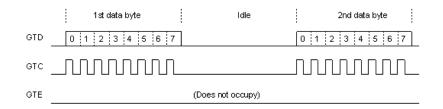

| 7.7.1 HEADER                                | 93  |

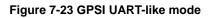

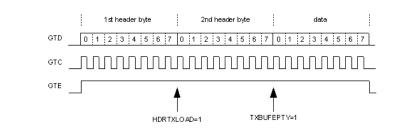

| 7.7.2 TRANSMIT PROTOCOL                     | 94  |

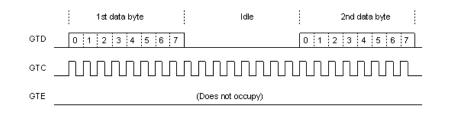

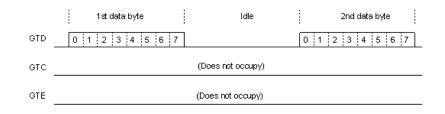

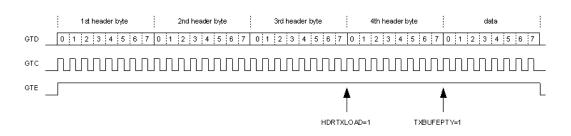

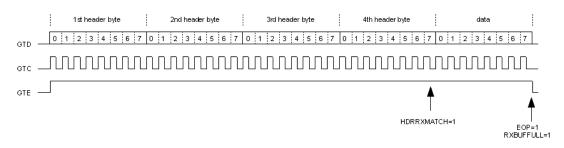

| 7.7.3 RECEIVE PROTOCOL                      | 95  |

| 7.7.4 INTERRUPTS                            | 98  |

| 7.7.5 BAUDRATE SETTING                      | 100 |

| 7.7.6 OPERATION FLOW                        | 101 |

| 7.8 ANALOG-TO-DIGITAL CONVERTER (ADC)       | 102 |

| 7.8.1 REFERENCE VOLTAGE                     | 102 |

| 7.8.2 INPUT UNITY-GAIN BUFFER               | 102 |

| 7.8.3 CONVERSION AND INTERRUPT              | 102 |

| 7.8.4 COMPARISON MODE                       | 104 |

| 7.8.5 CONVERSION TIME AND SAMPLING CLOCK    | 105 |

| 7.9 UNIVERSAL SERIAL PORT (USB)             | 106 |

| 7.9.1 USB DEVICE                            | 106 |

| 7.9.2 USB INTERFACE UNIT                    | 107 |

| 7.9.3 ACCESS USB CONTROLLER                 | 108 |

| 7.9.4 WAKEUP OPERATIONS                     | 112 |

| 7.10 FIFO INTERFACE                         | 113 |

| 7.10.1 OPERATION FLOW                       | 114 |

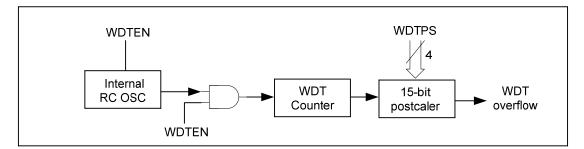

| 7.11 WATCHDOG TIMER                         | 115 |

| 7.11.1 TIMER FUNCTION                       | 116 |

| 7.11.2 CLEAR WATCHDOG TIMER                 | 116 |

| 7.11.3 WAKEUP, RESET AND INTERRUPT          | 117 |

| 8 CODE PROTECTION                           | 118 |

|                                             |     |

| 9 ELECTRICAL CHARACTERISTICS                | 119 |

| 9.1.1 ABSOLUTE MAXIMUM RATING               | 119 |

| 9.1.2 DC CHARACTERISTICS                    | 119 |

| 9.1.3 AC PARAMETERS                         | 117 |

| ,                                           | 121 |

| <u>10</u> | PACKAGE OUTLINE         | 123 |

|-----------|-------------------------|-----|

| 11        | <b>REVISION HISTORY</b> | 124 |

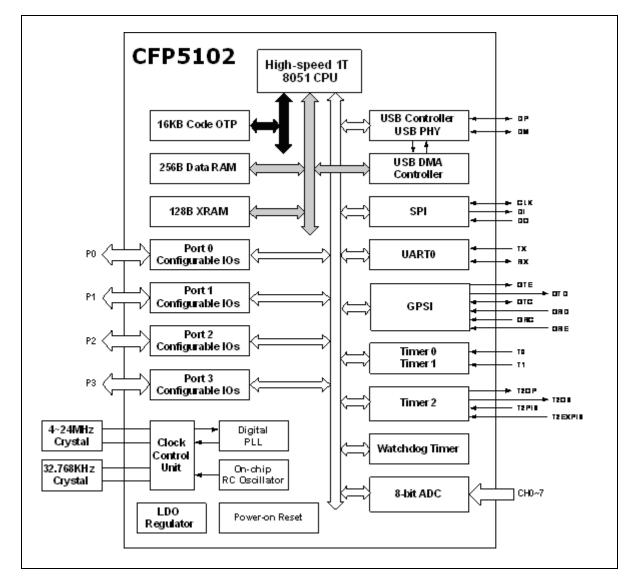

# **1 Product Overview**

### 1.1 Description

CFP5102 is an 8051 compatible mixed-signal 8-bit microcontroller. It integrates advanced digital and analog peripherals to accommodate different applications. For digital peripherals, it supports digital interfaces including UART, SPI, GPSI, three timers, watchdog timer, and an USB 2.0 full-speed device controller. For analog peripherals, it integrates an 8-bit ADC, a low dropout voltage regulator.

The microcontroller has an advanced RISC-based architecture and compatible with standard 8051 core running at 24 MIPS. All instructions take single clock cycle, except for program branching and accessing external memory.

CFP5102 has 16K byte OTP program memory and 384 bytes data memory. It also supports external memory interface (EMI), which allows program code running from external memory.

CFP5102 I/O pins have flexible programmable capabilities. It supports external port wakeup, open-drain and push-pull modes with internal pull-up resistor option.

CFP5102 has built-in In-System Programming (ISP) and In-System Debugging (ISD) capabilities, which supports third party tools to provide an integrated development environment including editor, macro assembler, debugger, programming and software peripherals.

In order to support portable applications with low power consumption, CFP5102 has three power-saving modes: IDLE, HALT and Power Down. It also has a sophisticated clock control system that can enable clock sources only for the peripherals that are running to further reduce power consumption.

TEL: +886-2-22231558 FAX: +886-2-22233988

E-mai : sales@cfpt.com.tw

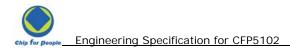

# 1.2 System Architecture

Figure 1-1: Block Diagram

# 2 Pin Information

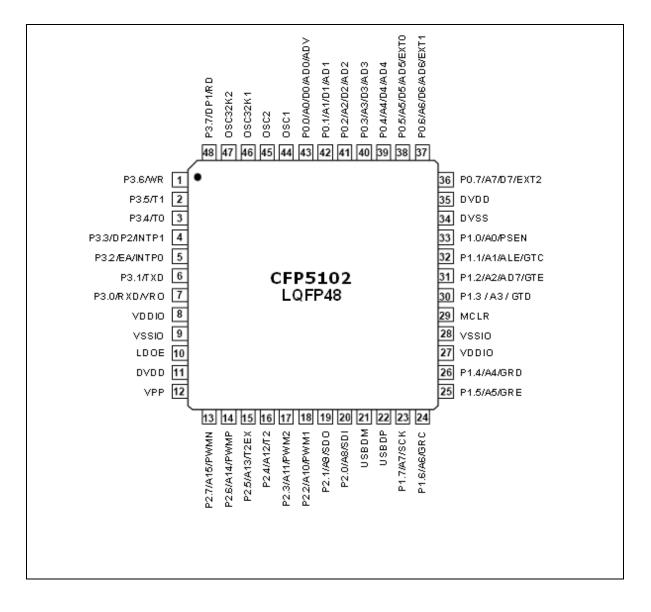

# 2.1 Pin Assignment

# 2.2 Pin Description

| Symbol                 | Pin | Type <sup>note1</sup> | Description                                                    |  |

|------------------------|-----|-----------------------|----------------------------------------------------------------|--|

| P0.0 / A0 / D0 / AD0 / | 43  | I/O                   | <b>P0.0</b> – port 0 bit 0                                     |  |

| ADV                    |     | 0                     | A0 – external memory address bus bit 0 <sup>note2</sup>        |  |

|                        |     | 0                     | <b>D0</b> – external memory data bus bit 0                     |  |

|                        |     | I                     | AD0 – analog-to-digital converter channel 0                    |  |

|                        |     | I                     | ADV – analog-to-digital converter voltage reference            |  |

| P0.1 / A1 / D1 / AD1   | 42  | I/O                   | <b>P0.1</b> – port 0 bit 1                                     |  |

|                        |     | 0                     | A1 – external memory address bus bit 1 <sup>note2</sup>        |  |

|                        |     | 0                     | D1 – external memory data bus bit 1                            |  |

|                        |     | I                     | AD1 – analog-to-digital converter channel 1                    |  |

| P0.2 / A2 / D2 / AD2   | 41  | I/O                   | <b>P0.2</b> – port 0 bit 2                                     |  |

|                        |     | 0                     | A2 – external memory address bus bit 2 <sup>note2</sup>        |  |

|                        |     | 0                     | D2 – external memory data bus bit 2                            |  |

|                        |     | l                     | AD2 – analog-to-digital converter channel 2                    |  |

| P0.3 / A3 / D3 / AD3   | 40  | I/O                   | <b>P0.3</b> – port 0 bit 3                                     |  |

|                        |     | 0                     | A3 – external memory address bus bit 3 <sup>note2</sup>        |  |

|                        |     | Õ                     | D3 – external memory data bus bit 3                            |  |

|                        |     | U<br>I                | AD3 – analog-to-digital converter channel 3                    |  |

| P0.4 / A4 / D4 / AD4   | 39  | I/O                   | P0.4 – port 0 bit 4                                            |  |

|                        | 55  | 0                     | A4 – external memory address bus bit 4 <sup>note2</sup>        |  |

|                        |     | 0                     | D4 – external memory data bus bit 4                            |  |

|                        |     | 0                     | AD4 – analog-to-digital converter channel 4                    |  |

| P0.5 / A5 / D5 / AD5 / | 38  | I/O                   | P0.5 – port 0 bit 5                                            |  |

| EXT0                   | 30  |                       | <b>PU.5</b> – poil 0 bil 5                                     |  |

| EXIU                   |     | 0                     | A5 – external memory address bus bit 5 <sup>note2</sup>        |  |

|                        |     | 0                     | <b>D5</b> – external memory data bus bit 5                     |  |

|                        |     | l                     | AD5 – analog-to-digital converter channel 5                    |  |

|                        |     | I                     | EXT0 – external interrupt 0                                    |  |

| P0.6 / A6 / D6 / AD6 / | 37  | I/O                   | <b>P0.6</b> – port 0 bit 6                                     |  |

| EXT1                   |     | 0                     | A6 – external memory address bus bit 6 <sup>note2</sup>        |  |

|                        |     | 0                     | <b>D6</b> – external memory data bus bit 6                     |  |

|                        |     | I                     | AD6 – analog-to-digital converter channel 6                    |  |

|                        |     |                       | EXT1 – external interrupt 1                                    |  |

| P0.7 / A7 / D7 / EXT2  | 36  | I/O                   | <b>P0.7</b> – port 0 bit 7                                     |  |

|                        |     | 0                     | A7 – external memory address bus bit 7 <sup>note2</sup>        |  |

|                        |     | 0                     | <b>D7</b> – external memory data bus bit 7                     |  |

|                        |     | I                     | EXT2 – external interrupt 2                                    |  |

| P1.0 / A0 / PSEN       | 33  | I/O                   | <b>P1.0</b> – port 1 bit 0                                     |  |

|                        |     | 0                     | <b>A0</b> – external memory address bus bit 0 <sup>note3</sup> |  |

|                        |     | 0                     | PSEN – external memory program select enable                   |  |

| P1.1 / A1 / ALE / GTC  | 32  | I/O                   | <b>P1.1</b> – port 1 bit 1                                     |  |

|                        |     | 0                     | A1 – external memory address bus bit 1 <sup>note3</sup>        |  |

|                        |     | 0                     | ALE – external memory address latch enable                     |  |

|                        |     | 0                     | GTC – GPSI transmit clock                                      |  |

| P1.2 / A2 / AD7 / GTE  | 31  | I/O                   | <b>P1.2</b> – port 1 bit 2                                     |  |

|                        |     | 0                     | A2 – external memory address bus bit 2 $^{note3}$              |  |

|                        |     | I                     | <b>AD7</b> – analog-to-digital converter channel 7             |  |

|                        |     | Ö                     | <b>GTE</b> – GPSI transmit enable                              |  |

| P1.3 / A3 / GTD        | 30  | 1/0                   | P1.3 – port 1 bit 3                                            |  |

|                        |     | 0                     | A3 – external memory address bus bit 3 <sup>note3</sup>        |  |

|                        |     | 0                     | <b>GTD</b> – GPSI transmit data                                |  |

| P1.4 / A4 / GRD        | 26  | 1/0                   | <b>P1.4</b> – port 1 bit 4                                     |  |

|                        | 20  |                       | pote3                                                          |  |

|                        |     | 0                     |                                                                |  |

|                        | 25  | I<br>I/O              | GRD – GPSI receive data                                        |  |

| P1.5 / A5 / GRE        | 25  | I/O                   | P1.5 – port 1 bit 5                                            |  |

|                        |     | 0                     | <b>A5</b> – external memory address bus bit 5 <sup>note3</sup> |  |

| <b>Preliminary</b>     |     |                       | 4 / 124 V0.1                                                   |  |

|                    |    |          | GRE – GPSI receive enable                                                                 |

|--------------------|----|----------|-------------------------------------------------------------------------------------------|

| P1.6 / A6 / GRC    | 24 | I/O      | <b>P1.6</b> – port 1 bit 6                                                                |

|                    |    | 0        | A6 – external memory address bus bit 6 <sup>note3</sup>                                   |

|                    |    |          | GRC – GPSI receive clock                                                                  |

| P1.7 / A7 / SCK    | 23 | I/O      | <b>P1.7</b> – port 1 bit 7                                                                |

|                    |    | 0        | <b>A7</b> – external memory address bus bit 7 <sup>note3</sup>                            |

|                    |    | I/O      | SCK – SPI clock                                                                           |

| P2.0 / A8 / SDI    | 20 | I/O      | <b>P2.0</b> – port 2 bit 0                                                                |

|                    |    | 0        | A8 – external memory address bus bit 8                                                    |

| D0 4 / 40 / 0D 0   | 40 | I/O      | SDI – SPI data input <sup>nóte4</sup>                                                     |

| P2.1 / A9 / SDO    | 19 | I/O      | P2.1 – port 2 bit 1                                                                       |

|                    |    | 0        | A9 – external memory address bus bit 9<br>SDO – SPI data output <sup>note4</sup>          |

| P2.2 / A10 / PWM1  | 18 | 1/0      | <b>P2.2</b> – port 2 bit 2                                                                |

| 12.27 81071 991911 | 10 | 0        | A10 – external memory address bus bit 10                                                  |

|                    |    | 0        | <b>PWM1</b> – 8-bit PWM channel 1                                                         |

| P2.3 / A11 / PWM2  | 17 | 1/0      | <b>P2.3</b> – port 2 bit 3                                                                |

| 1 2.077(1171 00002 |    | 0        | A11 – external memory address bus bit 11                                                  |

|                    |    | ŏ        | <b>PWM2</b> – 8-bit PWM channel 2                                                         |

| P2.4 / A12 / T2    | 16 | I/O      | <b>P2.4</b> – port 2 bit 4                                                                |

| <b>_</b>           |    | 0        | A12 – external memory address bus bit 12                                                  |

|                    |    |          | T2 –timer/counter 2 external count input                                                  |

| P2.5 / A13 / T2EX  | 15 | I/O      | <b>P2.5</b> – port 2 bit 5                                                                |

|                    |    | 0        | A13 – external memory address bus bit 13                                                  |

|                    |    | 1        | T2EXtimer/counter 2 reload/capture/direction                                              |

|                    |    | I        | control                                                                                   |

| P2.6 / A14 / PWMP  | 14 | I/O      | <b>P2.6</b> – port 2 bit 6                                                                |

|                    |    | 0        | A14 – external memory address bus bit 14                                                  |

|                    |    | 0        | <b>PWMP</b> – 16-bit PWM positive channel                                                 |

| P2.7 / A15 / PWMN  | 13 | I/O      | <b>P2.7</b> – port 2 bit 7                                                                |

|                    |    | 0        | A15 – external memory address bus bit 15                                                  |

|                    |    | 0        | PWMN – 16-bit PWM negative channel                                                        |

| P3.0 / RXD / VRO   | 7  | I/O      | <b>P3.0</b> – port 3 bit 0                                                                |

|                    |    |          | <b>RXD</b> – serial port input                                                            |

| P3.1 / TXD         | 6  | 0<br>I/O | VRO – voltage reference out (1.25V)<br>P3.1 – port 3 bit 1                                |

| FJ.T/TAD           | 0  | 0        | TXD – serial port output                                                                  |

| P3.2 / EA / INTP0  | 5  | I/O      | <b>P3.2</b> – port 3 bit 2 (pull-up enable by default)                                    |

| 10.27 E/(/ INTE    | Ŭ  | "C       | <b>INTPO</b> – port interrupt 0                                                           |

|                    |    |          | <b>EA</b> – external access enable (active LOW)                                           |

|                    |    |          | EA must be externally held LOW to enable the                                              |

|                    |    |          | device to fetch code from external program                                                |

|                    |    |          | memory locations. If EA is held HIGH, the device                                          |

|                    |    |          | executes from internal program memory. The                                                |

|                    |    |          | value on the EA pin is latched when MCLR is                                               |

|                    |    |          | released and any subsequent changes have no                                               |

|                    | 4  | 1/0      | effect.                                                                                   |

| P3.3 / DP2 / INTP1 | 4  | I/O      | <b>P3.3</b> – port 3 bit 3 (pull-up enable by default)<br><b>INTP1</b> – port interrupt 1 |

|                    |    |          | <b>DP2</b> – in-system programming pin 2 (active LOW)                                     |

|                    |    |          | DP2 must be externally held LOW to enable                                                 |

|                    |    |          | in-system programming. The value on the DP2 pin                                           |

|                    |    |          | is latched when MCLR is released and any                                                  |

|                    |    |          | subsequent changes have no effect.                                                        |

| P3.4 / T0          | 3  | I/O      | <b>P3.4</b> – port 3 bit 4                                                                |

|                    |    | I        | T0 – timer/counter 0 capture/compare/count input                                          |

| P3.5 / T1          | 2  | I/O      | <b>P3.5</b> – port 3 bit 5                                                                |

|                    |    | 1        | T1 – timer/counter 1 capture/compare/count input                                          |

| P3.6 / WR          | 1  | I/O      | <b>P3.6</b> – port 3 bit 6                                                                |

|                    |    | I        | WR – external data memory write strobe                                                    |

|                    | 40 |          | (active LOW)                                                                              |

| P3.7 / DP1 / RD    | 48 | I/O      | <b>P3.7</b> – port 3 bit 7                                                                |

| Preliminary        |    |          | 5 / 124 V0.1                                                                              |

| <u> </u>           |    |          |                                                                                           |

|          |       | I   | <b>DP1</b> – in-system programming pin 1                                                        |  |

|----------|-------|-----|-------------------------------------------------------------------------------------------------|--|

|          |       |     | Cooperate with DP2 to operate in-system                                                         |  |

|          |       |     | programming                                                                                     |  |

|          |       | I   | <b>RD</b> – external data memory read strobe                                                    |  |

| USBDP    | 22    | I/O | (active LOW)<br>USBDP – USB data (positive)                                                     |  |

| USBDM    | 22    | I/O | USBDP – USB data (positive)                                                                     |  |

| LDOE     | 10    | 0   | <b>LDOE</b> – on-chip regulator (LDO) enable                                                    |  |

| LDOL     | 10    | 0   | (active LOW)                                                                                    |  |

|          |       |     | When LDOE is tied to HIGH, the LDO will be                                                      |  |

|          |       |     | disabled. It is recommended to supply power to                                                  |  |

|          |       |     | chip through external power source into DVDD                                                    |  |

|          |       |     | pad. When LDOE is tied to LOW, the LDO will be                                                  |  |

|          |       |     | enabled and will regulate the voltage to 3.3V after                                             |  |

|          |       |     | a short start-up time.                                                                          |  |

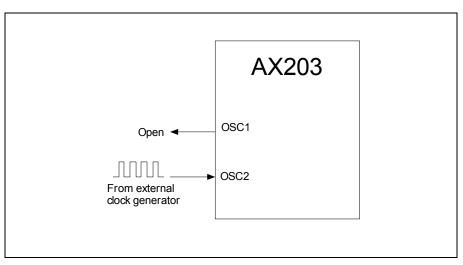

| OSC1     | 44    | Ι   | <b>OSC1</b> – high speed crystal pin 1                                                          |  |

|          |       |     | Input to the inverting oscillator amplifier and input                                           |  |

|          |       |     | to the internal clock generator circuits.                                                       |  |

| OSC2     | 45    | 0   | <b>OSC2</b> – high speed crystal pin 2                                                          |  |

| 000001/4 | 40    |     | Output from the inverting oscillator amplifier.                                                 |  |

| OSC32K1  | 46    | I   | <b>OSC32K1</b> – 32,768 Hz crystal pin 1                                                        |  |

|          |       |     | Input to the inverting oscillator amplifier and input to the internal clock generator circuits. |  |

| OSC32K2  | 47    | 0   | OSC32K2 –32,768 Hz crystal pin 1                                                                |  |

| 00002112 | 47    | 0   | Output from the inverting oscillator amplifier.                                                 |  |

| MCLR     | 29    | 1   | MCLR – master reset (active LOW)                                                                |  |

| MOLI     | 20    | •   | A LOW on this pin for 8 ms resets the device.                                                   |  |

| VPP      | 12    | Р   | <b>VPP</b> – OTP programming voltage supply                                                     |  |

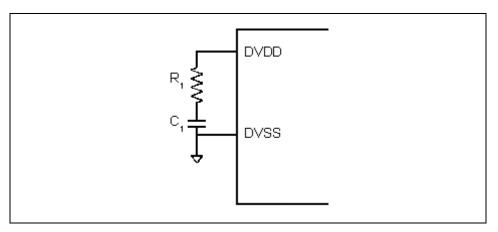

| DVDD     | 11,35 | Р   | <b>DVDD</b> – voltage supply for core                                                           |  |

|          |       |     | When LDO is enabled, this pad is served for                                                     |  |

|          |       |     | compensation for LDO output. Please refer to                                                    |  |

|          |       |     | Section 6.3.1 for external circuitry.                                                           |  |

| DVSS     | 34    | Р   | DVSS – supply ground for core                                                                   |  |

| VDDIO    | 8,27  | Р   | VDDIO – voltage supply for IO and LDO                                                           |  |

| VSSIO    | 9,28  | Р   | VSSIO – supply ground for IO and LDO                                                            |  |

Note1: O means output pin I means input pin I/O means input and output pin P means power pin Note2: For external memory interface in multiplexed address mode

Note3: For external memory interface in non-multiplexed address mode

TEL:+886-2-22231558 FAX:+886-2-22233988

E-mai : sales@cfpt.com.tw

# 3 Programming Model

### 3.1 Memory Organization

CFP5102, like 8052 contains several separated memory spaces, namely CODE, DATA, XDATA, STACK and REGISTER. These memory spaces are accessed by different addressing and by different instructions. OTP, SRAM and peripheral-control registers are mapped to these spaces. To suit for the memory requirement of different programs, CFP5102 provides enhanced configurable memory architecture. Users can select suitable memory mapping by programming the control register. The memory models are discussed in the following sections.

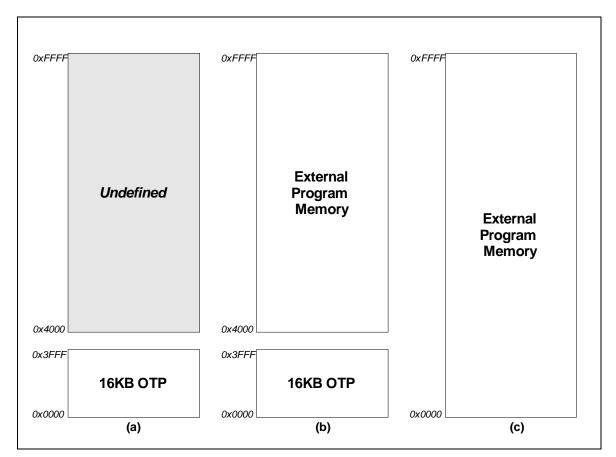

# 3.2 Program Memory (CODE)

The memory space CODE is a 64K-byte space dedicated for programs and constants. The whole space is addressed by program counter (PC) and also by two 16-bit data pointers (DPTR0 and DPTR1) using MOVC instruction. In CFP5102, the program can be implemented on-chip (in 16K-byte OTP memory), off-chip or as a combination. For applications with program excesses 16K bytes, CFP5102 provides an external memory interface (EMI) to expand the program memory through external storage, such as NOR Flash, ROM, EEPROM and etc.

The memory mapping in CODE is illustrated in Figure 3-1. In the default setting, the on-chip 16K bytes OTP memory is mapped to 0x0000 to 0x3FFF of CODE. The rest of the addressable area is not defined. Users should restrict the program within the mapped area to get rid of unpredictable operations.

CFP5102 supports two ways to enable external memory interface: (1) setting register by the program in OTP; (2) pull down the pin EA externally. In the former case, the program in OTP is working like a boot-loader, the setup program, reset program, interrupt subroutines, libraries and frequently called functions are stored in the internal OTP. As the CPU is able to work at full speed when accessing OTP, this arrangement is tuned for these frequently used parts of the program. The EMI is enabled by writing a '1' to bit 2 of DPCON (EMIEN). The details of the interconnection, timing and operation of EMI are discussed in Section 4

When users intend to execute program in external storage without programming the on-chip OTP memory, the only way is to configure CFP5102 by pulling down the pin EA during system reset until the execution of the first instruction. To stop hacking of OTP through this configuration, OTP is disabled and unmapped to any memory space. No any instruction allows accessing OTP in this mode. Further security measurements are discussed in Section 8.

Figure 3-1: (a) Default mapping of CODE. Access undefined area causes unpredictable result. (b) Mapping of CODE when external memory interface is enabled. (c) Special mapping of CODE when enabling external memory interface by forcing EA to low during system reset.

| Table 3-1: Summary of CODE | memory settings |

|----------------------------|-----------------|

|----------------------------|-----------------|

| EA | EMIEN | Memory Mapping             |

|----|-------|----------------------------|

| 1  | 0     | 0x0000 – 0x3FFF: OTP       |

|    |       | 0x4000 – 0xFFFF: Undefined |

| 1  | 1     | 0x0000 – 0x3FFF: OTP       |

|    |       | 0x4000 – 0xFFFF: EMI       |

| 0  | Х     | 0x0000 – 0xFFFF: EMI       |

TEL:+886-2-22231558 FAX:+886-2-22233988

E-mai : sales@cfpt.com.tw

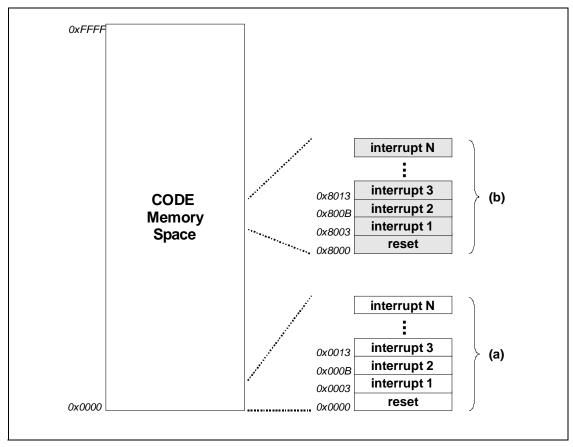

In standard 8051/8052 architecture, the reset program is located at 0x0000 of CODE. The interrupt subroutines starts from 0x0003, allocated 8 bytes for each interrupt subroutine. CFP5102 provide a remapping option to relocate the reset and interrupt entries to upper 32K-byte area of CODE. Programmers are freed from the limitation of 8051/8052 to do flexible memory planning, in addition to do fast switching between two different reset and interrupt handling schemes. To remap the reset and interrupt entries, programmers have to write '1' to bit 4 of CCON (ISRM). These setting cannot be cancelled by watchdog reset and wakeup reset. Only power-on reset clears this bit to default value, logic '0'.

Figure 3-2: (a) The location of reset and interrupt entries by default. (b) The location of reset and interrupt entries when remapping is enabled

TEL: +886-2-22231558 FAX: +886-2-22233988

E-mai : sales@cfpt.com.tw

Web-site : www.cfpt.com.tw

### 3.3 Data Memory (DATA)

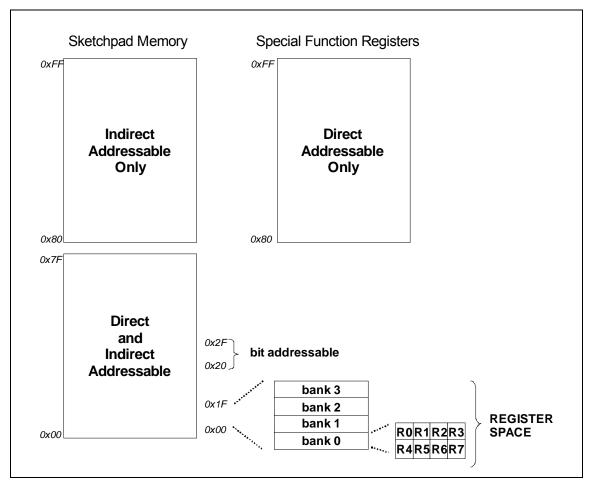

Data memory space (DATA) contains 256K bytes sketchpad memory, special function registers for controlling peripherals. It is also a super set of REGISTER space. To access this complex space, several addressing modes (direct, indirect, register and bit addressing) are provided. For details, please refer to the 8052 standard.

Figure 3-3: The mapping of DATA and REGISTER

### 3.4 General Purpose Registers (REGISTER)

General purpose registers R0 through R7 link to 32 bytes of internal data memory in the way that allows quick, efficient access. For example, the instruction *MOV A,00h* using two bytes of code can be replaced by shorthand notation instruction MOV A,R0 that uses one byte of code only.

These 32 bytes of memory are put into 4 banks. Any one of them within a bank is selected by R0 through R7. Desired register bank is selected using bits RS1 and RS0 in PSW, bit 4 and bit 3 respectively (please refer to Table 3-2 for setting description). This feature eliminates the effort required to backup the registers to stack memory during context switching, in addition provides more registers for complicated algorithms.

| Preliminary                                 | 10 / 124                         | V0.1                       |

|---------------------------------------------|----------------------------------|----------------------------|

| TEL : +886-2-22231558 FAX : +886-2-22233988 | E-mai : <u>sales@cfpt.com.tw</u> | Web-site : www.cfpt.com.tw |

| RS0 | RS1 | Bank | Mapping Address to DATA |

|-----|-----|------|-------------------------|

| 0   | 0   | 0    | 0x00 – 0x07             |

| 0   | 1   | 1    | 0x08 – 0x0F             |

| 1   | 0   | 2    | 0x10 – 0x17             |

| 1   | 1   | 3    | 0x18 – 0x1F             |

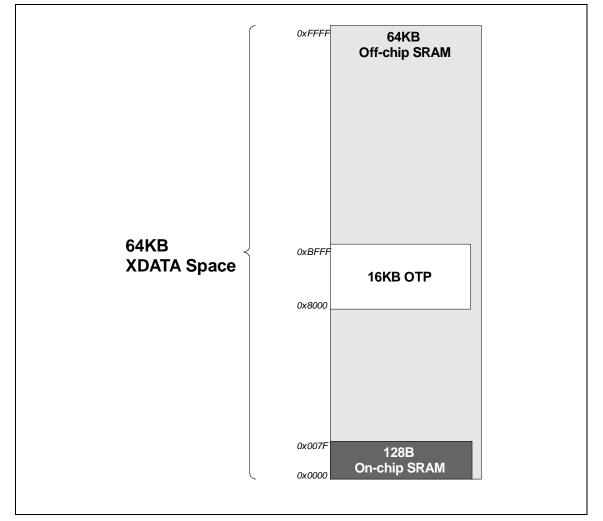

### 3.5 Extended Data Memory (XDATA)

To provide a unified linear memory model, CFP5102 organizes internal data memory and external data memory that out of the scope of DATA into extended data memory space (XDATA). Total 64K bytes of XDATA are addressed through instruction *MOVX* using two 16-bit data pointers, DPTR0 and DPTR1. XDATA contains 128 bytes on-chip SRAM, 64K bytes off-chip SRAM and also 16K bytes OTP. Constant data structures stored in OTP can be manipulated uniformly as data structures in data memory through instruction MOVX.

| EA | EMIEN | XMAP | Memory Mapping                       |

|----|-------|------|--------------------------------------|

| 1  | 0     | 0    | 0x0000 – 0x007F: On-chip SRAM (XRAM) |

|    |       |      | 0x0080 – 0xFFFF: Undefined           |

| 1  | 0     | 1    | 0x0000 – 0x007F: XRAM                |

|    |       |      | 0x0080 – 0x7FFF: Undefined           |

|    |       |      | 0x8000 – 0x9FFF: OTP                 |

|    |       |      | 0xA000 – 0xFFFF: Undefined           |

| 1  | 1     | 0    | 0x0000 – 0x007F: XRAM                |

|    |       |      | 0x0080 – 0xFFFF: EMI                 |

| 1  | 1     | 1    | 0x0000 – 0x007F: XRAM                |

|    |       |      | 0x0080 – 0x7FFF: EMI                 |

|    |       |      | 0x8000 – 0x9FFF: OTP                 |

|    |       |      | 0xA000 – 0xFFFF: EMI                 |

| 0  | 0     | Х    | 0x0000 – 0x007F: XRAM                |

|    |       |      | 0x0080 – 0xFFFF: Undefined           |

| 0  | 1     | Х    | 0x0000 – 0x007F: XRAM                |

|    |       |      | 0x0080 – 0xFFFF: EMI                 |

TEL:+886-2-22231558 FAX:+886-2-22233988

E-mai : sales@cfpt.com.tw

Figure 3-4: The mapping of XDATA

### 3.6 Program Stack Memory (STACK)

The classic 8051/8052 provides a stack for program counter storage during interrupts, subroutine calls and also for temporary data. The stack is implemented in DATA memory, therefore limited to 128 bytes in 8051 or 256 bytes in 8052. The limitation thus hampers developing large scale systems on 8051.

To breakthrough the burden to support nowadays complex systems, CFP5102 extends the program stack memory to XDATA, which means the size of the STACK can be up to 64K bytes when using external memory. The 16-bit STACK pointer is formed by combining register SPH and SP. (refer to Section 3.10)

| SPXSEL | EMIEN | Memory Mapping                           |

|--------|-------|------------------------------------------|

| 0      | 0     | 0x0000 – 0x00FF: Sketchpad memory (DRAM) |

| 1      | 0     | 0x0000 – 0x007F: On-chip SRAM (XRAM)     |

| 1      | 1     | 0x0000 – 0x007F: XRAM                    |

|        |       | 0x0080 – 0xFFFF: EMI                     |

| <u>Preliminary</u>                          | 12 / 124                  | V0.1                       |

|---------------------------------------------|---------------------------|----------------------------|

| TEL : +886-2-22231558 FAX : +886-2-22233988 | E-mai : sales@cfpt.com.tw | Web-site : www.cfpt.com.tw |

### 3.7 CPU Timing

CFP5102 is a high performance MCU. It executes most instruction in 1 cycle, in contrast to 12 cycles in classic 8051/8052. To fetch instructions, CFP5102 reads 1 byte at each cycle. To take all into account, the cycle required to complete an instruction can be calculated as follows:

Cycle required = number of bytes + execution cycle -1

For example, the instruction ADDC A, Rn takes 1 cycle; the instruction MOVC A, @A+PC takes 3 cycles

|    |                      |           |                                          | Number of<br>Bytes | Execution<br>Cycle |  |  |  |  |

|----|----------------------|-----------|------------------------------------------|--------------------|--------------------|--|--|--|--|

| #  | Mnemo                | onics     | Description                              | 2                  |                    |  |  |  |  |

|    |                      |           | Arithmetic Instructions                  | 1                  | 1                  |  |  |  |  |

| 1  | ADD                  | A, Rn     | Add register to A                        | 2                  | 1                  |  |  |  |  |

| 2  | ADD                  | A, direct | Add direct byte to A                     | 2<br>1             | 1                  |  |  |  |  |

| 3  |                      | A, @Ri    | Add indirect RAM to A                    | 2                  | 1                  |  |  |  |  |

| 4  | ADD                  | A, #data  | Add immediate to A                       | 2<br>1             | 1                  |  |  |  |  |

| 5  | ADDC                 |           | Add register to A with carry             | 2                  | 1                  |  |  |  |  |

| 6  |                      | A, direct | Add direct byte to A with carry          | 2<br>1             | 1                  |  |  |  |  |

| 7  |                      | A, @Ri    | Add indirect RAM to A with carry         | 2                  | 1                  |  |  |  |  |

| 8  |                      | A, #data  | Add immediate to A with carry            | 2<br>1             | 1                  |  |  |  |  |

| 9  | SUBB                 |           | Subtract register from A with borrow     | 2                  | 1                  |  |  |  |  |

| 10 |                      | A, direct | Subtract direct byte from A with borrow  |                    | -                  |  |  |  |  |

| 11 |                      | A, @Ri    | Subtract indirect RAM from A with borrow | 1                  | 1                  |  |  |  |  |

| 12 |                      | A, #data  | Subtract immediate from A with borrow    |                    | 1                  |  |  |  |  |

| 13 | INC                  | <u>A</u>  | Increment A                              | 1                  | 1                  |  |  |  |  |

| 14 | INC                  | Rn        | Increment register                       | 1                  | 1                  |  |  |  |  |

| 15 | INC                  | direct    | Increment direct byte                    | 2                  | 1                  |  |  |  |  |

| 16 | INC                  | @Ri       | Increment indirect RAM                   | 1                  | 1                  |  |  |  |  |

| 17 | DEC                  | A         | Decrement A                              | 1                  | 1                  |  |  |  |  |

| 18 | DEC                  | Rn        | Decrement register                       | 1                  | 1                  |  |  |  |  |

| 19 | DEC                  | direct    | Decrement direct byte                    | 2                  | 1                  |  |  |  |  |

| 20 | DEC                  | @Ri       | Decrement indirect RAM                   | 1                  | 1                  |  |  |  |  |

| 21 | INC                  | DPTR      | Increment Data Pointer                   | 1                  | 1                  |  |  |  |  |

| 22 | MUL                  | AB        | Multiply A and B                         | 1                  | 1                  |  |  |  |  |

| 23 | DIV                  | AB        | Divide A by B                            | 1                  | 1                  |  |  |  |  |

| 24 | DA                   | Α         | Decimal adjust A                         | 1                  | 1                  |  |  |  |  |

|    | Logical Instructions |           |                                          |                    |                    |  |  |  |  |

| 25 | ANL                  | A, Rn     | AND register to A                        | 1                  | 1                  |  |  |  |  |

| 26 | ANL                  | A, direct | AND direct byte to A                     | 2                  | 1                  |  |  |  |  |

| 27 | ANL                  | A, @Ri    | AND indirect RAM to A                    | 1                  | 1                  |  |  |  |  |

### 3.8 Instruction Set Summary

#### Preliminary

13 / 124

TEL:+886-2-22231558 FAX:+886-2-22233988

E-mai : sales@cfpt.com.tw

| <u></u> | A N '' | A #1-1-1       |                                          | 2      | 1 |

|---------|--------|----------------|------------------------------------------|--------|---|

|         | ANL    | A, #data       | AND immediate to A                       |        |   |

|         | ANL    | direct, A      | AND A to direct byte                     | 2      | 1 |

|         | ANL    | direct, #data  | AND immediate to direct byte             | 3      | 1 |

| 31      | ORL    | A, Rn          | OR register to A                         | 1      | 1 |

| 32      | ORL    | A, direct      | OR direct byte to A                      | 2      | 1 |

| 33      | ORL    | A, @Ri         | OR indirect RAM to A                     | 1      | 1 |

| 34      | ORL    | A, #data       | OR immediate to A                        | 2      | 1 |

| 35      | ORL    | direct, A      | OR A to direct byte                      | 2      | 1 |

| 36      | ORL    | direct, #data  | OR immediate to direct byte              | 3      | 1 |

| 37      | XRL    | A, Rn          | XOR register to A                        | 1      | 1 |

| 38      | XRL    | A, direct      | XOR direct byte to A                     | 2      | 1 |

| 39      | XRL    | A, @Ri         | XOR indirect RAM to A                    | 1      | 1 |

| 40      | XRL    | A, #data       | XOR immediate to A                       | 2      | 1 |

| 41      | XRL    | direct, A      | XOR A to direct byte                     | 2      | 1 |

| 42      | XRL    | direct, #data  | XOR immediate to direct byte             | 3      | 1 |

|         | CLR    | A              | Clear A                                  | 1      | 1 |

| 44      | CPL    | A              | Complement A                             | 1      | 1 |

| 45      | RL     | A              | Rotate A left                            | 1      | 1 |

|         | RLC    | A              | Rotate A left through carry              | 1      | 1 |

|         | RR     | A              | Rotate A right                           | 1      | 1 |

|         | RRC    | A              | Rotate A right through carry             | 1      | 1 |

|         | SWAP   |                | Swap nibbles of A                        | 1      | 1 |

|         |        |                | Data Transfer Instructions               |        |   |

| 50      | MOV    | A, Rn          | Move register to A                       | 1      | 1 |

|         |        | A, direct      | Move direct byte to A                    | 2      | 1 |

|         |        | A, @Ri         | Move indirect RAM to A                   | 1      | 1 |

|         |        | A, #data       | Move immediate to A                      | 2      | 1 |

|         | MOV    | Rn, A          | Move A to register                       | 1      | 1 |

| -       | MOV    | Rn, direct     | Move direct byte to register             | 2      | 1 |

|         | MOV    | Rn. #data      | Move immediate to register               | 2      | 1 |

|         |        | direct, A      | Move A to direct byte                    | 2      | 1 |

|         |        | direct, Rn     | Move register to direct byte             | 2      | 1 |

|         | MOV    | direct, direct | Move direct byte to direct byte          | 3      | 1 |

|         | MOV    | direct, @Ri    | Move indirect Byte to direct byte        | 2      | 1 |

|         | MOV    | direct, #data  | Move immediate to direct byte            | 3      | 1 |

| -       | MOV    | @Ri, A         | Move A to indirect RAM                   | 1      | 1 |

|         | MOV    | @Ri, direct    | Move direct byte to indirect RAM         | 2      | 1 |

|         | MOV    |                | Move immediate to indirect RAM           | 2      | 1 |

|         | MOV    | @Ri, #data     | Load DPTR with 16-bit constant           | 3      | 1 |

|         |        | DPTR, #data    |                                          | 1      | 3 |

|         |        | A, @A+DPTR     | Move code byte relative DPTR to A        | 1      | 3 |

|         |        | A, @A+PC       | Move code byte relative PC to A          | 1      | 1 |

|         |        | A, @Ri         | Move external data (8-bit address) to A  | 1      | 1 |

|         |        | @Ri, A         | Move A to external data (8-bit address)  | י<br>1 | 1 |

|         |        | A, @DPTR       | Move external data (16-bit address) to A | 1      | 1 |

|         |        | @DPTR, A       | Move A to external data (16-bit address) | 2      | 1 |

|         | PUSH   |                | Push direct byte onto stack              | 2      | 1 |

| 73      | POP    | direct         | Pop direct byte from stack               | 2      | I |

### Preliminary

V0.1

| 74       | ХСН   | A, Rn                 | Exchange register with A                            | 1 | 1      |

|----------|-------|-----------------------|-----------------------------------------------------|---|--------|

|          | ХСН   | A, direct             | Exchange direct byte with A                         | 2 | 1      |

| 76       |       | A, @Ri                | Exchange indirect RAM with A                        | 1 | 1      |

|          |       | A, @Ri                | Exchange low nibble of indirect RAM with A          | 1 | 1      |

| 11       | лопр  |                       | Bit Manipulation Instructions                       |   |        |

| 70       | CLR   | С                     | ·                                                   | 1 | 1      |

| 78<br>70 |       |                       | Clear carry                                         | 2 | 1      |

| 79<br>80 |       | bit                   | Clear direct bit                                    | 1 | 1      |

| 80       | SETB  | C                     | Set carry                                           | 2 | 1      |

| 81<br>80 | SETB  | bit                   | Set direct bit                                      | 1 | 1      |

| 82       | CPL   | C                     | Complement carry                                    | 2 | 1      |

| 83       | CPL   | bit                   | Complement direct bit                               |   |        |

| 84       | ANL   | C, bit                | AND direct bit to carry                             | 2 | 1      |

| 85       | ANL   | C, /bit               | AND complement of direct bit to carry               | 2 | 1      |

| 86       | ORL   | C, bit                | OR direct bit to carry                              | 2 | 1      |

| 87       | ORL   | C, /bit               | OR complement of direct bit to carry                | 2 | 1      |

|          | MOV   | C, bit                | Move direct bit to Carry                            | 2 | 1      |

| 89       | MOV   | bit, C                | Move Carry to direct bit                            | 2 | 1      |

| 90       | JC    | rel code              | Jump if carry is set                                | 2 | 1 3*   |

| 91       | JNC   | rel code              | Jump if carry is not set                            | 2 | 1 3*   |

| 92       | JB    | bit, rel code         | Jump if direct bit is set                           | 3 | 1 3*   |

| 93       | JNB   | bit, rel code         | Jump if direct bit is not set                       | 3 | 1 3*   |

| 94       | JBC   | bit, rel code         | Jump if direct bit is set and clear bit             | 3 | 1 3*   |

|          | 1     |                       | Program Branching Instructions                      | 1 | -      |

| 95       | ACALL | page code             | Absolute subroutine call                            | 2 | 3      |

| 96       | LCALL | long code             | Long subroutine call                                | 3 | 3      |

| 97       | RET   |                       | Return from subroutine                              | 1 | 3      |

| 98       | RETI  |                       | Return from interrupt                               | 1 | 3      |

| 99       | AJMP  | page code             | Absolute jump                                       | 2 | 3      |

| 100      | LJMP  | long code             | Long jump                                           | 3 | 3      |

| 101      | SJMP  | rel addr              | Short jump (relative address)                       | 2 | 3      |

| 102      | JMP   | @A+DPTR               | Jump indirect relative to DPTR                      | 1 | 3      |

| 103      | JZ    | rel code              | Jump if A equals zero                               | 2 | 1 3*   |

| 104      | JNZ   | rel code              | Jump if A does not equal zero                       | 2 | 1   3* |

| 105      | CJNE  | A, direct, rel code   | Compare direct byte to A and jump if not equal      | 3 | 1   3* |

| 106      | CJNE  | A, #data, rel code    | Compare immediate to A and jump if not equal        | 3 | 1   3* |

|          | CJNE  | Rn, #data, rel code   | Compare immediate to Register and jump if not equal | 3 | 1 3*   |

| 108      | CJNE  | @Ri, #data, rel code  | Compare immediate to indirect and jump if not equal | 3 | 1 3*   |

| 109      | DJNZ  | Rn, rel code          | Decrement Register and jump if not zero             | 2 | 1 3*   |

|          | DJNZ  | direct, rel code      | Decrement direct byte and jump if not zero          | 3 | 1 3*   |

|          | NOP   |                       | No operation                                        | 1 | 1      |

|          |       | cates a branch occurs |                                                     | 1 |        |

### Notes on Registers, Operands and Addressing Modes:

Rn - Register R0-R7 of the currently selected register bank.

@Ri - Data RAM location addressed indirectly through R0 or R1.

rel - 8-bit, signed (2s complement) offset relative to the first byte of the following instruction.

#### **Preliminary**

Used by SJMP and all conditional jumps.

**direct** - 8-bit internal data location's address. This could be a direct-access Data RAM location (0x00-0x7F) or an SFR (0x80-0xFF).

#data - 8-bit constant

#data16 - 16-bit constant

**bit** - Direct-accessed bit in Data RAM or SFR

**page code** - 11-bit destination address used by ACALL and AJMP. The destination must be within the same 2K-byte page of program memory as the first byte of the following instruction. **long code** - 16-bit destination address used by LCALL and LJMP. The destination may be anywhere within the 64K-byte program memory space.

### 3.9 **Dual Data Pointers**

To facilitate data movement in XDATA, CFP5102 provides dual data pointers. Two independent data pointers are especially useful when moving, copying and manipulating large data types, such arrays, structures and unions. Based on this feature, CFP5102 saves many operations in manipulating pointer, comparing to single data pointer classic 8051/8052. The additional data pointer can be selected through register DPCON. No additional instruction is introduced to distinguish these 2 pointers.

| DPCON:<br>TYPE:                       | R/\  | N. | ointer Cor   | trol Regis  | ter              |              |         |            |         |

|---------------------------------------|------|----|--------------|-------------|------------------|--------------|---------|------------|---------|

| ADDRESS:<br>Position                  | Ox8  | 56 | Bit6         | Bit5        | Bit4             | Bit3         | Bit2    | Bit1       | BitO    |

| Mnemonic                              | DPID | 1  |              | DPTSE       | DPAID            | -            | EMIEN   | SPXSEL     | DPS     |

| Default                               | 0    |    | 0            | 0           | 0                | -            |         |            | 0       |

| Derduit                               | 0    |    | 0            | 0           | 0                | 0            | U       | 0          | 0       |

| Name                                  | Mode | D  | escription   |             |                  |              | Se      | etting     |         |

| DPID1                                 | RW   | R  | eplace inst  | ruction INC | DPTR1 by I       | DEC DPTR     |         | INC        |         |

|                                       |      |    | -1           |             | - 5              | -            |         | DEC        |         |

| DPID0                                 | RW   | R  | eplace inst  | ruction INC | DPTR0 by I       | DEC DPTR     |         | INC        |         |

|                                       |      |    |              |             | ,                |              |         | DEC        |         |

| DPTSE                                 | RW   | Α  | utomatic DI  | PTR select  | toggle enab      | le.          |         | disable    |         |

| 21.101                                |      |    |              |             | omatically a     |              | •••     | enable     |         |

|                                       |      |    | 10VC instru  |             | ,,               | ,            |         |            |         |

| DPTAID                                | RW   |    |              |             | ent/decrem       | ent enable b | oit. O: | disable    |         |

|                                       |      |    |              |             | TR automa        |              |         | enable     |         |

|                                       |      |    | 10VX or MC   |             |                  |              | ung n   | 0110.010   |         |

| EMIEN                                 | RW   |    |              |             | ce enable b      | it           | 0.      | disable    |         |

|                                       |      |    |              |             |                  |              |         | enable     |         |

| SPXSEL                                | RW   | S  | tack point X | RAM mapr    | oing select b    | it           |         | map to DRA | M       |

| OI XOLL                               |      |    |              |             | RAM space        |              |         | map to XRA |         |

| DPS                                   | RW   |    | ata pointer  |             |                  |              |         | DPTR0      |         |

| DIO                                   | 1    | 0  |              | 301001      |                  |              | ••      | DPTR1      |         |

| DPH:<br>TYPE:<br>ADDRESS:<br>Position | R/\  | N  | r 0 High B   | yte Regist  | er<br>Bit4       | Bit3         | Bit2    | Bit1       | BitO    |

| Mnemonic                              |      |    | 2.10         | 2.00        | DPTR             |              |         | 2.01       | 2       |

| Default                               |      |    |              |             | 0000             |              |         |            |         |

|                                       | ·    |    |              |             |                  |              |         |            |         |

| DPL:                                  |      |    | ointer 0 H   | igh Byte R  | egister          |              |         |            |         |

| TYPE:                                 | R/\  |    |              |             |                  |              |         |            |         |

| ADDRESS:                              |      | 32 |              |             |                  |              |         |            | <b></b> |

| Position                              | Bit7 |    | Bit6         | Bit5        | Bit4             | Bit3         | Bit2    | Bit1       | Bit0    |

| Mnemonic                              |      |    |              |             | DPTR             |              |         |            |         |

| Default                               |      |    |              |             | 0000             | 0000         |         |            |         |

| Prelimina                             | nv   |    |              |             | 16 / 124         |              |         |            | V0.1    |

|                                       |      |    |              |             | - · · <b>- ·</b> |              |         |            |         |

TEL : +886-2-22231558 FAX : +886-2-22233988 E-mai : <u>sales@cfpt.com.tw</u>

| Data Pointer 1 High Byte Register |             |             |             |                                             |             |                                                             |                                                                  |

|-----------------------------------|-------------|-------------|-------------|---------------------------------------------|-------------|-------------------------------------------------------------|------------------------------------------------------------------|

| R/W                               |             |             |             |                                             |             |                                                             |                                                                  |

| 0x85                              |             |             |             |                                             |             |                                                             |                                                                  |

| Bit7                              | Bit6        | Bit5        | Bit4        | Bit3                                        | Bit2        | Bit1                                                        | BitO                                                             |

|                                   |             |             | DPTR1       | [15:8]                                      |             |                                                             |                                                                  |

|                                   |             |             | 0000        | 0000                                        |             |                                                             |                                                                  |

|                                   |             |             | 0000        | 0000                                        |             |                                                             |                                                                  |

|                                   | R/W<br>0x85 | R/W<br>0x85 | R/W<br>0x85 | R/W<br>0x85<br>Bit7 Bit6 Bit5 Bit4<br>DPTR1 | R/W<br>0x85 | R/W<br>0x85<br>Bit7 Bit6 Bit5 Bit4 Bit3 Bit2<br>DPTR1[15:8] | R/W<br>0x85<br>Bit7 Bit6 Bit5 Bit4 Bit3 Bit2 Bit1<br>DPTR1[15:8] |

| DPL1:    | Data Pointer 1 High Byte Register |            |      |      |      |      |      |      |  |

|----------|-----------------------------------|------------|------|------|------|------|------|------|--|

| TYPE:    | R/W                               |            |      |      |      |      |      |      |  |

| ADDRESS: | 0x84                              |            |      |      |      |      |      |      |  |

| Position | Bit7                              | Bit6       | Bit5 | Bit4 | Bit3 | Bit2 | Bit1 | BitO |  |

| Mnemonic |                                   | DPTR1[7:0] |      |      |      |      |      |      |  |

| Default  |                                   | 0000000    |      |      |      |      |      |      |  |

# 3.10 CPU Registers

| CPU Co | CPU Control Register |                                    |                                             |                                                       |                                                                 |                                                                        |                                                                           |  |  |  |  |  |

|--------|----------------------|------------------------------------|---------------------------------------------|-------------------------------------------------------|-----------------------------------------------------------------|------------------------------------------------------------------------|---------------------------------------------------------------------------|--|--|--|--|--|

| R/W    | _                    |                                    |                                             |                                                       |                                                                 |                                                                        |                                                                           |  |  |  |  |  |

| OxAB   |                      |                                    |                                             |                                                       |                                                                 |                                                                        |                                                                           |  |  |  |  |  |

| Bit7   | Bit6                 | Bit5                               | Bit4                                        | Bit3                                                  | Bit2                                                            | Bit1                                                                   | BitO                                                                      |  |  |  |  |  |

| PROT   | -                    | LPM                                | ISRM                                        | XMAP                                                  | -                                                               | -                                                                      | -                                                                         |  |  |  |  |  |

| 0      | 0                    | 0                                  | 0                                           | 0                                                     | 0                                                               | 0                                                                      | 0                                                                         |  |  |  |  |  |

|        | R/W<br>OxAB<br>Bit7  | R/W<br>OxAB<br>Bit7 Bit6<br>PROT - | R/W<br>0xAB<br>Bit7 Bit6 Bit5<br>PROT - LPM | R/W<br>OxAB<br>Bit7 Bit6 Bit5 Bit4<br>PROT - LPM ISRM | R/W<br>OxAB<br>Bit7 Bit6 Bit5 Bit4 Bit3<br>PROT - LPM ISRM XMAP | R/W<br>OxAB<br>Bit7 Bit6 Bit5 Bit4 Bit3 Bit2<br>PROT - LPM ISRM XMAP - | R/W<br>OxAB<br>Bit7 Bit6 Bit5 Bit4 Bit3 Bit2 Bit1<br>PROT - LPM ISRM XMAP |  |  |  |  |  |

| Name | Mode | Description                                            | Setting              |

|------|------|--------------------------------------------------------|----------------------|

| PROT | RW   | OTP code protection enable bit.                        | 0: disable           |

|      |      | When set to '1', MOVC to OTP memory is disabled.       | 1: enable            |

|      |      | This bit can clear by reset sources only               |                      |

| LPM  | RW   | Low power mode enable bit.                             | 0: disable           |

|      |      | Reduce the power consumption by OTP memory.            | 1: enable            |

|      |      | Caution: this mode can only be enabled when system     |                      |

|      |      | clock is under 10MHz                                   |                      |

| ISRM | RW   | Interrupt subroutine mapping bit.                      | 0: no offset         |

|      |      | 0x8000 offset is added to the address of the interrupt | 1: add 0x8000 offset |

|      |      | subroutine when this bit is set                        |                      |

| XMAP | RW   | OTP mapping to XRAM enable bit.                        | 0: disable           |

|      |      | Map OTP memory to XRAM space when set to '1'.          | 1: enable            |

|      |      | User can use MOVX instruction to access                |                      |

| PSW:<br>TYPE:<br>ADDRESS | R/V   |               | d           |      |      |      |        |      |

|--------------------------|-------|---------------|-------------|------|------|------|--------|------|

| Position                 | Bit7  | Bit6          | Bit5        | Bit4 | Bit3 | Bit2 | Bit1   | BitO |

| Mnemonic                 | CY    | AC            | FO          | RS1  | RS0  | ov   | F1     | Р    |

| Default                  | 0     | 0             | 0           | 0    | 0    | 0    | 0      | 0    |

| News                     | Maria | Description   |             |      |      | 0    |        |      |

| Name                     | Mode  | Description   |             |      |      | Se   | etting |      |

| Р                        | R     | Odd parity cl | neck of ACC | ;    |      |      |        |      |

| OV                       | RW    | Overflow flag | 3           |      |      |      |        |      |

| F1, F0                   | RW    | User-defined  | l bits      |      |      |      |        |      |

| RS1,<br>RS0              | RW    | Register bar  | k select    |      |      |      |        |      |

| AC                       | RW    | Auxiliary car | ry flag     |      |      |      |        |      |

| CY                       | RW    | Carry flag    |             |      |      |      |        |      |

V0.1

November 2007

SP: **Stack Pointer Register** TYPE: R/W ADDRESS: 0x81 Bit0 Position Bit7 Bit6 Bit5 Bit4 Bit3 Bit2 Bit1 Mnemonic SP Default 00000111 SPH: Stack Pointer High Byte Register TYPE: R/W ADDRESS: 0x9B Position Bit7 Bit6 Bit5 Bit4 Bit3 Bit2 Bit1 Bit0 Mnemonic SPH Default 0000000 Description Setting SPH and SP registers are combined to form a 16-bit stack pointer when SPXSEL in DPCON is '1' ACC: Accumulator Register TYPE: R/W ADDRESS: **OxEO** Position Bit7 Bit6 Bit5 Bit4 Bit3 Bit2 Bit1 Bit0 Mnemonic ACC Default 0000000 B: **B** Register TYPE: R/W ADDRESS: 0xF0 Position Bit7 Bit6 Bit5 Bit2 Bit1 Bit0 Bit4 Bit3 Mnemonic В Default 0000000

November 2007

### 3.11 Special Function Registers (SFR)

### **3.11.1** SFR table listed in alphabetical order

The unimplemented bits are labelled '-', never write value other than its reset value to it, otherwise unpredictable effects will be resulted. Some registers have undetermined reset value, it is labelled 'X'.

November 2007

| Register |                            |         | Bit Functions |       |          |          |       |       |        |        |           |  |

|----------|----------------------------|---------|---------------|-------|----------|----------|-------|-------|--------|--------|-----------|--|

| Name     | Description                | Address | MSB           |       |          |          |       |       |        | LSB    | Reset     |  |

| ACC      | Accumulator                | 0xE0    |               |       |          |          |       |       |        |        | 0000 0000 |  |

| ADCB     | ADC buffer                 | 0xEE    |               |       |          |          |       |       |        |        |           |  |

| ADCCON0  | ADC control 0              | 0xF4    | ADCPND        | INBUF | REFS     | TM       | TC[1] | TC[0] | GO     | ADCEN  | 0000 0000 |  |

| ADCCON1  | ADC control 1              | 0xF5    | CM            | GT    | -        | REFBE    | -     | AS[2] | AS[1]  | AS[0]  | 0000 0000 |  |

| ADCSC    | ADC sampling clock control | 0xF3    |               |       |          |          |       | -     | -      |        | 0000 0000 |  |

| ADCT     | ADC threshold              | 0xF1    |               |       |          |          |       |       |        |        | XXXX XXXX |  |

| В        | B register                 | 0xF0    |               |       |          |          |       |       |        |        | 0000 0000 |  |

| CCON     | CPU control                | 0xAB    | PROT          | -     | LPM      | ISRM     | XMAP  | -     | -      | -      | 0000 0000 |  |

| CKCON0   | Clock control 0            | 0x91    | -             | -     | LPOSC    | PLLEN    | -     | SCPLL | SCS    | SCKD   | 0000 0000 |  |

| CKCON1   | Clock control 1            | 0x92    | FFCKE         | 32CKE | RTCKE    | MCKE     | PCKE  | -     | TCKE   | UCKE   | 0001 1110 |  |

| CKCON2   | Clock control2             | 0x93    | -             | -     | -        | -        | -     | CKS   | 32CE   | HSCE   | 0000 1101 |  |

| CLKDIV   | Clock divider              | 0x94    |               |       |          |          |       |       |        |        | 0000 0000 |  |

| DP1H     | Data pointer 1 high byte   | 0x85    |               |       |          |          |       |       |        |        | 0000 0000 |  |

| DP1L     | Data pointer 1 low byte    | 0x84    |               |       |          |          |       |       |        |        | 0000 0000 |  |

| DPCON    | Data pointer control       | 0x86    | DPID1         | DPID0 | DPTSE    | DPAID    | -     | EMIEN | SPXSEL | DPS    | 0000 0000 |  |

| DPH      | Data pointer high byte     | 0x83    |               |       |          |          |       | -     | -      |        | 0000 0000 |  |

| DPL      | Data pointer low byte      | 0x82    |               |       |          |          |       |       |        |        | 0000 0000 |  |

| EMICON1  | EMI control 1              | 0x8E    | RW[3]         | RW[2] | RW[1]    | RW[0]    | HD[1] | HD[0] | SET[1] | SET[0] | 1111 1111 |  |

| EMICON2  | EMI control 2              | 0x8F    | -             | SZ[1] | SZ[0]    | -        | PSON  | MUX   | WRON   | AL     | 0100 1111 |  |

| FIFOCON  | FIFO interface control     | 0x9C    | FEN           | ONLY  | -        | -        | -     | -     | WR     | RD     | 0000 0000 |  |