Distributed by:

JAMECO

ELECTRONICS

## www.Jameco.com + 1-800-831-4242

The content and copyrights of the attached material are the property of its owner.

Jameco Part Number 43191

Jameco Part Number 43191

R650X ● R651X

## **R650X and R651X Microprocessors (CPU)**

## DESCRIPTION

The 8-bit R6500 microprocessor devices are produced with N-channel, silicon gate technology. Performance speeds are enhanced by advanced system architecture. This innovative architecture results in smaller chips—the semiconductor threshold is cost-effectivity. System cost-effectivity is further enhanced by providing a family of 10 software-compatible microprocessor (CPU) devices, described in this document. Rockwell also provides single chip microcomputers, memory and peripheral devices-as well as low-cost design aids and documentation.

Ten CPU devices are available. All are software-compatible. They provide options of addressable memory, interrupt input, on-chip clock oscillators and drivers. All are bus-compatible with earlier generation microprocessors like the M6800 devices.

The R650X and R651X family includes six microprocessors with on-board clock oscillators and drivers and four microprocessors driven by external clocks. The on-chip clock versions are aimed at high performance, low cost applications where single phase inputs, crystal or RC inputs provide the time base. The external clock versions are geared for multiprocessor system applications where maximum timing control is mandatory. All R6500 microprocessors are also available in a variety of packaging (ceramic and plastic), operating frequency (1 MHz, 2 MHz and 3 MHz) and temperature (commercial and industrial) versions.

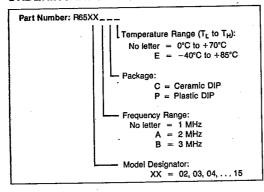

## **ORDERING INFORMATION**

#### **FEATURES**

- N-channel, silicon gate, depletion load technology

- 8-bit parallel processing

- 56 instructions

- Decimal and binary arithmetic

- Thirteen addressing modes

- True indexing capability

- Programmable stack pointer

- Variable length stack

- Interrupt request

- Non-maskable interrupt

- Use with any type of speed memory

- 8-bit bidirectional data bus

- Addressable memory range of up to 64K bytes

- "Ready" input

- Direct Memory Access capability

- Bus compatible with M6800

- 1 MHz, 2 MHz, and 3 MHz versions

- · Choice of external or on-chip clocks

- On-chip clock options

- -External single clock input

- -Crystal time base input

- Commercial and industrial temperature versions

- Pipeline architecture

- Single +5V supply

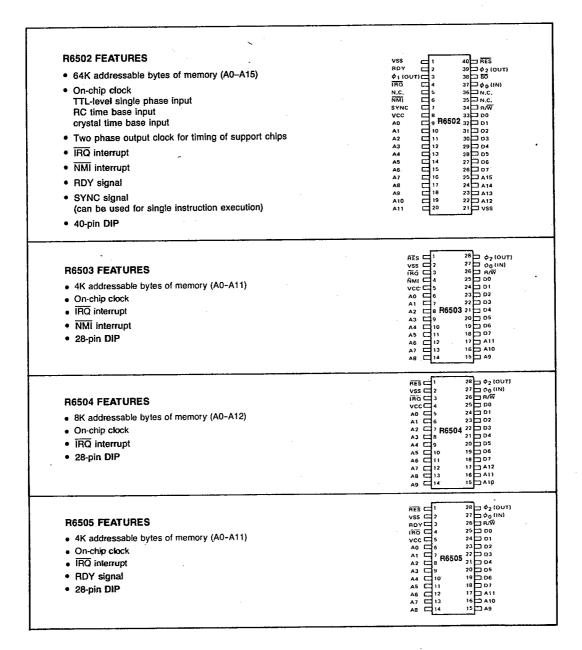

## **R6500 CPU FAMILY MEMBERS**

| Microproces | ssors with Internal To | wo Phase Clock Generator |

|-------------|------------------------|--------------------------|

| Mode!       | No. Pins               | Addressable Memory       |

| R6502       | 40                     | 64K Bytes                |

| R6503       | 28                     | 4K Bytes                 |

| R6504       | 28                     | 8K Bytes                 |

| R6505       | -28                    | 4K Bytes                 |

| R6506       | 28                     | 4K Bytes                 |

| R6507       | 28                     | 8K Bytes                 |

| Micropro    | cessors with Externa   | I Two Phase Clock Input  |

| Model       | No. Pins               | Addressable Memory       |

| R6512       | 40                     | 64K Bytes                |

| R6513       | 28                     | 4K Bytes                 |

| R6514       | 28                     | 8K Bytes                 |

| R6515       | 28                     | 4K Bytes                 |

Document No. 29000D39

**Data Sheet**

Order No. D39 Rev. 8, June 1987

## INTERFACE SIGNAL DESCRIPTIONS

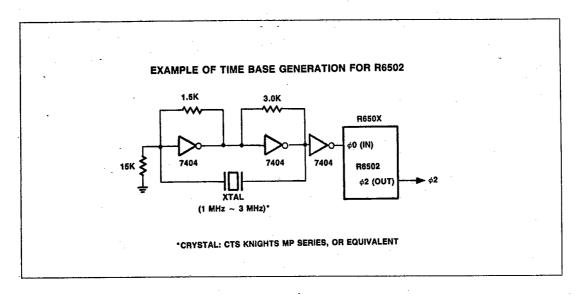

#### **CLOCKS (Ø1, Ø2)**

The R651X requires a two phase non-overlapping clock that runs at the  $V_{\rm CC}$  voltage level. The R650X clocks are supplied with an internal clock generator. The frequency of these clocks is externally controlled.

## ADDRESS BUS (A0-A15)

The address line outputs access data in memory device locations or cells, access data in I/O device registers and/or effect logical operations in I/O or controller devices depending on system design. The addressing range is determined by the number of address lines available on the particular CPU device. The R6502 and R6512 can address 64K bytes with a 16-bit address bus (A0-A15); the R6504, R6507, and the R6514 can address 8K bytes with a 13-bit address bus (A0-A12); and the R6503, R6505, R6506, R6513, and R6515 can address 4K bytes with a 12-bit address bus (A0-A11). These outputs are TTL-compatible and are capable of driving one standard TTL load and 130 pF.

#### DATA BUS (D0-D7)

The data lines (D0-D7) form an 8-bit bidirectional data bus which transfers data between the CPU and memory or peripheral devices. The outputs are tri-state buffers capable of driving one standard TTL load and 130 pF.

## DATA BUS ENABLE (DBE, R6512 ONLY)

The TTL-compatible DBE input allows external control of the tristate data output buffers and will enable the microprocessor bus driver when in the high state. In normal operation DBE is driven by the phase two (\$\mathcal{B}^2\$) clock, thus allowing data output from microprocessor only during \$\mathcal{B}^2\$. During the read cycle, the data bus drivers are internally disabled, becoming essentially an open circuit. To disable data bus drivers externally, DBE should be held low.

#### READY (RDY)

The Ready input signal allows the user to halt or single cycle the microprocessor on all cycles except write cycles. A negative transition to the low state during or coincident with phase one (£1) will halt the microprocessor with the output address lines reflecting the current address being fetched. If Ready is low during a write cycle, it is ignored until the following read operation. This condition will remain through a subsequent phase two (£2) in which the Ready signal is low. This feature allows microprocessor interfacing with the low speed PROMs as well as Direct Memory Access (DMA).

#### INTERRUPT REQUEST (IRQ)

The TTL level active-low IRQ input requests that an interrupt sequence begin within the microprocessor. The microprocessor will complete the current instruction being executed before recognizing the request. At that time, the interrupt mask bit in the Processor Status Register will be examined. If the interrupt mask flag is not set, the microprocessor will begin an interrupt sequence. The Program Counter and Processor Status Register

are stored in the stack. The microprocessor will then set the interrupt mask flag high so that no further interrupts can occur. At the end of this cycle, the program counter low will be loaded from address FFFE, and program counter high from location FFFF, therefore transferring program control to the memory vector located at these addresses. The RDY signal must be in the high state for any interrupt to be recognized. A  $3\mathrm{K}\Omega$  external resistor should be used for proper wire-OR operation.

#### NON-MASKABLE INTERRUPT (NMI)

A negative going edge on the  $\overline{\text{NM}}$  input requests that a non-maskable interrupt sequence be generated within the microprocessor.

NMI is an unconditional interrupt. Following completion of the current instruction, the sequence of operations defined for IRQ will be performed, regardless of the state interrupt mask flag. The vector address loaded into the program counter, low and high, are locations FFFA and FFFB respectively, thereby transferring program control to the memory vector located at these addresses. The instructions loaded at these locations cause the microprocessor to branch to a non-maskable interrupt routine in memory.

$\overline{\text{NMI}}$  also requires an external 3K $\Omega$  register to  $V_{\text{CC}}$  for proper wire-OR operations.

Inputs IRQ and NMI are hardware interrupts lines that are sampled during Ø2 (phase 2) and will begin the appropriate interrupt routine on the Ø1 (phase 1) following the completion of the current instruction.

## SET OVERFLOW FLAG (SO)

A negative going edge on the SO input sets the overflow bit in the Processor Status Register. This signal is sampled on the trailing edge of \$1 and must be externally synchronized.

#### SYNC

The SYNC output line identifies those cycles in which the microprocessor is doing an OP CODE fetch. The SYNC line goes high during \$1 of an OP CODE fetch and stays high for the remainder of that cycle. If the RDY line is pulled low during the \$1 clock pulse in which SYNC went high, the processor will stop in its current state and will remain in the state until the RDY line goes high. In this manner, the SYNC signal can be used to control RDY to cause single instruction execution.

## RESET (RES)

The active low  $\overline{\text{RES}}$  resets, or starts, the microprocessor from a power down or restart condition. During the time that this line is held low, writing to or from the microprocessor is inhibited. When a positive edge is detected on the input, the microprocessor will immediately begin the reset sequence.

After a system initialization time of six clock cycles, the mask interrupt flag is set and the microprocessor loads the program counter from the memory vector locations FFFC and FFFD, This is the start location for program control.

After  $V_{CC}$  reaches 4.75 volts in a power up routine, reset must be held low for at least two clock cycles. At this time the  $R/\overline{W}$  and SYNC signals become valid.

T-49-17-06

T-49-17-06

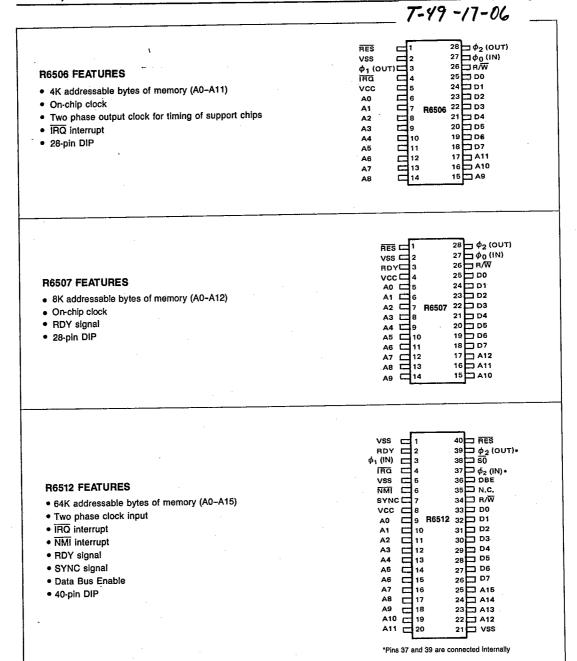

## **R6513 FEATURES**

- 4K addressable bytes of memory (A0-A11)

- · Two phase clock input

- IRQ interrupt

- NMI interrupt

- 28-pin DIP

2

## **R6514 FEATURES**

- 8K addressable bytes of memory (A0-A12)

- Two phase clock input

- IRQ interrupt

- 28-pin DIP

## R6515 FEATURES

- 4K addressable bytes of memory (A0-A11)

- Two phase clock input

- IRQ interrupt

- RDY signal

- 28-pin DIP

## **FUNCTIONAL DESCRIPTION**

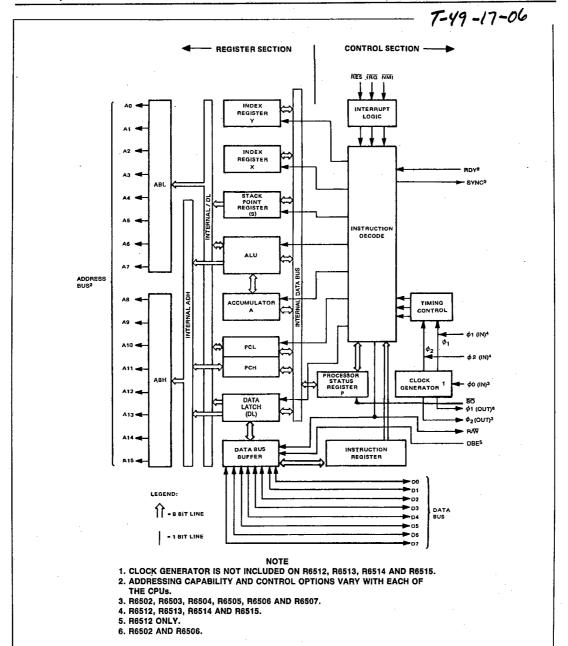

The internal organization of all R6500 CPUs is identical except for some variations in clock interface, the number of address output lines, and some unique input/output lines between versions.

## **CLOCK GENERATOR**

The clock generator develops all internal clock signals, and (where applicable) external clock signals, associated with the device. It is the clock generator that drives the timing control unit and the external timing for slave mode operations.

#### TIMING CONTROL

The timing control unit keeps track of the instruction cycle being monitored. The unit is set to zero each time an instruction fetch is executed and is advanced at the beginning of each phase one clock pulse for as many cycles as is required to complete the instruction. Each data transfer which takes place between the registers depends upon decoding the contents of both the instruction register and the timing control unit.

#### PROGRAM COUNTER

The 16-bit program counter provides the addresses which step the microprocessor through sequential instructions in a program.

Each time the microprocessor fetches an instruction from program memory, the lower byte of the program counter (PCL) is placed on the low-order bits of the address bus and the higher byte of the program counter (PCH) is placed on the high-order 8 bits. The counter is incremented each time an instruction or data is fetched fromprogram memory.

## INSTRUCTION REGISTER AND DECODE

Instructions fetched from memory are gated onto the internal data bus. These instructions are latched into the instruction register, then decoded, along with timing and interrupt signals, to generate control signals for the various registers.

## R6500 Microprocessors (CPU) 7-49-17-06

## ARITHMETIC AND LOGIC UNIT (ALU)

All arithmetic and logic operations take place in the ALU including incrementing and decrementing internal registers (except the program counter). The ALU has no internal memory and is used only to perform logical and translent numerical operations.

#### **ACCUMULATOR**

The accumulator is a general purpose 8-bit register that stores the results of most arithmetic and logic operations, and in addition, the accumulator usually contains one of the two data words used in these operations.

#### **INDEX REGISTERS**

There are two 8-bit index registers (X and Y), which may be used to count program steps or to provide an index value to be used in generating an effective address.

When executing an instruction which specifies indexed addressing, the CPU fetches the op code and the base address, and modifies the address by adding the index register to it prior to performing the desired operation. Pre- or post-indexing of indirect addresses is possible (see addressing modes).

#### STACK POINTER

The stack pointer is an 8-bit register used to control the addressing of the variable-length stack on page one. The stack pointer is automatically incremented and decremented under control of the microprocessor to perform stack manipulations under direction of either the program or interrupts  $(\overline{\text{NMI}})$  and  $\overline{\text{IRQ}})$ . The stack allows simple implementation of nested subroutines and multiple level interrupts. The stack pointer should be initialized before any interrupts or stack operations occur.

## PROCESSOR STATUS REGISTER

The 8-bit processor status register contains seven status flags. Some of the flags are controlled by the program, others may be controlled both by the program and the CPU.

## **R6500 Microprocessors (CPU)**

R650X and R651X Internal Architecture

## R650X, R651X

## **INSTRUCTION SET**

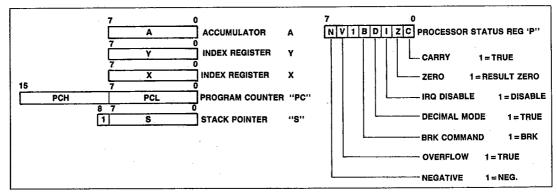

The R6500 CPU has 56 instruction types which are enhanced by up to 13 addressing modes for each instruction. The Accumulator, index registers, Program Counter, Stack Pointer and Processor Status Register are Illustrated below.

## Alphabetic Listing of Instruction Set

| Mnemonic | Function                                   | Mnemonic | Function                                     |

|----------|--------------------------------------------|----------|----------------------------------------------|

| ADC      | Add Memory to Accumulator with Carry       | JMP      | Jump to New Location                         |

| AND      | "AND" Memory with Accumulator              | JSR      | Jump to New Location Saving Return Address   |

| ASL      | Shift Left One Bit (Memory or Accumulator) |          | ,                                            |

|          | ,                                          | LDA      | Load Accumulator with Memory                 |

| всс      | Branch on Carry Clear .                    | LDX      | Load Index X with Memory                     |

| BCS      | Branch on Carry Set                        | LDY      | Load Index Y with Memory                     |

| BEQ      | Branch on Result Zero                      | LSR      | Shift One Bit Right (Memory or Accumulator)  |

| BIT      | Test Bits in Memory with Accumulator       |          |                                              |

| вмі      | Branch on Result Minus                     | NOP      | No Operation                                 |

| BNE      | Branch on Result not Zero                  |          |                                              |

| BPL      | Branch on Result Plus                      | ORA      | "OR" Memory with Accumulator                 |

| BRK      | Force Break                                |          | , '                                          |

| BVC      | Branch on Overflow Clear                   | PHA      | Push Accumulator on Stack                    |

| BVS      | Branch on Overflow Set                     | PHP      | Push Processor Status on Stack               |

|          |                                            | PLA      | Pull Accumulator from Stack                  |

| CLC      | Clear Carry Flag                           | PLP      | Pull Processor Status from Stack             |

| CLD      | Clear Decimal Mode                         |          |                                              |

| CLI      | Clear Interrupt Disable Bit                | ROL      | Rotate One Bit Left (Memory or Accumulator)  |

| CLV      | Clear Overflow Flag                        | ROR      | Rotate One Bit Right (Memory or Accumulator) |

| CMP      | Compare Memory and Accumulator             | RTI      | Return from Interrupt                        |

| CPX      | Compare Memory and Index X                 | RTS      | Return from Subroutine                       |

| CPY      | Compare Memory and Index Y                 | }        |                                              |

|          | •                                          | SBC      | Subtract Memory from Accumulator with Borrow |

| DEC      | Decrement Memory by One                    | SEC      | Set Carry Flag                               |

| DEX      | Decrement Index X by One                   | SED      | Set Decimal Mode                             |

| DEY      | Decrement Index Y by One                   | SEI      | Set Interrupt Disable Status                 |

|          |                                            | STA      | Store Accumulator in Memory                  |

| EOR      | "Exclusive-OR" Memory with Accumulator     | STX      | Store Index X in Memory                      |

| 1        |                                            | STY      | Store Index Y in Memory                      |

| INC      | Increment Memory by One                    |          | '                                            |

| INX      | Increment Index X by One                   | TAX      | Transfer Accumulator to Index X              |

| INY      | Increment Index Y by One                   | TAY      | Transfer Accumulator to Index Y              |

|          |                                            | TSX      | Transfer Stack Pointer to Index X            |

|          |                                            | TXA      | Transfer Index X to Accumulator              |

|          |                                            | TXS      | Transfer Index X to Stack Register           |

|          |                                            | TYA      | Transfer Index Y to Accumulator              |

**Programming Model**

## T-49-17-06

## R650X, R651X

## R651X R6500 Microprocessor (CPU)

## ADDRESSING MODES

The R6500 CPU family has 13 addressing modes. In the following discussion of these addressing modes, a bracketed expression follows the title of the mode. This expression is the term used in the Instruction Set Op Code Marix table (later in this product description) to make it easier to identify the actual addressing mode used by the instruction.

ACCUMULATOR ADDRESSING [Accum]—This form of addressing is represented with a one byte instruction, implying an operation on the accumulator.

IMMEDIATE ADDRESS [IMM]—In immediate addressing, the second byte of the instruction contains the operand, with no further memory addressing required.

ABSOLUTE ADDRESSING [Absolute]—In absolute addressing, the second byte of the instruction specifies the eight low order bits of the effective address while the third byte specifies the eight high order bits. Thus, the absolute addressing mode allows access to the entire 64K bytes of addressable memory.

ZERO PAGE ADDRESSING [ZP]—The zero page instructions allow for shorter code and execution times by fetching only the second byte of the instruction and assuming a zero high address byte. Careful use of the zero page can result in significant increase in code efficiency.

INDEXED ZERO PAGE ADDRESSING [ZP, X or Y]—This form of addressing is used with the index register and is referred to as "Zero Page, X" or "Zero Page, Y". The effective address is calculated by adding the second byte to the contents of the index register. Since this is a form of "Zero Page" addressing, the content of the second byte references a location in page zero. Additionally, due to the "Zero Page" addressing nature of this mode, no carry is added to the high order eight bits of memory and crossing of page boundaries does not occur.

INDEXED ABSOLUTE ADDRESSING [ABS, X or Y]—This form of addressing is used in conjunction with X and Y index register and is referred to as "Absolute, X" and "Absolute, Y." The effective address is formed by adding the contents of X or Y to the address contained in the second and third bytes of the instruction. This mode allows the index register to contain the index or count value and the instruction to contain the base

address. This type of indexing allows referencing of any location and the index may modify multiple fields, resulting in reduced coding and execution time.

IMPLIED ADDRESSING [Implied]—In the implied addressing mode, the address containing the operand is implicitly stated in the operation code of the instruction.

**RELATIVE ADDRESSING [Relative]**—Relative addressing is used only with branch instructions and establishes a destination for the conditional branch.

The second byte of the instruction is an operand. This operand is an offset which is added to the program counter when the counter is set at the next instruction. The range of the offset is -128 to +127 bytes.

INDEXED INDIRECT ADDRESSING [(IND, X)]—In indexed indirect addressing (referred to as (indirect, X)), the second byte of the instruction is added to the contents of index register X discarding the carry. The result of this addition points to a memory location on page zero which contains the low order byte of the effective address. The next memory location in page zero contains the high order byte of the effective address. Both memory locations specifying the effective address must be in page zero.

INDIRECT INDEXED ADDRESSING [(IND), Y)]—In indirect indexed addressing (referred to as (Indirect), Y), the second byte of the instruction points to a memory location in page zero. The contents of this memory location are added to the contents of index register Y. The result is the low order byte of the effective address. The carry from this addition is added to the contents of the next page zero memory location, to form the high order byte of the effective address.

ABSOLUTE INDIRECT [Indirect]—The second byte of the instruction contains the low order byte of a memory location. The high order eight bits of that memory location are contained in the third byte of the instruction. The contents of the fully specified memory location are the low order byte of the effective address. The next memory location contains the high order byte of the effective address which is loaded into the sixteen bits of the program counter. (JMP (IND) only)

## R6500 Microprocessors (CPU)

## T-49 -17-06

## INSTRUCTION SET OP CODE MATRIX

The following matrix shows the Op Codes associated with the R6500 family of CPU devices. The matrix identifies the hexadecimal code, the mnemonic code, the addressing mode, the

number of instruction bytes, and the number of machine cycles associated with each Op Code. Also, refer to the instruction set summary for additional information on these Op Codes.

| _ LS | SD 0                     | 1                       | 2                 | 3 | 4                   | 5                   | 6                   | 7 | 8                     | 9                     | A                     | В        | C                      | D                     | E                    | F        |   |

|------|--------------------------|-------------------------|-------------------|---|---------------------|---------------------|---------------------|---|-----------------------|-----------------------|-----------------------|----------|------------------------|-----------------------|----------------------|----------|---|

| WSD  | BRK<br>Implied<br>1 7    | ORA<br>(IND, X)<br>2 6  |                   |   |                     | ORA<br>ZP<br>2 3    | ASL<br>ZP<br>2 5    |   | PHP<br>Implied<br>1 3 | ORA<br>IMM<br>2 2     | ASL<br>Accum<br>1 2   |          |                        | ORA<br>ABS<br>3 4     | ASL<br>ABS<br>3 6    |          | o |

| 1    | BPL<br>Relative<br>2 2"  | ORA<br>(IND), Y<br>2 5' |                   |   |                     | ORA<br>ŽP, X<br>2 4 | ASL<br>ZP, X<br>2 6 |   | CLC<br>Implied<br>1 2 | ORA<br>ABS, Y<br>3 4° |                       |          |                        | ORA<br>ABS, X<br>3 4* | ASL<br>ABS, X<br>3 7 |          | 1 |

| 2    | JSR<br>Absolute<br>3 6   | AND<br>(IND, X)<br>2 6  |                   |   | BIT<br>ZP<br>2 .3   | AND<br>ZP<br>2 3    | ROL<br>ZP<br>2 5    |   | PLP<br>Implied<br>1 4 | AND<br>IMM<br>2 2     | ROL<br>Accum<br>1 2   |          | BIT<br>ABS<br>3 4      | AND<br>ABS<br>3 4     | ROL<br>ABS<br>3 6    |          | 2 |

| . 3  | BMI<br>Relative<br>2 2** | AND<br>(IND), Y<br>2 5* | -                 |   |                     | AND<br>ZP, X<br>2 4 | ROL<br>ZP, X<br>2 6 |   | SEC<br>Implied<br>1 2 | AND<br>ABS, Y<br>3 4° |                       |          |                        | AND<br>ABS, X<br>3 4° | ROL<br>ABS, X<br>3 7 |          | 3 |

| 4    | RTI<br>Implied<br>1 6    | EOR<br>(IND, X)<br>2 6  |                   |   |                     | EOR<br>ZP<br>2 3    | LSR<br>ZP<br>2 5    |   | PHA<br>Implied<br>1 3 | EOR<br>IMM<br>2 2     | LSR<br>Accum<br>1 2   |          | JMP<br>ABS<br>3 3      | EOR<br>ABS<br>3 4     | LSR<br>ABS<br>3 6    |          | 4 |

| 5    | BVC<br>Relative<br>2 2"  | EOR<br>(IND), Y<br>2 5* |                   |   |                     | EOR<br>ZP, X<br>2 4 | LSR<br>ZP, X<br>2 6 |   | CLI<br>Implied<br>1 2 | EOR<br>ABS, Y<br>3 4  |                       |          |                        | EOR<br>ABS, X<br>3 4  | LSR<br>ABS, X<br>3 7 |          | 5 |

| 6    | RTS<br>Implied<br>1 6    | ADC<br>(IND, X)<br>2 6  |                   |   |                     | ADC<br>ZP<br>2 3    | ROR<br>ZP<br>2 5    |   | PLA<br>Implied<br>1 4 | ADC<br>IMM<br>2 2     | ROR<br>Accum<br>1 2   |          | JMP<br>Indirect<br>3 5 | ADC<br>ABS<br>3 4     | ROR<br>ABS<br>3 6    |          | 6 |

| 7    | BVS<br>Relative<br>2 2"  | ADC<br>(IND), Y<br>2 5* |                   |   |                     | ADC<br>ZP, X<br>2 4 | ROR<br>ZP, X<br>2 6 |   | SEI<br>Implied<br>1 2 | ADC<br>ABS, Y<br>3 4' |                       |          |                        | ADC<br>ABS, X<br>3 4* | ROR<br>ABS, X<br>3 7 |          | 7 |

| 8    |                          | STA<br>(IND, X)<br>2 6  |                   |   | STY<br>ZP<br>2 3    | STA<br>ZP<br>2 3    | STX<br>ZP<br>2 3    |   | DEY<br>Implied<br>1 2 |                       | TXA<br>Implied<br>1 2 |          | ABS<br>3 4             | STA<br>ABS<br>3 4     | STX<br>ABS<br>3 4    |          | 8 |

| 9    | BCC<br>Relative<br>2 2"  | STA<br>(IND), Y<br>2 6  |                   |   | STY<br>ZP, X<br>2 4 | STA<br>ZP, X<br>2 4 | STX<br>ZP, Y<br>2 4 |   | TYA<br>Implied<br>1 2 | STA<br>ABS, Y<br>3 5  | TXS<br>Implied<br>1 2 |          |                        | STA<br>ABS, X<br>3 5  |                      |          | 9 |

| A    | LDY<br>IMM<br>2 2        | LDA<br>(IND, X)<br>2 6  | LDX<br>IMM<br>2 2 |   | LDY<br>ZP<br>2 3    | LDA<br>ZP<br>2 3    | LDX<br>ZP<br>2 3    |   | TAY<br>Implied<br>1 2 | IMM<br>2 2            | TAX<br>Implied<br>1 2 |          | ABS<br>3 4             | ABS<br>3 4            | ABS<br>3 4           |          | A |

| В    | BCS<br>Relative<br>2 2"  | LDA<br>(IND), Y<br>2 5* |                   |   | LDY<br>ZP, X<br>2 4 | LDA<br>ZP, X<br>2 4 | LDX<br>ZP, Y<br>2 4 |   | CLV<br>Implied<br>1 2 | LDA<br>ABS, Y<br>3 4° | TSX<br>Implied<br>1 2 |          | ABS, X<br>3 4          | 3 4'                  | 3 4                  |          | В |

| С    | CPY<br>IMM<br>2 2        | CMP<br>(IND, X)<br>2 6  |                   |   | CPY<br>ZP<br>2 3    | CMP<br>ZP<br>2 3    | DEC<br>ZP<br>2 5    |   | INY<br>Implied<br>1 2 | IMM<br>2 2            | DEX<br>Implied<br>1 2 |          | CPY<br>ABS<br>3 4      | ABS<br>3 4            | DEC<br>ABS<br>3 6    |          | С |

| D    | BNE<br>Relative<br>2 2** | CMP<br>(IND), Y<br>2 5* |                   |   |                     | CMP<br>ZP, X<br>2 4 | DEC<br>ZP, X<br>2 6 |   | CLD<br>Implied<br>1 2 | 3 4                   | <u> </u>              | <u> </u> | ļ _                    | CMP<br>ABS, X<br>3 4" | 3 7                  |          | P |

| E    | CPX<br>IMM<br>2 2        | SBC<br>(IND, X)<br>2 6  |                   |   | CPX<br>ZP<br>2 3    | SBC<br>ZP<br>2 3    | INC<br>ZP<br>2 5    |   | INX<br>Implied<br>1 2 | 2 2                   | NOP<br>Implied<br>1 2 |          | CPX<br>ABS<br>3 4      | SBC<br>ABS<br>3 4     | INC<br>ABS<br>3 6    |          | E |

| F    | BEQ<br>Relative<br>2 2"  | SBC<br>(IND), Y<br>2 5* |                   |   |                     | SBC<br>ZP, X<br>2 4 | INC<br>ZP, X<br>2 6 |   | SED<br>Implied<br>1 2 | SBC<br>ABS, Y<br>3 4* |                       |          |                        | SBC<br>ABS, X<br>3 4° | 3 7                  | <u> </u> | F |

|      | 0                        | 1                       | 2                 | 3 | 4                   | 5                   | 6                   | 7 | 8                     | 9                     | A.                    | В        | С                      | D                     | E                    | F        |   |

<sup>0</sup>BRK implied — OP Code — Addressing Mode — Instruction Bytes; Machine Cycles

<sup>\*</sup>Add 1 to N if page boundary is crossed.

\*\*Add 1 to N if branch occurs to same page;

add 2 to N if branch occurs to different page.

T-49-17-06

## **INSTRUCTION SET SUMMARY**

|          | INSTRUCTIONS                                     |     | мер  | ATE | AB       | SOLI | DTE  | ZE       | LO PA | IGE  | A   | CUM      |        | IM       | PLIED        | , [ | (IX | D. X | ī   | (IH | 01, Y     | 7            | PAC | SE, X      |                 | 185. | I   | _      | BS.  | 7   | REI      | ATR | rE.      | IHC | PIRE | CT | 2        | PAG     | E.Y  | 10  | PACCESSOR STA          |                  |          |

|----------|--------------------------------------------------|-----|------|-----|----------|------|------|----------|-------|------|-----|----------|--------|----------|--------------|-----|-----|------|-----|-----|-----------|--------------|-----|------------|-----------------|------|-----|--------|------|-----|----------|-----|----------|-----|------|----|----------|---------|------|-----|------------------------|------------------|----------|

| MHEMONIC | OPERATION                                        | OР  | 'n   |     | QР       | 'n   |      | ОP       | c     | •    | OP  | ٠        | 7      | OΡ       | n.           | • ( | )P  | n    | •   | ЭP  | n.        | . 0          | P   | •          | OF              | ٥    |     | ОP     | n    |     | OР       | n   | •        | OP  | n    | Ŀ  | OF       | n       |      | 1   | 7 6 5 4 J<br>N V • B D | 2 1 0<br>1 2 C   | MHEMONIC |

| ADC      | A+M+E-A (4)(1)                                   | 69  | 2    | 2   | 60       | 4    | 3    | 65       | 3     | 2    |     | ٦        | $\neg$ | ╗        | $\neg$       |     |     |      |     |     | 5 3       |              |     | 2          | 70              |      | 1-  | 79     |      | 3   | П        | ╗   | ╗        |     |      | Г  | Г        | Г       | Г    | т.  | N V                    |                  | ADC      |

| AND      | ÄAM→A (1)                                        | 29  | 2    | 2   | 20       |      |      |          |       |      |     |          | -      | 1        |              |     | 21  | 6    | 2   | 31  | 5         |              |     |            |                 |      |     | 39     | 4    | 3   |          | -   | Į        |     |      |    |          |         | 1    | 1   | н                      |                  | AND      |

| ASL      | C+(r 0-0                                         | ı   | l    |     | 0E       | 6    | 3    | 06       | 5     | 2    | ØA. | 2        | ١      | - 1      |              | ١   |     | ł    | ١   | -1  |           | ŀ            | 6 6 | 3 2        | 1E              | 7    | 3   |        |      |     |          | -   | - 1      |     |      |    | ı        | ١.      | ı    | ľ   | м                      |                  |          |

| всс      | BRANCHONC = 0 (2)                                |     | ı    | 1   |          |      |      | 1        | Н     | Ш    |     |          |        | ١        | - 1          | 1   |     | -    | ١   |     |           | 1            | 1   | 1          |                 |      |     | ı      |      |     |          | 2   |          |     |      |    | l        | ļ       | l    | 1.  |                        |                  | B C C    |

| BCS      | BRANCHONG = 1 (2)                                | L   | L.   | ļ_  | <b>!</b> | L    | L    | Ļ        | Ш     | Ц    | Ц   |          | 4      | 4        | -i           | 4   | 4   | 4    | 4   | 4   | 4         | 4            | 4   | +          | 1-              | ⊢    | ╀   | ⊢      | H    | H   | В0       |     |          |     |      | ļ. | ┞        | ⊢       | ╀    | ť   |                        | <u> </u>         | BCS      |

| 8 E O    | BRANCH ON Z = 1 (2)                              |     |      |     | ١.       |      |      | l        |       |      |     | - 1      | - [    | - [      | - }          | -1  | -1  | ı    | -1  |     | ļ         | Т            | 1   | ŀ          | 1               | ١.   |     | ı      | ]    |     | FO       | 2   | 2        |     | -1   |    |          | 1       | ı    |     | <br>М, М,              |                  | BEQ      |

| BIT      | AAM                                              | ı   | 1    |     | 2C       | 1    | 3    | 24       | 3     | 2    |     | - [      | -      | ١        | -            |     |     | -    | ŀ   |     | - }       | ı            | ı   |            | l               | 1    | ŀ   | ı      |      |     |          | ŀ   | .        | -   |      |    | ľ        | ı       | l    |     | My Me.                 |                  | BMI      |

| BMI      | BRANCH ON N = 1 (2)<br>BRANCH ON Z = 0 (2)       |     |      |     | ı        |      |      | 1        | L     |      | 1   | 1        |        | ١        |              |     |     | 1    | 1   |     | ı         | ı            | ı   |            | l               | 1    | ŀ   | 1      |      |     | 30<br>00 |     | 2        | -   |      |    | ľ        | l       | 1    | 1.  |                        |                  | BNE      |

| BPL      | 8RANCHON 2 = 0 (2)                               |     | l    |     | 1        |      | ١    | ł        |       |      |     | 1        |        | -        | - 1          |     |     | 1    | 1   |     | ŀ         | ı            | ı   |            | ı               | l    |     | 1      |      |     | 1 1      | t   | 2        |     |      | Ì  | l        | l       |      | Ι.  |                        |                  | BPL      |

| BRK      | BREAK                                            | ╀╌  | ⊢    | ⊢   | ┢        | -    | ⊢    | ╌        | Н     | Н    | Н   | ┪        | ┪      | 00       | <del>,</del> | 1   | +   | +    | +   | +   | +         | +            | +   | +          | ┿               | ╁╌   | +-  | ╁╌     | Н    | Н   | ۳        | +   | ÷        | -   | -    | ┝  | ┢        | ╆       | †-   | ۲.  | 1 .                    | ١.,              | BRK      |

| BVC      | BRANCHONV = 0 (2)                                | ١.  | l    | 1   | l        |      |      | ı        | l     | 1    |     | - 1      |        | ``       | 1            | 1   |     | 1    | -   |     | 1         | 1            | 1   | 1          |                 | ı    | 1   | ı      | l    | l   | 50       | 2   | 2        |     |      |    | l        | l       | ł    | ١.  |                        |                  | вус      |

| BVS      | BRANCHONV = 1 (2)                                |     | l    |     | ļ.       |      |      | l        | i I   |      |     | 1        | -      | ١        | - 1          |     |     | -    | -   |     |           | ı            | ı   |            | ı               | l    | 1   | 1      | l    |     | 70       |     |          |     |      |    | ı        | l       |      | ١.  |                        |                  | BVS      |

| CLC      | 0-C                                              |     | l    | 1   |          |      |      |          | -     |      |     | 1        |        | 18       | 2            | 1   |     | -    | ľ   |     | - 1       |              | ı   |            | ı               | l    | 1   | 1      | l    |     |          | -   | ı        |     |      |    | l        | ı       |      | 1   |                        | 0                | Crc      |

| CLD      | 0 - D                                            | l   | l    | 1   |          |      |      | l        |       |      |     | - 1      |        | 08       | 2            | 1   |     | - 1  | 1   | ļ   |           | 1            | ı   |            | ı               | l    | 1   | l      | l    |     |          | -   | -        |     |      | ١  | ١        | <u></u> | L    | J.  |                        |                  | CLD      |

| CLI      | 0~1                                              | Ī   | Г    |     | 1        |      | Γ    |          | П     |      | П   | ╗        | ┪      | 58       | 2            | 1   | T   | Т    | 7   | ╗   | T         | Т            | Т   | Т          | Т               | Т    | Т   | Π      | Г    | П   |          | П   |          |     |      |    | Γ        | Π       | Г    | T   |                        | . 0              | CLI      |

| CLV      | 0 <b>-</b> ¥                                     |     | l    | 1   | 1        |      | l    | l        |       | ١,   |     | - 1      |        | 88       | 2            | 1   |     | - 1  | 1   | -   |           | -            | ı   | 1          | l               | l    | L   | l      | l    |     |          | -   | - 1      |     |      |    | 1        | ı       |      | 1   |                        |                  | CrA      |

| CMP      | A – M                                            | C9  | 2    | 2   | CO       | 4    | 3    | C5       | 3     | 2    | ļ   | .        |        | -        |              | •   | 21  | 6    | 2   | D1  | 5         | 2 D          | 5 4 | 1 2        | DC              | 4    | 3   | 09     | 4    | 3   | ı        | -   |          |     |      |    | 1        | l       |      | 1   |                        | ·zc              |          |

| CPX      | X – M                                            | ΕO  | 2    | 2   | EC       | 4    | 3    | E4       | 3     | 2    |     | - 1      | - [    | ı        |              |     |     | 1    | 1   | -   |           | 1            | 1   |            |                 | ı    | ı   | 1      | ļ    | l   |          | 1   | - [      |     |      | l  | l        |         | 1    | ŀ   | N · · · ·              |                  |          |

| CPY      | Y - M                                            | Сā  | 2    | 2   | cc       |      |      | C4       |       | 2    |     | _        | 4      | 4        | 4            | 4   | 4   | 4    | 4   | 4   | 4         | 4            | 4   | 4-         | ↓.              | ļ.,  | ╄   | ↓_     | L    |     | Ц        | 4   | 4        |     | Ш    | ļ  | Ļ.       | -       | ↓.   | 4:  |                        | . z c            | CPY      |

| DEC      | M - 1 → M                                        | l   |      | ŀ   | CE       | 6    | 3    | C6       | 5     | 2    |     |          | j      | .        | - [          | -   |     | -    | 1   | -   |           | ľ            | 6 6 | 5   Z      | DE              | 7    | 3   | 1      |      |     | П        | - 1 |          |     |      |    | l        |         |      | -1  | N                      |                  | DEC      |

| DEX      | X - 1 → X.                                       |     | l    | Ī   | ŀ        |      |      | l        |       |      | ı   | 1        |        | CA       |              | 1   | 4   | ı    | -   | -   |           | ı            |     | 1          | ı               |      | Ī   | 1      |      |     | Ιİ       | ı   |          |     |      | ŀ  | l        | l       |      | -11 | N                      |                  | OEX      |

| DEY      | Y - 1 - Y                                        | 1   | l    | l   | ŀ        | Ì    |      | 1        |       |      |     | ٠ ا      | - 1    | 88       | 2            | ١   |     | . 1  |     | _ 1 | .         | Л.           | 1.  | ١.         | l.,             | ١.   | ١.  | ١      |      |     | l        | ł   |          |     |      | 1  | l        | 1       |      | ľ   | N                      |                  | DEY      |

| EOR      |                                                  | 49  | 2    | 2   | 4D       |      |      |          |       |      |     | - 1      | - 1    | -        | -            | ľ   | "   | ٥    | 2   | ۱۰۰ | 5         |              |     | 5 2        | 50              |      |     | 59     | 1    | 3   |          | · i |          |     |      |    | l        |         | l    | T.  | N                      |                  | INC      |

| INC      | M + 1 → M                                        | Ͱ   | H    | ┝   | EE       | -    | 3    | E6       | 5     | 2    | Н   | $\dashv$ | -      |          | +            | +   | +   | -+   | +   | -   | +         | - -          | 910 | 1          | <del> "</del>   | ť    | 13  | ╁      | ⊢    | ⊢   | ⊣        | ᅱ   | -        | -   | Н    | ⊢  | ╀        | ╁       | ٠    | _   | N                      |                  | INX      |

| INX      | X + 1 → X<br>Y' + 1 → Y                          |     | ŀ    | l   | l        |      | İ    | i        |       |      |     |          |        | €8<br>C8 |              |     | -   |      | - [ | - 1 |           | 1            |     |            | ı               | ı    | 1   | İ      |      |     |          | ı   | ١        |     |      | l  |          | l       | ŀ    |     | N                      |                  | INY      |

| TNA      | JUMP TO NEW LOC                                  | İ   | l    | l   | 4C       | ١.   | 3    |          | Ļ     |      |     |          | - 1    | ۳        | '            | 1   | 1   |      | - 1 | Ì   |           | Т            | ı   |            | ı               | İ    |     |        |      |     |          | .   |          | ŧC  |      | ١, | ı        | ł       | į    | Ľ   |                        |                  | JMP      |

| JSR      | JUMPSUB                                          | :   |      | ŀ   | 20       | 6    |      | ĺ        |       |      |     | ٠ ا      | - [    | ı        | 1            | ١   | 1   |      | -1  | J.  | .         | 1            |     |            | ı               | ĺ    |     |        |      |     | ۱.       | ١   | : 1      | ~   | 1    | ľ  | l        | l       |      | Ţ,  |                        |                  | JSR      |

| LDA      | M-A (1)                                          | AG  | ١,   | ١,  | AD       | i .  |      | 45       | 3     | ,    |     | ١        | -1     | 1        | ١            | - [ | A1  | 6    | 2   | в.  |           | 2 8          | اه  | . ا ،      | l <sub>ec</sub> | 4    | 13  | В9     | ١,   | نا  | H        | ٠ [ |          |     |      |    | ı        |         | i    | ١,  | N · · · ·              | · z ·            | LDA      |

| LOX      | M - X (1)                                        | -   | 2    |     | ΑE       |      | +-   | A6       | _     | 2    | Н   | 7        | ┪      | 7        | 7            | 7   | 7   | Ť    | Ť   | _   | 1         | ۳            | Ť   | T          | ۳               | ۲    | Ť   | BE     |      | 3   |          |     |          |     | П    | Γ  | ВЕ       | 4       | 1 2  |     | N                      | , <sub>2</sub> , | LOX      |

| LDY      | M→Y (I)                                          |     | 2    |     | AG       |      |      | A4       |       |      |     | ٠ ا      |        |          | 1            | -   | -   |      |     |     | į         | 6            | 4   | ı          | Вс              | 4    | 1 3 |        | Į    | ľ   |          | .   |          |     |      |    |          | ŀ       |      | 1   | м                      |                  | LDY      |

| tsR      | 0 – <u>₹                                    </u> |     | l    | l   |          |      |      | 46       |       | 2.   | 4A  | 2        | ١,     | -        | - 1          | - 1 |     | ļ    |     |     | - 1       | 5            | 6 0 | 6 2        | 56              | 7    | 3   |        |      |     |          | ļ   |          |     |      |    |          | 1       | ļ    | 1   | 0                      | z c              | LŞR      |

| NOP      | NO OPERATION                                     |     |      | ŀ   | ı        | l    |      | 1        |       |      |     |          |        | EA       | 2            | 1   | -   | ı    |     |     | - 1       | 1            |     | L          | ı               | ŀ    | 1   |        |      |     |          | ı   |          |     |      | 1  |          | ŀ       | l    | ı   |                        |                  | NOP      |

| ORA      | AVM-A                                            | 09  | 2    | 2   | 00       | 4    | 3    | 05       | 3     | 2    |     |          |        |          |              | _   | 01  | 6    | 2   | 11  | 5         | 2 1          | 5   | 1 2        | 10              | 4    | 3   | 19     | 4    | J   | Ш        | ┙   |          |     |      | L. | L        | L       | L    | Ŀ   | N · · · ·              | . z              | ORA      |

| PHA      | AMs S-1-S                                        | Γ   | Γ    |     | Г        | Γ    |      | Π        |       |      |     |          |        | 48       | 3            | ١   | 1   | - [  |     |     |           | Т            |     | 1          | П               |      |     | 1      |      |     | П        |     |          |     |      |    |          |         | 1    | ı   |                        |                  | PHA      |

| PHP      | P → Ms S - 1 → S                                 |     |      |     | l        | l    |      | 1        |       |      |     | - 1      | - 1    | 68       | -            | ١   | 1   | ł    | ł   | ١   | - 1       |              | ł   | 1          | ı               |      |     |        |      |     | П        |     |          |     |      |    |          |         |      | ı   |                        |                  | PHP      |

| PLA      | S+1-S M5-A                                       |     |      |     | ı        | ١.   |      | 1        |       |      |     |          |        | 68       | -            | ١١  | -   | - 1  | Ì   | Ì   | - 1       |              | ŀ   | 1          | 1               |      |     | 1      |      | l   | Ш        | ١   |          |     |      |    |          |         | 1    | ı   | н • • • •              |                  | PLA      |

| PLP      | S+1→S Ms→P                                       | ŀ   | 1    |     | L        | l.   |      | 1        |       |      |     |          | - 1    | 28       | 4            | 1   | 1   | 1    | ı   | Į   | - 1       | ١.           | 1.  | ١.         | l.,             | ١.   | ١.  | ı      | l    | ŀ   | П        | - 1 |          |     |      | l  | Ì        |         | 1    | I.  | IRESTO                 |                  | PLP      |

| ROL      | -6-3-6-                                          | ⊢   | ┞    | ⊢   | ZE       |      |      | 26       |       |      |     | 2        | 1      | $\dashv$ | 4            | 4   | +   | +    | 4   |     | +         |              | _   | _          | 36              | -    | +-  | ╀      | ⊢    | ╀╌  | Н        | ┥   | $\vdash$ | Н   | -    | ┝  | ╁        | ╀       | ╀    | -   | N                      | · Z C            | ·        |

| ROR      | RTRNINT                                          |     | 1    |     | 6E       | ١٥   | 13   | 66       | ٦     | 2    | 68  | 2        | 1      | 40       | اء           | .   | -   |      | ١   |     | -         | 1′           | 6   | 5   2      | 75              | 1    | 1   | 1      | l    | l   | Ш        |     |          |     |      | l  |          | İ       |      | ı   | RESTO                  |                  | RTI      |

| RIS      | RTRN SUB                                         |     |      | l   | 1        | l    | 1    |          | i I   |      |     |          |        | 60       | - 1          | ;1  | 1   | - 1  | -1  | - 1 | - 1       |              | Т   | 1          | 1               | ı    | 1   | ı      | ı    | ı   | Ш        |     |          |     |      | l  |          | ŀ       | ŀ    | ı   |                        |                  | RIS      |

| SBC      |                                                  | L.  | ١,   | ١,  | ΕO       | l.   | ١.   | ١.,      | ١,    | ١,   |     |          | l      | ~        | ľ۱           |     | ١,  | ۱ء   | ,   | ١,  | 5         | , ,          | ٠,  | ,ا،        | -               | ۱,   | ١,  | <br>F9 | I٠   | l٦  | Ш        |     |          |     |      | l  | 1        |         |      | ı   | N V · · ·              | · · z 13         |          |

| SEC      | 1-C                                              | ٦   | ۱    | ľ   | ۳        | ľ    | ľ    | ٦        | ا ا   | 1    | П   |          | 1      | 38       | 2            | ٦ľ  | -   | -    |     |     | -1        | ٦'           | 1   | Ι,         | Γ               | T    | 1   | Γ      | ľ    | ľ   | Ιl       |     |          |     |      | l  | 1        | 1       |      | 1   |                        | 1                | SEC      |

| SED      | 1-0                                              | l   | l    | 1   | ı        | 1    |      |          |       |      | П   |          |        | F8       |              | 1   | 1   |      | -   | J   |           |              |     |            |                 | 1    | 1   | 1      |      |     |          | ļ   |          |     |      |    | 1        | 1       |      | 1   |                        |                  | SED      |

| 5 E I    | 1-1                                              | ✝   | †    | t   | †-       | 1    | ✝    | 1-       | -     | 1    | Н   | $\dashv$ |        | 78       |              | 1   | 7   | 4    | 7   | ┪   | $\dashv$  | $^{\dagger}$ | +   | 1          | t               | t    | 1   | t      | t٠   | ٢   | Н        | 7   | -        | Н   | -    | T  | t        | t       | t    | t   |                        | 1                | SEI      |

| STA      | A-M                                              | l   | l    |     | 80       | 4    | 3    | 85       | 3     | 2    | П   |          |        |          |              | -   | Sı  | 6    | 2   | 91  | 6         | 2 9          | 5   | 4 2        | 90              | 5    | 3   | 99     | 5    | 3   |          |     |          |     |      |    | 1        |         | Ì    | ١   |                        |                  | STA      |

| STX      | x → M                                            | l   |      |     | BE       |      |      | 86       |       |      | l i |          | .      | ı        | ١            | -1  | -   | -    | -   | J   |           | 1            |     |            |                 | 1    |     | 1      |      |     |          |     |          |     | l    |    | 96       | 4       | 2    | 1   | • • • •                |                  | STX      |

| . STY    | Y → M                                            | l   | 1    | 1   | 80       | 4    | 3    | 84       | 3     | 2    |     |          | ŀ      |          |              | - [ | J   | -    | 1   | -   |           | 9            | 4   | 4 2        | 1               | 1    |     | 1      | t    |     |          |     |          |     | ļ    |    | 1        | -       | ŀ    | 1   |                        |                  | STY      |

| TAX      | A→X                                              | L   | L    | L   | _        | _    | L    | L        | L     | L    | Ш   |          | _      | AA.      | -            | 1   | ┙   | _    | 4   | ╝   | ╛         | 1            | 1   | $\perp$    | Ļ               | L    | Ļ   | L      | 1_   | L   | Ц        |     | Ш        |     | L    | L  | ╀        | L       | Ļ    | 4   | и · · ·                |                  | TAX      |

| TAY      | A → Y                                            |     | ľ    | ١   | Ι        |      | Ī    | ١        |       |      |     | 1        |        | A8       |              | 1   | -[  | - ]  | ı   | 1   |           | -            |     |            | 1               |      |     | 1      |      | 1   | П        |     |          |     |      | Ì  |          | 1       |      | 1   | и • • •                |                  | TAY      |

| TSX      | s → x                                            | 1   |      | 1   | 1        |      | 1    | 1        |       | 1    | l   |          |        | BA       | 2            | 1   | 1   |      | ١   |     |           | 1            |     |            | 1               |      |     |        |      | 1   | H        |     |          |     | ĺ    | l  | 1        | 1       | ļ    |     |                        | · · z            | TSX      |

| TXA      | X - A                                            | 1   | 1    |     |          |      | 1    | 1        |       |      |     |          |        | ВА       | 2            | 1   | - [ | - 1  | - [ |     | $ \cdot $ | 1            |     | 1          | ı               | 1    |     | 1      |      | 1   | П        |     |          | ļ.  |      | 1  | L        | İ       | 1    | 1   | N · · ·                | · · z            | TXA      |

| TXS      | X → S                                            | 1   | 1    |     | ľ        |      | 1    | 1        |       |      |     |          |        | 9A       | 2 2          | 1   | - 1 | - 1  | - [ |     |           | 1            |     | 1          |                 | 1    |     |        | 1    | 1   | Н        |     |          | ĺ   |      | 1  | ı        |         | 1    | 1   | N · · ·                |                  | TYA      |

| TYA      | Y-A                                              |     | L    | 1   | 1        | 1    | 1    | <u>L</u> | با    | L    | L_  |          |        | 98       | 2            | יי  | _   | _    | -   |     | Ļ         |              | ٠.  |            | _               | _    |     | _      | _    | _   | Ш        |     | Ц.       | ٠   | Ļ.   | L- | 1_       | 1_      |      |     | -                      |                  | •        |

|          | 111 ADD 1 10<br>121 ADD 1 TO                     |     |      |     |          |      |      |          |       |      |     | GE       |        |          |              |     |     |      | -   |     | ,         |              |     | DEX        |                 |      |     |        |      |     |          |     |          | •   |      | AD | D<br>BTA | 40      | r    |     |                        | MEMORY<br>MEMORY |          |

|          | ADD 2 TO                                         | ·N  | IF I | BRA | NC       | 100  | CU   | ÁS 1     | őő    | IFFE | RE  | NI P     | AGE    |          |              |     |     |      | -   |     | ,         |              |     | CUM<br>CUM |                 | TOF  | 4   |        |      | ٠   |          |     |          | Ĭ   |      | AN |          | 40      | •    |     |                        | NO. CYC          |          |

| 1        | (3) CARRY N                                      |     |      |     |          |      |      |          |       |      |     |          |        |          |              |     |     |      | -   |     | i         |              |     | MOF        |                 |      |     | ĊTI    | ve A | DO  | 1655     |     |          | v   |      | OR |          |         |      |     |                        | NO. BYTE         |          |

| 1        | (4) IF IN DEC                                    | MA. | OR.  | MUS | L.ZF     | E CH | u IS | KED      | FO    | R ZE | ЯÒ  | RES      | ULT    |          |              |     |     |      | - 1 |     |           | As           | WE  | MOF        | Y P             | ĘR S | TAC | K P    | OIN  | tea |          |     |          | ٧   |      | EX | CLU      | SIV     | E OI | R   |                        |                  |          |

T-49-17-06

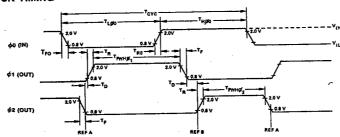

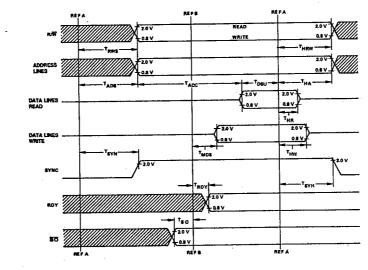

## R651X CLOCK TIMING

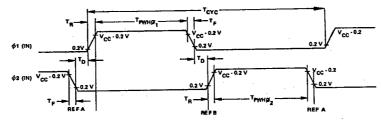

## R65XX READ WRITE TIMING

# R6500 Microprocessors (CPU)

## **AC CHARACTERISTICS**

|                                                                          |                                   |             | 5XX<br>AHz) |          | XXA<br>fHz) |      | XXB<br>VHz) |      |

|--------------------------------------------------------------------------|-----------------------------------|-------------|-------------|----------|-------------|------|-------------|------|

| Characteristic                                                           | Symbol                            | Min         | Max         | Min      | Max         | Min  | Max         | Unit |

| R650X CLOCK TIMING                                                       | •                                 | <del></del> |             | <u> </u> |             |      | -           |      |

| Clock Cycle Time                                                         | T <sub>CYC</sub>                  | 1.0         | 10          | 0.5      | 10          | 0.33 | 10          | μs   |

| ∮0 (IN) Low Pulse Width                                                  | T <sub>L60</sub>                  | 480         |             | 240      |             | 160  |             | ns   |

| ∮0 (IN) High Pulse Width                                                 | T <sub>H60</sub>                  | 460         | <u> </u>    | 240      | 1           | 160  | _           | ns   |

| ∮0 (IN) Rise and Fall Time¹. ²                                           | T <sub>R0</sub> , T <sub>F0</sub> | -           | 10          | -        | 10          | 1    | 10          | ns   |

| ∮1 (OUT) High Pulse Width                                                | T <sub>PWHø1</sub>                | 460         | _           | 235      | _           | 155  | _           | ns   |

| ∮2 (OUT) High Pulse Width                                                | T <sub>PWHØ2</sub>                | 460         | _           | 240      |             | 160  | _           | ns   |

| Delay Between \$1 (OUT) and \$2 (OUT)                                    | T <sub>D</sub>                    | 0           | _           | 0        | _           | 0    | _           | ns   |

| <b>∮</b> 1 (OUT), <b>∮</b> 2 (OUT) Rise and Fall<br>Time <sup>1, 2</sup> | T <sub>R</sub> , T <sub>F</sub>   | _           | 25          | _        | 25          | _    | 15          | ns   |

| R651X CLOCK TIMING                                                       |                                   |             |             |          |             |      |             |      |

| Clock Cycle Time                                                         | T <sub>CYC</sub>                  | 1.0         | 10          | 0.5      | . 10        | 0.33 | 10          | μs   |

| ∮1 (IN) High Pulse Width                                                 | T <sub>PWHØ1</sub>                | 430         | _           | 215      |             | 150  |             | ns   |

| 92 (IN) High Pulse Width                                                 | T <sub>PWH\$2</sub>               | 470         | 1           | 235      |             | 160  |             | ns   |

| Delay Between Ø1 and Ø2                                                  | T <sub>D</sub>                    | 0           | 1           | 0        |             | 0    | -           | ns   |

| 91 (IN), 92 (IN) Rise and Fall Time <sup>1, 3</sup>                      | T <sub>R</sub> , T <sub>F</sub>   | _           | 25          | _        | 20          |      | 15          | ns   |

| R65XX READ/WRITE TIMING                                                  |                                   |             |             |          |             |      |             |      |

| R/W Setup Time                                                           | T <sub>RWS</sub>                  | <u> </u>    | 225         | -        | 140         | ı    | 110         | ns   |

| R/W Hold Time                                                            | THRW                              | 30          | _           | 30       |             | 15   | _           | ns   |

| Address Setup Time                                                       | T <sub>ADS</sub>                  | -           | 225         |          | 140         | -    | 110         | ns   |

| Address Hold Time                                                        | T <sub>HA</sub>                   | 30          |             | 30       | _           | 15   |             | ns   |

| Read Access Time                                                         | T <sub>ACC</sub>                  |             | 650         |          | 310         |      | 170         | ns   |

| Read Data Setup Time                                                     | T <sub>DSU</sub>                  | 100         | _           | 50       | -           | 50   |             | ns   |

| Read Data Hold Time                                                      | T <sub>HR</sub>                   | 10          | _           | 10       |             | 10   |             | ns   |

| Write Data Setup Time                                                    | T <sub>MDS</sub>                  | _           | 175         |          | 100         | _    | 85          | ns   |

| Write Data Hold Time                                                     | T <sub>HW</sub>                   | 30          | _           | 30       | _           | 15   |             | ns   |

| SYNC Hold Time                                                           | T <sub>SYH</sub>                  | 30          | -           | 30       | _           | 15   | _           | ns   |

| RDY Setup Time                                                           | T <sub>RDY</sub>                  | 100         | _           | 50       |             | 35   |             | ns   |

| SO Setup Time                                                            | T <sub>SO</sub>                   | 100         | _           | 50       |             | 35   | _           | ns   |

|                                                                          |                                   |             |             |          | F           |      |             | I    |

## Notes:

SYNC Setup Time

1. Loads: All output except clocks = 1 TTL + 130 pF. Clock outputs = 1 TTL + 30 pF.

Tsyn

- 2. Measured between 0.8 and 2.0 points on waveform load. 3. Measured between 10% and 90% points on waveforms. 4. \*RDY must never switch states within  $R_{\rm RDY}$  to end of  $\rlap/$ 2.

225

140

1.10

T-49 -17-06

## R6500 Microprocessor (CPU)

## **ABSOLUTE MAXIMUM RATINGS\***

| Parameter                                               | Symbol           | Value        | Unit |

|---------------------------------------------------------|------------------|--------------|------|

| Supply Voltage                                          | V <sub>CC</sub>  | -0.3 to +7.0 | Vdc  |

| Input Voltage                                           | Vin              | -0.3 to +7.0 | Vdc  |

| Operating Temperature Range<br>Commercial<br>Industrial | TA               | -40 to +85   | °C   |

| Storage Temperature                                     | T <sub>STG</sub> | -55 to +150  | °C   |

## T-49-17-06

\*NOTE: Stresses above those listed may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the other sections of this document is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

## **OPERATING CONDITIONS**

| Parameter                                     | Symbol          | Value                          |

|-----------------------------------------------|-----------------|--------------------------------|

| Supply Voltage                                | V <sub>CC</sub> | 5V ±5%                         |

| Temperature Range<br>Commercial<br>Industrial | TA              | 0°C to +70°C<br>-40°C to +85°C |

## DC CHARACTERISTICS

(V<sub>CC</sub> = 5.0V  $\pm$ 5%, V<sub>SS</sub> = 0; T<sub>A</sub> = T<sub>L</sub> to T<sub>H</sub>, unless otherwise noted)

| Parameter                                                                     | Symbol                                                                        | Min.                                | Typ.5                   | Max.                                                         | Unit <sup>1</sup> | Test Conditions                                                              |

|-------------------------------------------------------------------------------|-------------------------------------------------------------------------------|-------------------------------------|-------------------------|--------------------------------------------------------------|-------------------|------------------------------------------------------------------------------|

| Input High Voltage                                                            | V <sub>IH</sub>                                                               |                                     |                         |                                                              | ٧                 |                                                                              |

| Logic<br>60 (IN)<br>61 (IN), 62 (IN)                                          |                                                                               | 2.0<br>2.4<br>V <sub>CC</sub> - 0.3 |                         | V <sub>CC</sub><br>V <sub>CC</sub><br>V <sub>CC</sub> + 0.25 |                   |                                                                              |

| Input Low Voltage<br>Logic<br>Ø0 (IN), Ø1 (IN), Ø2 (IN)                       | V <sub>IL</sub>                                                               | -0.3<br>-0.3                        | _                       | 0.8<br>0.4                                                   | V                 |                                                                              |

| Input Leakage Current<br>Logic (Excl. RDY, SO)<br>Ø1 (IN), Ø2 (IN)<br>Ø0 (IN) | I <sub>IN</sub>                                                               | -<br>-<br>-                         | _<br>_<br>_             | 2.5<br>100<br>10                                             | μА                | V <sub>IN</sub> = 0V to 5.25V<br>V <sub>C</sub> = 0V                         |

| Input Leakage Current for Three State Offf D0-D7                              | I <sub>TSI</sub>                                                              | _                                   | _                       | 10                                                           | μΑ                | $V_{IN} = 0.4V \text{ to } 2.4V$<br>$V_{CC} = 5.25V$                         |

| Output High Voltage<br>SYNC, D0-D7, A0-A15, R/W, Ø1 (OUT), Ø2 (OUT)           | V <sub>OH</sub>                                                               | +2,4                                | _                       |                                                              | V                 | $I_{LOAD} = -100 \mu\text{A}$ $V_{CC} = 4.75V$                               |

| Output Low Voltage<br>SYNC, D0-D7, A0-A15, R/W, \$1 (OUT), \$2 (OUT)          | V <sub>OL</sub>                                                               | _                                   | _                       | +0.4                                                         | V                 | $I_{LOAD} = 1.6 \text{ ma}$ $V_{CC} = 4.75V$                                 |

| Power Dissipation<br>1 and 2 MHz<br>3 MHz                                     | P <sub>D</sub>                                                                | _                                   | 450<br>500              | 700<br>800                                                   | mW                |                                                                              |

| Capacitance Logic D0-D7 A0-A15, R/W, SYNC Ø0 (IN) Ø1 (IN) Ø2 (IN)             | C<br>C <sub>IN</sub><br>C <sub>OUT</sub><br>CØ <sub>O(IN)</sub><br>CØ1<br>CØ2 |                                     | -<br>-<br>-<br>30<br>50 | 10<br>15<br>12<br>15<br>50<br>80                             | pF                | $V_{CC} = 5.0V$ $V_{IN} = 0V$ $f = 1 \text{ MHz}$ $T_A = 25^{\circ}\text{C}$ |

## Notes:

Notes:

1. All units are direct current (dc) except for capacitance.

2. Negative sign indicates outward current flow, positive indicates inward flow.

3. IRQ and NMI require 3K pull-up resistor.

4. Ø1 (IN) and Ø2 (IN) apply to R6512, 13, 14, and 15; Ø0 (IN) applies to R6502, 03, 04, 05, 06 and 07.

5. Typical values shown for V<sub>CC</sub> = 5.0V and T<sub>A</sub> = 25°C.