# UE6015 Time-Code Receiver IC

# 1 Short Description

The UE6015 is a BICMOS integrated straight through receiver circuit, which is suitable for the frequency range from 40kHz up to 120 kHz (ASK modulation). The receiver is equiped with a very high sensitivity and is prepared for single- and multi-band reception. Therefore this IC is designed for all kinds of standard and high valued radio controlled clock applications.

Once used with reference to its application circuit and connected with a corresponding antenna the UE6015 receives and demodulates time code signals transmitted by e.g. DCF77 (Germany), MSF (UK), WWVB (USA), JJY (JPN), HBG (CH) and BPC (China).

The IC includes an integrated antenna-switching circuit, controlled by 2 antenna-switch input-lines. This antenna switch allows to connect other capacitors in parallel to the initial antenna-capacitor. By this way the connected antenna can be tuned to at least 2 other frequencies too. By connection of max. 3 different crystal-filters it is possible to receive transmitting stations working on 3 different carrier frequencies. The UE6015 is the key for single-, dual-, or multi-band receivers.

Integrated functions as stand-by mode, hold mode and a selectable output polarity offer features for universal applications.

## 2 Features

- Single Chip AM Straight Through Receiver

- Low power consumption

- Very high sensitivity (typ. 0.3μV<sub>RMS</sub>)

- High selectivity by using crystal filters

- Power down mode available

- Only a few external components needed

- Implemented antenna-switches

- Single-, Dual- and Tri-Band receiver IC

- CMOS output stage with selectable polarity

- Output-signal for FSI-indication

- AGC hold mode

- Fast start-up

- Wide frequency range (40 ... 120 kHz)

- Low power battery applications (1.1 .. 3.6 V)

## 3 Operation Modes

## 3.1 Power Down Mode

Switching the IC into Power Down Mode the IC becomes current-less. During this operation mode:

- all internal functional blocks are powered OFF

- signal output DAT is set to LOW

- status of antenna-switches is undefined

## 3.2 ASK Reception mode

This standard reception mode is entered after PowerON Reset and is characterized by:

- AGC-hold function is available (pin HLD; LOW active)

- Data Output Polarity can be changed (pin DATP; LOW active); default polarity (DATP open) = LHL

- Integrated compensation capacitance can be switched OFF (pin CF; LOW active)

- Additional external capacitors can be added in parallel to the antenna capacitor in order to tune the antenna circuitry to a lower frequency (pins CA1, CA2; LOW active)

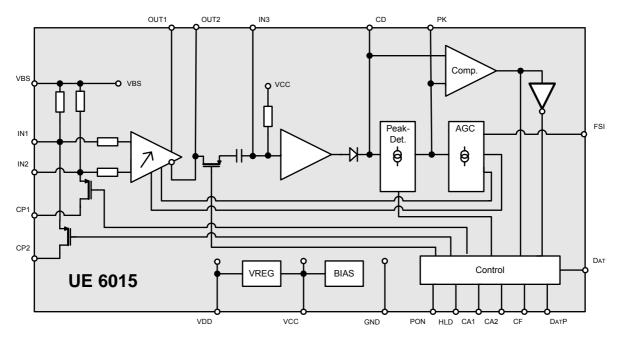

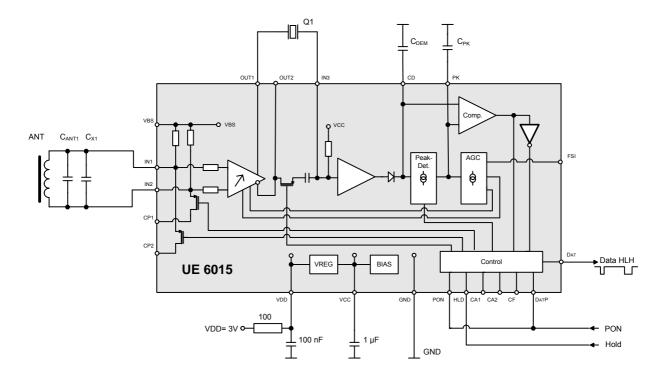

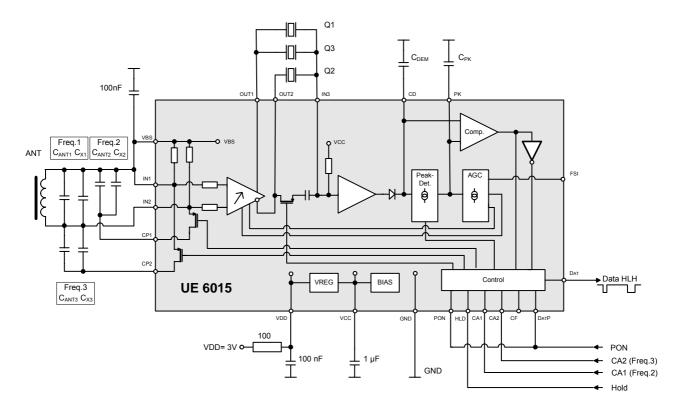

# 4 Block Diagram

Figure 1: Block diagram

# 5 Absolute Maximum Ratings

(for  $T_A = -25$  to  $85^{\circ}$ C)

| Pos. | Parameters                                                                   | Symbol           | min. | max.                 | Unit |

|------|------------------------------------------------------------------------------|------------------|------|----------------------|------|

| 1    | Supply voltage                                                               | V <sub>cc</sub>  | 0    | 3                    | V    |

| 2    | Supply voltage V <sub>DD</sub>                                               | V <sub>DD</sub>  | 0    | 4                    | V    |

| 3    | Voltage at any pin                                                           | V <sub>PIN</sub> | -0.3 | V <sub>CC</sub> +0.3 | V    |

|      | (except $V_{DD}$ , DAT, HLD, PON and digital inputs DATP, CF, CA1, CA2)      |                  |      |                      |      |

| 4    | Voltage at $V_{DD}$ , DAT, HLD, PON and at digital inputs DATP, CF, CA1, CA2 | $V_{PIN\ dig.}$  | -0.3 | V <sub>DD</sub> +0.3 | V    |

# 6 Operation Ratings

| Pos. | Parameters                     | conditions               | Symbol          | min. | max. | Unit |

|------|--------------------------------|--------------------------|-----------------|------|------|------|

| 1    | Supply voltage V <sub>CC</sub> | T <sub>A</sub> = 0 +85°C | V <sub>cc</sub> | 1.1  | 1.8  | V    |

| 2    | Supply voltage V <sub>DD</sub> |                          | V <sub>DD</sub> | 2    | 3.6  | V    |

| 3    | Ambient temperature            |                          | T <sub>A</sub>  | -25  | 85   | °C   |

| 4    | Frequency range                |                          | f <sub>IN</sub> | 40   | 120  | kHz  |

# 7 Electrical Characteristics

Unless otherwise specified:

$$\label{eq:VDD} \begin{split} V_{DD} = V_{CC} = 1.5V; \ V_{PON} = 0V; \ f_{IN} = 77.5 \text{kHz}, \ v_{IN} = 300 \mu V_{RMS}; \\ AM \ carrier \ voltage \ reduction \ from \ 100\% \ to \ 25\% \ for \ t_{MOD} = 200 \text{ms} \end{split}$$

## 7.1 DC-Characteristics

| Pos. | Parameters                 | conditions                                                         | Symb.                | min.                 | typ. | max.                 | Unit |

|------|----------------------------|--------------------------------------------------------------------|----------------------|----------------------|------|----------------------|------|

| 1    | Quiescent current          | V <sub>PON</sub> =V <sub>DD</sub> =3.0V                            | I <sub>DD0</sub>     |                      |      | 1                    | μA   |

| 2    | Quiescent current          | V <sub>PON</sub> =V <sub>DD</sub> =V <sub>CC</sub> =1.5V           | I <sub>DC0</sub>     |                      |      | 1                    | μA   |

| 3    | Supply current with VREG   | V <sub>DD</sub> =3.0V                                              | I <sub>DD</sub>      |                      |      | 130                  | μA   |

| 4    | Supply current w/o VREG    | $V_{DD}=V_{CC}=1.5V$                                               | I <sub>CC</sub>      |                      | 100  | 120                  | μA   |

| 5    | DAT output voltage HIGH    | I <sub>DAT</sub> = 30uA                                            | $V_{\text{DATH}}$    | V <sub>DD</sub> -0.3 |      |                      | V    |

| 6    | DAT output voltage LOW     | I <sub>DAT</sub> = - 30uA                                          | V <sub>DATL</sub>    |                      |      | 0.3                  | V    |

| 7    | DIG input voltage HIGH     | (all digital *)                                                    | V <sub>IH</sub>      | V <sub>DD</sub> *0.7 |      |                      | V    |

| 8    | DIG input voltage LOW      | (all digital *)                                                    | V <sub>IL</sub>      |                      |      | V <sub>DD</sub> *0.3 | V    |

| 9    | DIG input current HIGH     | V <sub>IX</sub> =H (all digital *)                                 | I <sub>IHx</sub>     |                      |      | 1                    | μA   |

| 10   | DIG input current LOW      | V <sub>IX</sub> =L (all digital *)                                 | I <sub>ILx</sub>     | -10                  |      |                      | μA   |

| 11   | PK settling time default   | С <sub>РК</sub> = 1µF                                              | t <sub>PK</sub>      |                      |      | 3                    | S    |

| 12   | AGC response time +        | $V_{PON} = 0V; \Delta v_{IN} = +20dB$                              | $t_{AGC+\Delta}$     |                      | 0.3  |                      | S    |

| 13   | AGC response time -        | $V_{PON} = 0V; \Delta v_{IN} = -20dB$                              | t <sub>AGC-∆</sub>   |                      | 7    |                      | S    |

| 14   | FSI output current min.    | v <sub>IN</sub> = 0                                                | I <sub>FSI min</sub> |                      | 0.3  | 1                    | μA   |

| 15   | FSI output current max.    | v <sub>IN</sub> = 30mV <sub>RMS</sub>                              | I <sub>FSI max</sub> |                      | 10   |                      | μA   |

| 16   | FSI output voltage         | v <sub>IN</sub> = 30mV <sub>RMS</sub> ; I <sub>FSI max</sub> =10µA | U <sub>FSI max</sub> |                      |      | 1                    | V    |

| 17   | CPx PMOS-RDS <sub>ON</sub> | CAx=L                                                              | R <sub>CPx</sub>     |                      | 6    |                      | Ω    |

| 18   | IN1 / IN2 input impedance  |                                                                    | Z <sub>Inx1</sub>    |                      | 500  |                      | kΩ   |

$^{*)}$  PON, HLD and digital inputs DATP, CF, CA1, CA2;  $\,$  H=V\_{DD}, L=0V

## 7.2 AC-Characteristics

| Pos. | Parameters                           | conditions                                     | Symb.               | Min | Тур | Max | Unit                 |

|------|--------------------------------------|------------------------------------------------|---------------------|-----|-----|-----|----------------------|

| 1    | Minimum input voltage                | differential input                             | V <sub>IN min</sub> |     | 0.3 | 0.6 | $\mu V_{\text{RMS}}$ |

| 2    | Maximum input voltage                | differential input                             | V <sub>IN max</sub> | 30  |     |     | $mV_{RMS}$           |

| 3    | Output pulse width                   | DCF, t <sub>MOD</sub> =200ms                   | t <sub>WDAT</sub>   | 160 | 185 | 220 | ms                   |

| 4    | Static parallel input<br>capacitance | between IN1 and IN2 w/o using antenna switches | CPS <sub>IN</sub>   |     | 18  |     | pF                   |

| 5    | Additional input capacitance<br>CP1  | using CP1                                      | CPP1                |     | 6.5 |     | pF                   |

| 6    | Additional input capacitance<br>CP2  | using CP2                                      | CPP2                |     | 8   |     | pF                   |

| SPEC No. | Revision | State      | Version | Page         |

|----------|----------|------------|---------|--------------|

| UE6015   | A 4.1    | 31.07.2006 | English | Page 3 of 14 |

#### 8 Internal connection of PAD's

The IC is ESD protected conform to the Human-Body-Model ( $V_{ESD}$  = ±1000V on each pin refered to GND).

#### 9 Functional description of PAD's

#### IN1 / IN2 Antenna inputs

Both antenna inputs, IN1 and IN2, are entitled to the same rights. Each of the antenna inputs is connected by an integrated resistor to the internal Bias-voltage. Generally it is possible to realize a symmetrical or an unsymmetrical operation of the connected ferrit-antenna. The coil of the ferrit-antenna has to be connected between IN1 and IN2.

- symmetrical operation mode:

Recommended operation mode for applications influenced by bigger disturbances and for multi-band receivers. The RF-signal is supplied symmetrically into both antenna inputs. Pin VBS is not used.

<u>unsymmetrical operation mode:</u>

The RF-signal is supplied into only one of the antenna inputs. The second antenna input is connected to Pin VBS. A capacitor has to be connected between Pin VBS and GND.

#### CP1 / CP2 PMOS antenna switch inputs

Inputs of two PMOS-switches which are used to connect additional capacitors in parallel to the initial antenna capacitor in order to reduce the resonant frequency of the antenna circuit. The additonal capacitors should be connected between IN1 and CP1 respectively between IN2 and CP2. By this way the antenna can be tuned to other frequencies too.

The implemented antenna switches of UE6015 are characterized by parasitic capacitances as specified in chapter 7.2.

#### OUT1 Crystal RF output 1

At the output OUT1 you find the amplified RF-signal. OUT1 is connected to the crystal 1 filter.

#### OUT2 Crystal RF output 2

At the output OUT2 you find the amplified RF-signal. OUT2 is connected to the crystal 2 filter.

#### IN 3 Crystal input 1

High resistance input of an amplifier stage. An external crystal has to be connected to IN3 to supply the filtered signal into this amplifier.

#### CF Filter switch input

CMOS compatible input; LOW active; by default set to HIGH via internal pull-up resistor. Using an odd no. of filter-crystals this pin has to be kept open. Once the receiver is used with 2 filter-crystals then this pin should be switched to LOW during any reception attempt.

#### CD Demodulator output

An external capacitor (typ. 47nF) has to be connected between pin CD and GND. It is used to demodulate the filtered and amplified RF-signal.

#### PK Peak Detector output

An external capacitor ( $C_{PK} \ge 2.2\mu$ F) has to be connected between pin PK and GND. This ensures the function of the peak detector. The value of  $C_{PK}$  influences the AGC regulation time.

#### FSI Field strength indicator

Output FSI supplies a current which is proportional (appr. logarithmic) to the received field-strength. The typical range of output-current is  $0.1\mu$ A ...  $10\mu$ A which corresponds with a range of input-voltage of  $0.3\mu$ V ... 30mV. The simpliest way to use this output-information is the use of a resistor ( $47k\Omega$  ...  $100k\Omega$ ) between FSI-output and GND. The output stage is a PMOS-current source and can be kept open if it isn't used.

The output-current of this FSI-pin isn't considered in the current consumption specified for the IC.

| SPEC No. | Revision | State      | Version | Page         |

|----------|----------|------------|---------|--------------|

| UE6015   | A 4.1    | 31.07.2006 | English | Page 4 of 14 |

# DATP Data-Output-Polarity selection input

CMOS compatible input; LOW active; by default set to HIGH via internal pull-up resistor.

This pin allows the control of the polarity of output signal obtained on pin DAT. By default (DATP not connected) this pin is HIGH and the resulting polarity of output signal is LHL. In order to change the polarity of output signal to HLH pin DATP has to be connected to LOW during any reception attempt. If the receiver is switched OFF (PON=HIGH= $V_{DD}$ ) then set DATP=HIGH too.

## HLD AGC hold input

CMOS compatible, digital input; LOW active; by default set to HIGH via internal pull-up resistor.

AGC hold mode: HLD = HIGH sets normal function,  $HLD = LOW (V_{HLD} = GND)$  holds for a short time the AGC voltage. This can be used to prevent the AGC from peak voltages, created by e.g. a stepper motor. Once HLD is used then it is recommended to keep HLD activated (HLD=LOW) as long as the interference can

## PON Power ON input

CMOS compatible, digital input; LOW active; by default set to HIGH via internal pull-up resistor. By this pin the operation mode of IC is controlled. If PON is LOW (connected to GND), the receiver will be activated. If PON is HIGH, the receiver will switch to power-down mode.

## DAT Data output

CMOS compatible, digital output w/o any internal pull-resistors.

be detected on the cristal filter. Typical values are 100...200ms.

At the data output pin DAT you find the demodulated time code signal. By default (DATP open) output signal pulses will be HIGH-active (LHL). The polarity can be inverted to HLH once the DATP-pin is used accordingly.

## CA1 / CA2 Antenna-Switch control inputs

CMOS compatible, digital inputs; LOW active; by default set to HIGH via internal pull-up resistor.

Inputs used to control the status of those two integrated PMOS-antenna-switches.

Once CA1/CA2 are not connected or set to HIGH then the antenna-switches are open (high impedance). If one or both of these pins are set to LOW during reception mode, then the corresponding antenna switch is closed and the corresponding capacitor connected to CP1 / CP2 is added to the antenna capacitor.

If the receiver is switched OFF (PON=HIGH= $V_{DD}$ ) then also set CA1 = CA2 = HIGH.

## VDD Supply voltage, input of voltage regulator

Once we have a 3V-application then the positive power supply voltage for the IC has to be connected to VDD only. It is recommended to provide corresponding RC-elements between VDD and GND in order to get a smooth power supply voltage.

Once the power supply voltage is 1.5V only then pins VDD and VCC should be connected together.

## VCC Supply voltage, output of voltage regulator

Common input (together with VDD) of positive power supply voltage for 1.5V applications. An external capacitor ( $\geq 1\mu$ F) has to be connected between pin VCC and GND.

If there is used a 3V power supply voltage then pin VCC has to be connected to the external capacitor only!

## GND Supply Ground

GND is the reference potential for all IC-stages and for the internal ESD protection circuit. GND is also connected to the IC-substrate.

## VBS Input Bias voltage

Used only during unsymmetrical operation mode of antenna. A capacitor has to be connected between pin VBS and GND. In all other applications this pin shouldn't be connected.

#### **10 Pad Layout and PAD Coordinates**

The UE6015 is available as DIE for "chip-on-board" mounting.

| DIE size:  | 1470 µm x 1720 µm |

|------------|-------------------|

| Thickness: | 330 µm            |

| PAD size:          | 100 µm x 90 µm |

|--------------------|----------------|

| min. pad-distance: | 50 µm          |

| min. pad-pitch:    | 140 µm         |

Once the chip-substrate has to be electrically connected then GND has to be used as reference voltage for the chip back-plane.

Note:

- Pad coordinates are refered to the center point of each pad.

- The reference point (origin) for the pad coordinates is the lower left chip edge (0;0).

| Pad # (dice) | Symbol | Function                                    | x-axis (µm) | y-axis (µm) |

|--------------|--------|---------------------------------------------|-------------|-------------|

| 1            | CP2    | PMOS antenna switch input 2                 | 169.1       | 175.0       |

| 2            | CP1    | PMOS antenna switch input 1                 | 169.1       | 315.0       |

| 3            | IN1    | Antenna input 1                             | 169.1       | 455.0       |

| 4            | IN2    | Antenna input 2                             | 169.1       | 595.0       |

| 5            | VCC    | Supply voltage, output of voltage regulator | 169.1       | 735.0       |

| 6            | VDD    | Supply voltage, input of voltage regulator  | 169.1       | 875.0       |

| 7            | OUT1   | Crystal RF output 1                         | 169.1       | 1015.0      |

| 8            | OUT2   | Crystal RF output 2                         | 169.1       | 1155.0      |

| 9            | GND    | Supply Ground                               | 169.1       | 1295.0      |

| 10           | IN3    | Crystal input 1                             | 169.1       | 1435.0      |

| 11           | CF     | Filter Switch Input                         | 169.1       | 1575.0      |

| 12           | DATP   | Data-Output-Polarity selection input        | 1330.9      | 1575.0      |

| 13           | FSI    | Field strength indicator output             | 1330.9      | 1435.0      |

| 14           | CD     | Demodulator output                          | 1330.9      | 1295.0      |

| 15           | HLD    | AGC hold input                              | 1330.9      | 1155.0      |

| 16           | PK     | Peak detector output                        | 1330.9      | 1015.0      |

| 17           | PON    | Power ON input                              | 1330.9      | 875.0       |

| 18           | CA1    | Antenna Switch control input 1              | 1330.9      | 735.0       |

| 19           | CA2    | Antenna Switch control input 2              | 1330.9      | 595.0       |

| 20           | DAT    | Data output                                 | 1330.9      | 455.0       |

| 21           | VBS    | Input bias voltage                          | 1330.9      | 315.0       |

| 22           | TP     | TestPad – do not connect!                   | 1330.9      | 175.0       |

#### **11 Ordering Information**

| Extended Type Number | Package | Remarks      |  |  |

|----------------------|---------|--------------|--|--|

| UE6015 DIT           | No      | DIE in trace |  |  |

| SPEC No. | Revision | State      | Version | Page         |

|----------|----------|------------|---------|--------------|

| UE6015   | A 4.1    | 31.07.2006 | English | Page 6 of 14 |

reference point (origin)

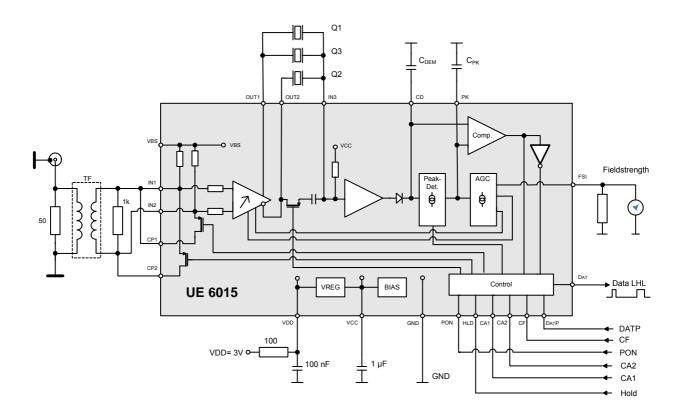

# 12 Test Circuitry

# **13** Application hints

13.1 General application circuit and recommended values (VDD=3V; symmetr. oper. of antenna)

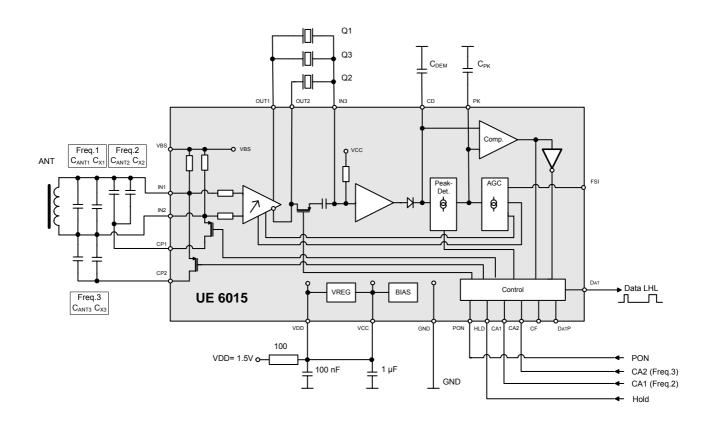

Recommended component values for a typical 3-band application (77.5kHz/60kHz/40kHz; symmetrical antenna operation; VDD=3V) based on the electrical scheme shown above:

| Selected<br>Band<br>(Carrier freq.) | Q1<br>[kHz] | Q2<br>[kHz] | Q3<br>[kHz] | ANT<br>[kHz] | C <sub>DEM</sub><br>[nF] | С <sub>РК</sub><br>[µF] | $C_{ANT1}$<br>+ $C_{X1}$<br>[nF] | $C_{ANT2}$<br>+ $C_{X2}$<br>[nF] | C <sub>ANT3</sub><br>+ C <sub>X3</sub><br>[nF] | CA1            | CA2            | CF             |

|-------------------------------------|-------------|-------------|-------------|--------------|--------------------------|-------------------------|----------------------------------|----------------------------------|------------------------------------------------|----------------|----------------|----------------|

| basic assy.                         | 77.5        | 60          | 40          | 77.5         | 47                       | 2.2                     | 1.8                              | 1.25                             | 3.93                                           |                |                | HIGH<br>(open) |

| 77.5kHz                             |             |             |             |              |                          |                         | active                           |                                  |                                                | HIGH<br>(open) | HIGH<br>(open) |                |

| 60kHz                               |             |             |             |              |                          |                         | active                           | active                           |                                                | LOW            | HIGH<br>(open) |                |

| 40kHz                               |             |             |             |              |                          |                         | active                           | active                           | active                                         | LOW            | LOW            |                |

Recommended antenna: resonant frequency = 77.5kHz ; L/C-ratio: L=2.29mH / C=1.8nF

#### Remarks:

a) Pin CA1 controls the antenna switch input CP1 and therefore the use of the additional set of antenna capacitors C<sub>ANT2</sub> + C<sub>X2</sub> connected between IN1 and CP1.

b) Pin CA2 controls the antenna switch input CP2 and therefore the use of the additional set of antenna capacitors C<sub>ANT3</sub> + C<sub>X3</sub> connected between IN2 and CP2.

c) The values mentioned above for antenna capacitors are theoretical values calculated for the corresponding target frequency with reference to the specified "ideal" antenna. Capacitor- and antenna-tolerances as well as the influence of the product construction and product casing were not taken into account and should be respected accordingly during the antenna tuning procedure.

| SPEC No. | Revision | State      | Version | Page         |

|----------|----------|------------|---------|--------------|

| UE6015   | A 4.1    | 31.07.2006 | English | Page 8 of 14 |

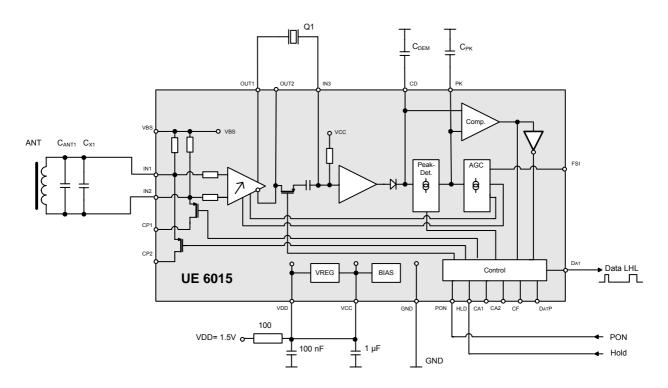

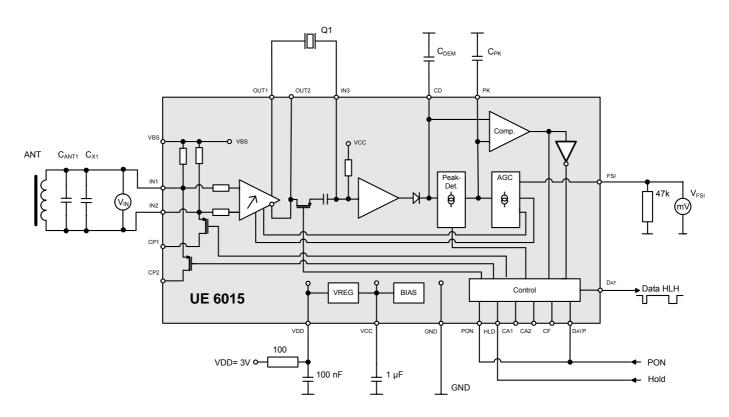

# 13.2 Application circuit (1-band; VDD=3V; symmetr. operation. of ANT; HLH)

13.3 Application circuit (1-band; VDD=1.5V; symmetr. operation. of ANT; LHL)

| SPEC No. | Revision | State      | Version | Page         |

|----------|----------|------------|---------|--------------|

| UE6015   | A 4.1    | 31.07.2006 | English | Page 9 of 14 |

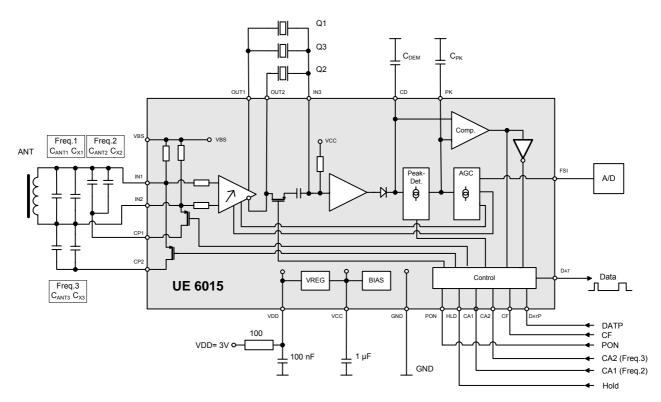

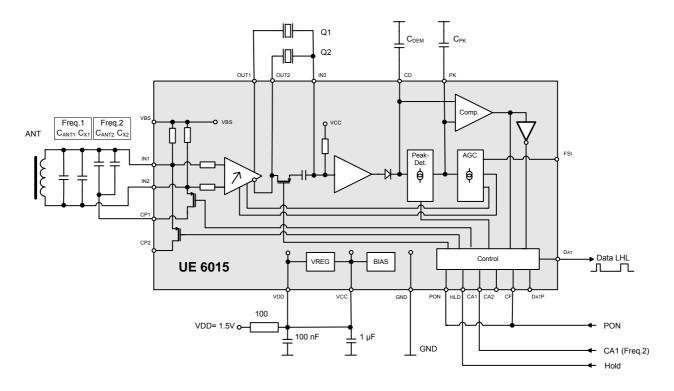

# 13.4 Application circuit (2-band; VDD=1.5V; symmetr. operation. of ANT; LHL)

13.5 Application circuit (3-band; VDD=1.5V; symmetr. operation. of ANT; LHL)

| SPEC No. | Revision | State      | Version | Page          |

|----------|----------|------------|---------|---------------|

| UE6015   | A 4.1    | 31.07.2006 | English | Page 10 of 14 |

## 13.6 Application circuit (3-band; VDD=3V; unsymmetr. operation. of ANT; HLH)

13.7 General aspects concerning the use and connection of control pins CF, CA1, CA2, DATP

All these pins have internal pull-up resistors. By this way they are pre-defined to logic HIGH if no external circuit will force them to LOW = GND.

- a) If HIGH-level is that logic level you need for your UE6015-configuration then simply keep the corresponding pin open (not connected).

- b) Pin PON is used to switch ON the receiver circuit UE6015 (PON = LOW = GND). Once the UE6015 configuration for your specific application needs other control-pins connected to LOW too (like CF, CA1, CA2, DATP) then we recommend to set them to LOW in combination with control-line PON. By this way you activate the corresponding control-pins only for the duration of any active reception attempt which minimizes the total power-consumption of UE6015.

- 13.8 General aspects concerning the use of antenna switches CP1, CP2

- a) Antenna switches CP1 and CP2 are compatible to each other. For the realization of 2-band applications there can be used or switch CP1 or switch CP2. Please refer to the alternative solutions a) and b) described in table 13.8 proposed for a typical 2-band configuration.

- b) Improvement of antenna effectivity for multiband applications

The antenna for multiband-applications is initially specified and optimized (no. of windings) for the highest frequency to be received. Switching the same antenna to any other, lower frequency by connecting additional antenna-capacitors in parallel, the L/C ratio of antenna automatically becomes suboptimal for the corresponding frequency. This effect cannot be avoided.

In the same time the antenna quality factor has to suffer from the influence of the internal, parasitic channelimpedance of each antenna switch too. The influence of this channel resistance can be reduced if both antennaswitches are used simultaneousely.

| SPEC No. | Revision | State      |

|----------|----------|------------|

| UE6015   | A 4.1    | 31.07.2006 |

Therefore, for a 3-band application it is recommended to use both antenna switches (and not only one) in order to tune the antenna to the lowest requested frequency (table 13.8).

In some dual-band watch-applications it can be also useful to split the value of the additionally needed antennacapacitor into two, approx. equal capacitors, to connect each one of them between CP1 and IN1 respectively between CP2 and IN2 and to operate both antenna switches simultaneously to switch the antenna from frequency 1 to the lower frequency 2.

This procedure helps to improve the antenna-effectivity by reducing the influence of the channel-resistance.

| <ul> <li>c) possible realization of</li> </ul> |                   | for a construction of |                        |

|------------------------------------------------|-------------------|-----------------------|------------------------|

| c) nossinie realization of                     | antenna switching | for some typical      | LIEBUIS-CONTINUESTIONS |

|                                                |                   |                       |                        |

| carrier freq. to<br>be received<br>[kHz] | CA1        | CA2        | CF         | CP1    | CP2    | target freq. of<br>antenna [kHz];<br>(+/- offset freq.) | comments                                                     |

|------------------------------------------|------------|------------|------------|--------|--------|---------------------------------------------------------|--------------------------------------------------------------|

| 1-band                                   |            |            |            |        |        |                                                         |                                                              |

| 77.5                                     | n.c.       | n.c.       | n.c.= HIGH | n.c.   | n.c.   | 77.5                                                    |                                                              |

| 2-band a)                                |            |            |            |        |        |                                                         |                                                              |

| 60                                       | HIGH       | n.c.= HIGH | LOW        | open   | n.c.   | 60                                                      | using antenna-                                               |

| 40                                       | LOW        | п.с.– пібп | LOW        | closed | n.c.   |                                                         | switch CA1/CP1                                               |

| 2-band b)                                |            |            |            |        |        |                                                         |                                                              |

| 60                                       | n.c.= HIGH | HIGH       | LOW        | n.c.   | open   | 60                                                      | using antenna-                                               |

| 40                                       |            | LOW        | LOW        | n.c.   | closed | 1                                                       | switch CA2/CP2                                               |

| 2-band c)                                |            |            |            |        |        |                                                         |                                                              |

| 60                                       | HIGH       | HIGH       |            | open   | open   |                                                         | splitting the addit.                                         |

| 40                                       | LOW        | LOW        | LOW        | closed | closed | 60                                                      | antenna-cap. and<br>using both antenna-<br>switches together |

| 3-band                                   |            |            |            |        |        |                                                         |                                                              |

| 77.5                                     | HIGH       | HIGH       |            | open   | open   |                                                         |                                                              |

| 60                                       | LOW        | HIGH       | n.c.= HIGH | closed | open   | 77.5                                                    |                                                              |

| 40                                       | LOW        | LOW        | n.c mon    | closed | closed |                                                         | using both antenna-<br>switches together                     |

<u>table 13.8:</u> possible realization of antenna switching for some typical UE6015-configurations (n.c. = not connected)

## 13.9 Special characteristic of Data output DAT

The internal configuration and driving capability of pin DAT allows the direct connection of test- and measurement equipment without big influence onto the reception characteristics. This is an enormous advantage with focus to the arrangement of functional tests of the receiver IC during any production line.

#### 13.10 Advantage of symmetrical antenna connection

The symmetrical connection of antenna is useful especially in applications of digital RC-clocks and –watches. It reduces the interference level seen on the input of UE6015 once it is applied in a noisy environment. There can be reduced, for example, the effect of interferences created by LCDs, matrix-keyboards, etc.

#### 13.11 Typical use of FSI-output

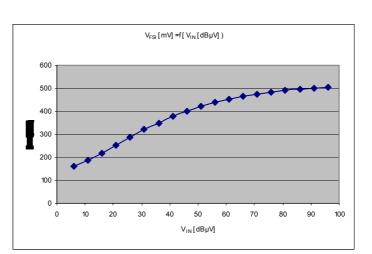

In order to get an information about the existing field-strength of received signal and in order to make a further evaluation of the receiption environment, the FSI-output current can be used. An easy and practical way is the connection of a resistor (47k $\Omega$  .. 100k $\Omega$ ) between FSI-output and GND (figure 13.11.a). Typical values of the characteristic between input voltage V<sub>IN</sub> of receiver circuit (function of the existing field strength and antenna factor of used antenna) and V<sub>FSI</sub> are given in table 13.11 and in figure 13.11.b.

Remarks:

- a) type of antenna used for this example: 8mm x 60mm / 77.5kHz

- b)  $R_{FSI} = 47$ kohm

- c) Measurements were made in a shielded room.

| SPEC No. | Revision | State      | Version | Page          |

|----------|----------|------------|---------|---------------|

| UE6015   | A 4.1    | 31.07.2006 | English | Page 12 of 14 |

Figure 13.11.a:

application circuit used

| field strenght of received time code signal | input voltage<br>measured at the<br>antenna input of<br>UE6015 | FSI-output voltage<br>@47kohm |

|---------------------------------------------|----------------------------------------------------------------|-------------------------------|

| E [dBµV/m]                                  | Vin [dBµV]                                                     | V <sub>FSI</sub> [mV]         |

| 30                                          | 6                                                              | 162                           |

| 35                                          | 11                                                             | 189                           |

| 40                                          | 16                                                             | 219                           |

| 45                                          | 21                                                             | 253                           |

| 50                                          | 26                                                             | 286                           |

| 55                                          | 31                                                             | 320                           |

| 60                                          | 36                                                             | 349                           |

| 65                                          | 41                                                             | 377                           |

| 70                                          | 46                                                             | 399                           |

| 75                                          | 51                                                             | 420                           |

| 80                                          | 56                                                             | 438                           |

| 85                                          | 61                                                             | 453                           |

| 90                                          | 66                                                             | 465                           |

| 95                                          | 71                                                             | 475                           |

| 100                                         | 76                                                             | 484                           |

| 105                                         | 81                                                             | 492                           |

| 110                                         | 86                                                             | 497                           |

| 115                                         | 91                                                             | 501                           |

| 120                                         | 96                                                             | 503                           |

Table 13.11:values measured

| SPEC No. | Revision | State      |  |

|----------|----------|------------|--|

| UE6015   | A 4.1    | 31.07.2006 |  |

# 14 Disclaimer of Warranty

Information furnished is believed to be accurate and reliable. However HKW-Elektronik GmbH assumes no responsibility, neither for the consequences of use of such information nor for any infringement of patents or other rights of third parties, which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of HKW. Specifications mentioned in this publication are subject to change without notice. This publication supersedes and replaces all information previously supplied. HKW products are not authorized for use as critical components in life support devices without express written approval of HKW.

#### Note

It is not given warranty that the declared circuits, devices, facilities, components, assembly groups or treatments included herein are free from legal claims of third parties.

The declared data are serving only to description of product. They are not guaranteed properties as defined by law. The examples are given without obligation and cannot given rise to any liability.

Reprinting this data sheet - or parts of it - is only allowed with a license of the publisher.

HKW-Elektronik GmbH reserve the right to make changes on this specification without notice at any time.

## **HKW-Elektronik GmbH**

Distributed by:

Industriestraße 12 D-99846 Seebach Germany

Tel.:

+49 (0)36929 82330

Fax:

+49 (0)36929 82339

Internet:

<u>http://www.hkw-elektronik.de</u>

email:

kontakt@hkw-elektronik.de