# Universal Serial Bus 3.0 Specification

**Hewlett-Packard Company**

Intel Corporation

Microsoft Corporation

**NEC Corporation**

ST-NXP Wireless

**Texas Instruments**

# **Revision History**

| Revision | Comments         | Issue Date        |

|----------|------------------|-------------------|

| 1.0      | Initial release. | November 12, 2008 |

#### INTELLECTUAL PROPERTY DISCLAIMER

THIS SPECIFICATION IS PROVIDED TO YOU "AS IS" WITH NO WARRANTIES WHATSOEVER, INCLUDING ANY WARRANTY OF MERCHANTABILITY, NON-INFRINGEMENT, OR FITNESS FOR ANY PARTICULAR PURPOSE. THE AUTHORS OF THIS SPECIFICATION DISCLAIM ALL LIABILITY, INCLUDING LIABILITY FOR INFRINGEMENT OF ANY PROPRIETARY RIGHTS, RELATING TO USE OR IMPLEMENTATION OF INFORMATION IN THIS SPECIFICATION. THE PROVISION OF THIS SPECIFICATION TO YOU DOES NOT PROVIDE YOU WITH ANY LICENSE, EXPRESS OR IMPLIED, BY ESTOPPEL OR OTHERWISE, TO ANY INTELLECTUAL PROPERTY RIGHTS.

Please send comments to techsup@usb.org

For industry information, refer to the USB Implementers Forum web page at <a href="http://www.usb.org">http://www.usb.org</a>

All product names are trademarks, registered trademarks, or servicemarks of their respective owners.

Copyright © 2007-2008, Hewlett-Packard Company, Intel Corporation, Microsoft Corporation, NEC Corporation, ST-NXP Wireless, and Texas Instruments.

All rights reserved.

# Acknowledgement of USB 3.0 Technical Contribution

#### **Dedication**

Dedicated to the memory of Brad Hosler, the impact of whose accomplishments made the Universal Serial Bus one of the most successful technology innovations of the Personal Computer era.

The authors of this specification would like to recognize the following people who participated in the USB 3.0 Bus Specification technical workgroups. We would also like to acknowledge the many others throughout the industry who provided feedback and contributed to the development of this specification.

#### **Promoter Company Employees**

Alan Berkema Hewlett-Packard Company

Walter Fry Hewlett-Packard Company

Anthony Hudson Hewlett-Packard Company

David Roderick Hewlett-Packard Company

Kok Hong Chan Intel Corporation Huimin Chen Intel Corporation Bob Dunstan Intel Corporation Dan Froelich Intel Corporation Howard Heck Intel Corporation **Brad Hosler** Intel Corporation John Howard Intel Corporation Rahman Ismail Intel Corporation John Keys Intel Corporation Yun Ling Intel Corporation Andy Martwick Intel Corporation Steve McGowan Intel Corporation Ramin Neshati Intel Corporation **Duane Quiet** Intel Corporation Jeff Ravencraft Intel Corporation **Brad Saunders** Intel Corporation Joe Schaefer Intel Corporation Sarah Sharp Intel Corporation Micah Sheller Intel Corporation Gary Solomon Intel Corporation Karthi Vadivelu Intel Corporation Clint Walker Intel Corporation Jim Walsh Intel Corporation Randy Aull Microsoft Corporation Fred Bhesania Microsoft Corporation Martin Borve Microsoft Corporation Jim Bovee Microsoft Corporation Stephen Cooper Microsoft Corporation Lars Giusti Microsoft Corporation Robbie Harris Microsoft Corporation

#### Universal Serial Bus 3.0 Specification, Revision 1.0

Allen Marshall Microsoft Corporation Kiran Muthabatulla Microsoft Corporation Tomas Perez-Rodriguez Microsoft Corporation Mukund Sankaranarayan Microsoft Corporation Nathan Sherman Microsoft Corporation Glen Slick Microsoft Corporation David Wooten Microsoft Corporation Rob Young Microsoft Corporation Nobuo Furuya **NEC Corporation** Hiroshi Kariya **NEC Corporation** Masami Katagiri **NEC Corporation** Yuichi Mizoguchi **NEC Corporation NEC Corporation** Kats Nakazawa Nobuyuki Mizukoshi **NEC Corporation** Yutaka Noguchi **NEC Corporation** Hajime Nozaki **NEC Corporation** Kenji Oguma **NEC Corporation** Satoshi Ohtani **NEC Corporation** Takanori Saeki **NEC Corporation** Eiji Sakai **NEC Corporation** Hiro Sakamoto **NEC Corporation** Hajime Sakuma **NEC Corporation** Makoto Sato **NEC Corporation** Hock Seow **NEC Corporation** "Peter" Chu Tin Teng **NEC Corporation** Yoshiyuki Tomoda **NEC** Corporation Satomi Yamauchi **NEC Corporation** Yoshiyuki Yamada **NEC Corporation** Susumu Yasuda **NEC Corporation** Alan Chang ST-NXP Wireless Wing Yan Chung ST-NXP Wireless Socol Constantin ST-NXP Wireless

Knud Holtvoeth NXP Semiconductors, B.V.

Linus Kerk ST-NXP Wireless

Martin Klein NXP Semiconductors, B.V.

Geert Knapen NXP Semiconductors, B.V.

Chee Ee Lee ST-NXP Wireless

Christian Paguet NXP Semiconductors, B.V.

Veerappan RajaramST-NXP WirelessShaun ReemeyerST-NXP WirelessDave SrokaST-NXP WirelessChee-Yen TEEST-NXP WirelessJerome TjiaST-NXP Wireless

Bart Vertenten NXP Semiconductors, B.V.

Hock Meng Yeo ST-NXP Wireless

Olivier Alavoine Texas Instruments.

David Arciniega Texas Instruments

Richard Baker Texas Instruments

Sujoy Chakravarty Texas Instruments

T. Y. Chan Texas Instruments

Romit Dasgupta Texas Instruments. Alex Davidson **Texas Instruments** Eric Desmarchelier **Texas Instruments** Christophe Gautier **Texas Instruments** Dan Harmon **Texas Instruments** Will Harris **Texas Instruments** Richard Hubbard **Texas Instruments** Ivo Huber **Texas Instruments** Scott Kim Texas Instruments **Texas Instruments Grant Ley** Karl Muth **Texas Instruments** Lee Myers Texas Instruments Julie Nirchi Texas Instruments Wes Ray **Texas Instruments** Matthew Rowley **Texas Instruments** Bill Sherry **Texas Instruments** Mitsuru Shimada **Texas Instruments** James Skidmore **Texas Instruments** Yoram Solomon Texas Instruments. Sue Vining Texas Instruments **Texas Instruments** Jin-sheng Wang Roy Wojciechowski **Texas Instruments**

#### **Contributor Company Employees**

Glen Chandler Acon

John Chen Acon

Roger Hou Acon

Charles Wang Acon

Norman Wu Acon

Steven Yang Acon

George Yee Acon

George Olear Contech Research

Sophia Liu Electronics Testing Center, Taiwan (ETC)

William Northey FCI Tom Sultzer FCI Garry Biddle Foxconn Kuan-Yu Chen Foxconn Jason Chou Foxconn Gustavo Duenas Foxconn Bob Hall Foxconn Jiayong He Foxconn Jim Koser Foxconn Joe Ortega Foxconn Ash Raheja Foxconn James Sabo Foxconn Pei Tsao Foxconn Kevin Walker Foxconn Tsuneki Watanabe Foxconn Chong Yi Foxconn Taro Hishinuma Hirose Electric Kaz Ichikawa Hirose Electric Ryozo Koyama Hirose Electric Karl Kwiat Hirose Electric Tadashi Sakaizawa Hirose Electric Shinya Tono Hirose Electric

#### Universal Serial Bus 3.0 Specification, Revision 1.0

Eiji Wakatsuki Hirose Electric

Takashi Ehara Japan Aviation Electronics Industry Ltd. (JAE)

Ron Muir Japan Aviation Electronics Industry Ltd. (JAE)

Kazuhiro Saito Japan Aviation Electronics Industry Ltd. (JAE)

Hitoshi Kawamura Mitsumi Takashi Kawasaki Mitsumi Atsushi Nishio Mitsumi Yasuhiko Shinohara Mitsumi Tom Lu Molex Inc. Edmund Poh Molex Inc. Scott Sommers Molex Inc. Jason Squire Molex Inc.

Dat Ba Nguyen NTS/National Technical System

Jan Fahllund Nokia Richard Petrie Nokia Panu Ylihaavisto Nokia

Martin FuruhjelmSeagate Technology LLCJulian GorfajnSeagate Technology LLCMarc HildebrantSeagate Technology LLCTony PriborskySeagate Technology LLCHarold ToSeagate Technology LLC

Robert Lefferts Synopsys, Inc. Saleem Mohammad Synopsys, Inc. Matthew Myers Synopsys, Inc. Synopsys, Inc. Daniel Weinlader Mike Engbretson Tektronix, Inc. Thomas Grzysiewicz Tyco Electronics Masaaki Iwasaki Tyco Electronics Kazukiyo Osada Tyco Electronics Hiroshi Shirai Tyco Electronics Scott Shuey Tyco Electronics Masaru Ueno Tyco Electronics

# **Contents**

| 1  | Intro | duction    |                                                       | 1-1 |

|----|-------|------------|-------------------------------------------------------|-----|

|    | 1.1   | Motivation | 1                                                     | 1-1 |

|    | 1.2   |            | of the Specification                                  |     |

|    | 1.3   | Scope of t | the Document                                          | 1-2 |

|    | 1.4   |            | uct Compliance                                        |     |

|    | 1.5   | Document   | t Organization                                        | 1-3 |

|    | 1.6   | •          | oals                                                  |     |

|    | 1.7   | Related D  | ocuments                                              | 1-3 |

| 2  | Term  | s and Ab   | breviations                                           | 2-1 |

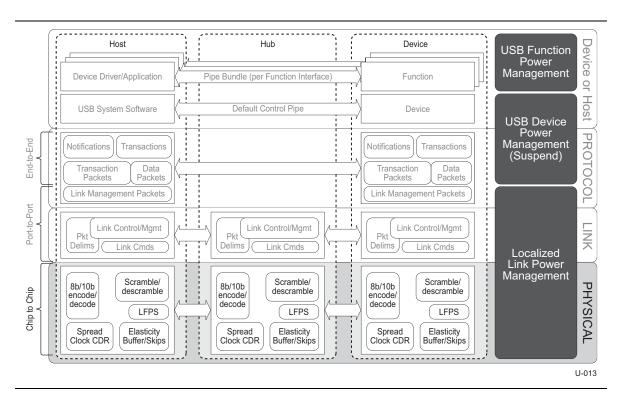

| 3  | USB   | 3.0 Archi  | itectural Overview                                    | 3-1 |

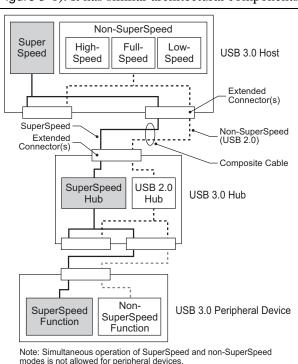

|    | 3.1   | USB 3.0 S  | System Description                                    | 3-1 |

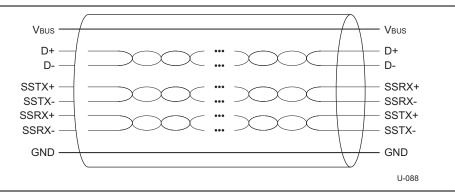

|    |       | 3.1.1      | USB 3.0 Physical Interface                            |     |

|    |       |            | 3.1.1.1 USB 3.0 Mechanical                            |     |

|    |       | 3.1.2      | USB 3.0 Power                                         |     |

|    |       | 3.1.3      | USB 3.0 System Configuration                          |     |

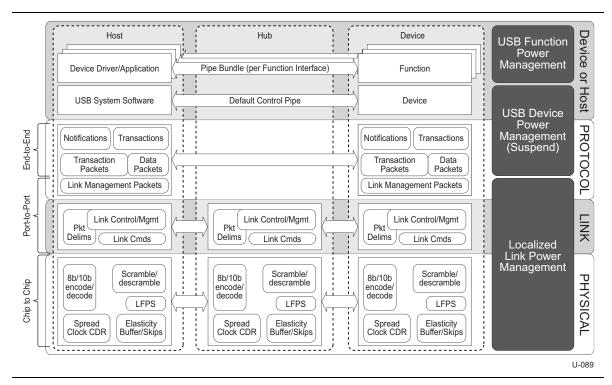

|    |       | 3.1.4      | USB 3.0 Architecture Summary                          |     |

|    | 3.2   |            | ed Architecture                                       |     |

|    |       | 3.2.1      | Physical Layer                                        |     |

|    |       | 3.2.2      | Link Layer                                            |     |

|    |       | 3.2.3      | Protocol Layer                                        |     |

|    |       | 3.2.4      | Robustness                                            |     |

|    |       |            | 3.2.4.1 Error Detection                               |     |

|    |       | 3.2.5      | SuperSpeed Power Management                           |     |

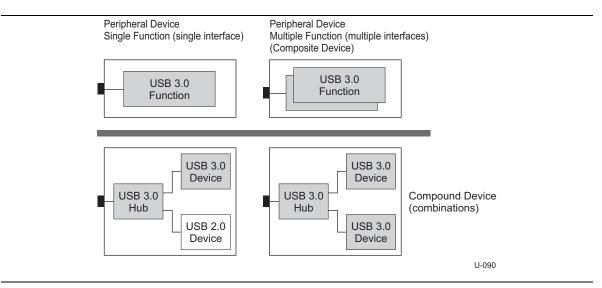

|    |       | 3.2.6      | Devices                                               |     |

|    |       | 3.2.0      | 3.2.6.1 Peripheral Devices                            |     |

|    |       |            | 3.2.6.2 Hubs                                          |     |

|    |       | 3.2.7      | Hosts                                                 |     |

|    |       | 3.2.8      | Data Flow Models                                      |     |

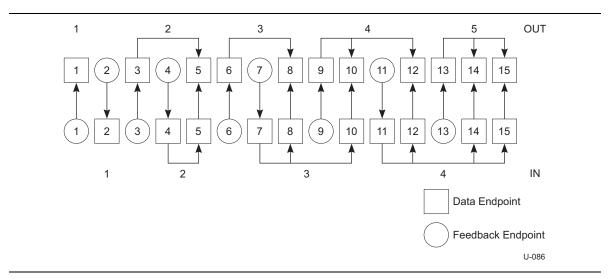

| 4. | Supe  | rSpeed [   | Data Flow Model                                       | 4-1 |

|    | 4.1   | -          | ter Viewpoints                                        |     |

|    | 4.2   |            | ed Communication Flow                                 |     |

|    |       |            | Pipes                                                 |     |

|    | 4.3   |            | ed Protocol Overview                                  |     |

|    |       | 4.3.1      | Differences from USB 2.0                              |     |

|    |       |            | 4.3.1.1 Comparing USB 2.0 and SuperSpeed Transactions | 4-3 |

|    |       |            | 4.3.1.2 Introduction to SuperSpeed Packets            | 4-4 |

|    | 4.4   | Generaliz  | ed Transfer Description                               |     |

|    |       | 4.4.1      | Data Bursting                                         |     |

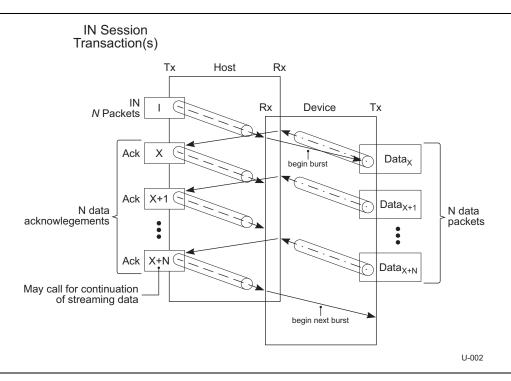

|    |       | 4.4.2      | IN Transfers                                          | 4-5 |

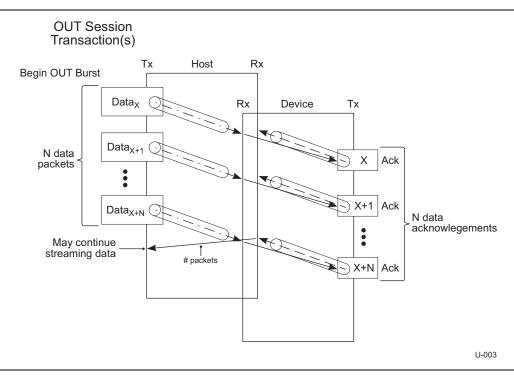

|    |       | 4.4.3      | OUT Transfers                                         |     |

|    |       | 4.4.4      | Power Management and Performance                      | 4-7 |

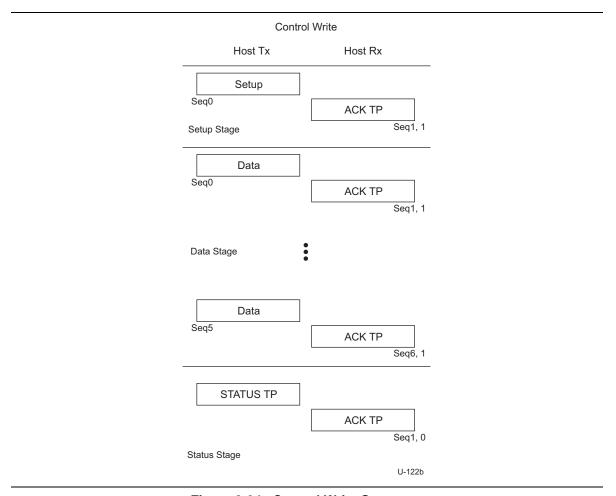

|   |            | 4.4.5  | Control Transf        | ers                                              | 4-8        |

|---|------------|--------|-----------------------|--------------------------------------------------|------------|

|   |            |        | 4.4.5.1               | Control Transfer Packet Size                     | 4-8        |

|   |            |        | 4.4.5.2               | Control Transfer Bandwidth Requirements          | 4-8        |

|   |            |        | 4.4.5.3               | Control Transfer Data Sequences                  |            |

|   |            | 4.4.6  | <b>Bulk Transfers</b> | · · · · · · · · · · · · · · · · · · ·            |            |

|   |            |        | 4.4.6.1               | Bulk Transfer Data Packet Size                   | 4-9        |

|   |            |        | 4.4.6.2               | Bulk Transfer Bandwidth Requirements             | 4-10       |

|   |            |        | 4.4.6.3               | Bulk Transfer Data Sequences                     | 4-10       |

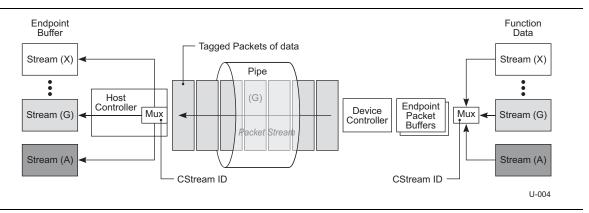

|   |            |        | 4.4.6.4               | Bulk Streams                                     | 4-11       |

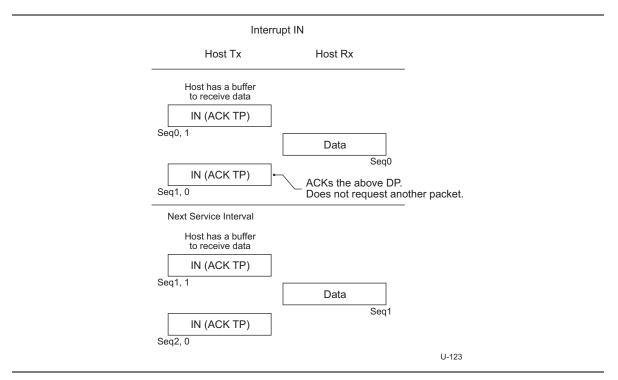

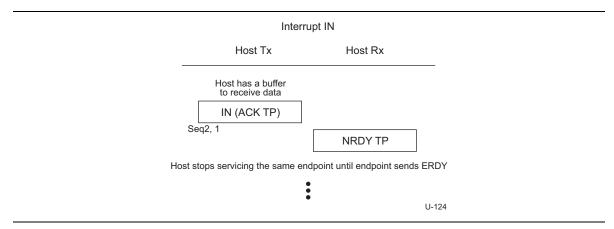

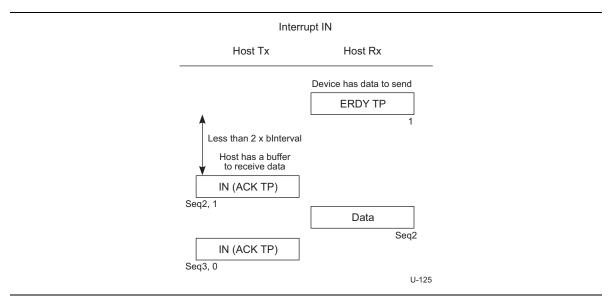

|   |            | 4.4.7  | Interrupt Trans       | sfers                                            | 4-12       |

|   |            |        | 4.4.7.1               | Interrupt Transfer Packet Size                   | 4-13       |

|   |            |        | 4.4.7.2               | Interrupt Transfer Bandwidth Requirements        | 4-13       |

|   |            |        | 4.4.7.3               | Interrupt Transfer Data Sequences                |            |

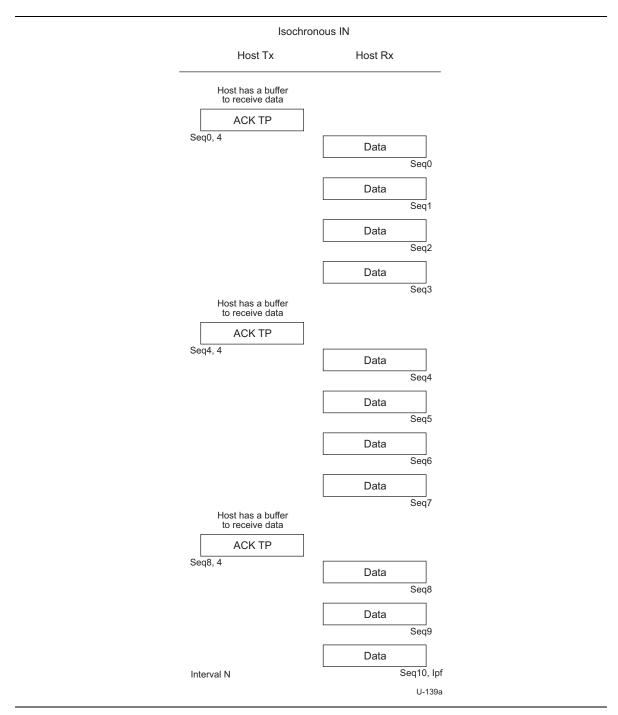

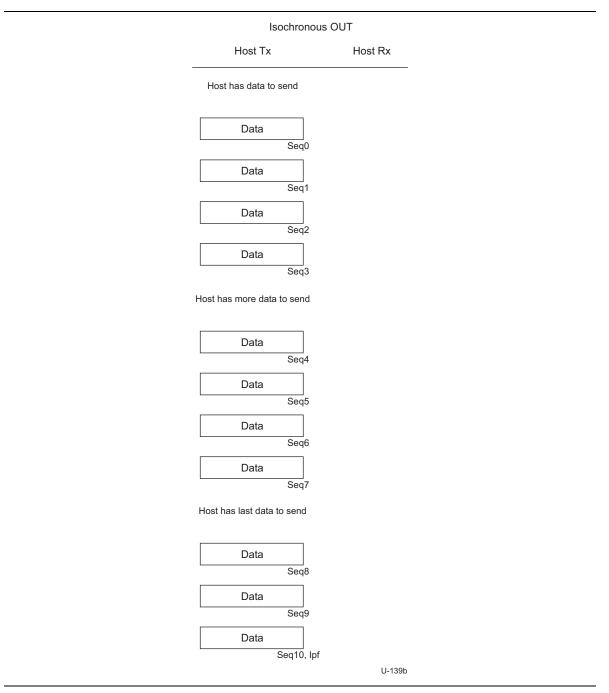

|   |            | 4.4.8  | Isochronous T         | ransfers                                         | 4-14       |

|   |            |        | 4.4.8.1               | Isochronous Transfer Packet Size                 | 4-15       |

|   |            |        | 4.4.8.2               | Isochronous Transfer Bandwidth Requirements      | 4-15       |

|   |            |        | 4.4.8.3               | Isochronous Transfer Data Sequences              |            |

|   |            | 4.4.9  | Device Notifica       | ations                                           | 4-16       |

|   |            | 4.4.10 | Reliability           |                                                  | 4-16       |

|   |            |        | 4.4.10.1              | Physical Layer                                   |            |

|   |            |        | 4.4.10.2              | Link Layer                                       |            |

|   |            |        | 4.4.10.3              | Protocol Layer                                   |            |

|   |            | 4.4.11 | Efficiency            | ······································           |            |

| 5 | Moch       | anical |                       |                                                  | <b>5</b> 1 |

| J |            |        |                       |                                                  |            |

|   | 5.1        | •      |                       |                                                  |            |

|   | 5.2        | •      |                       |                                                  |            |

|   |            | 5.2.1  |                       | LICE 2.0 Charderd A. Commonton                   |            |

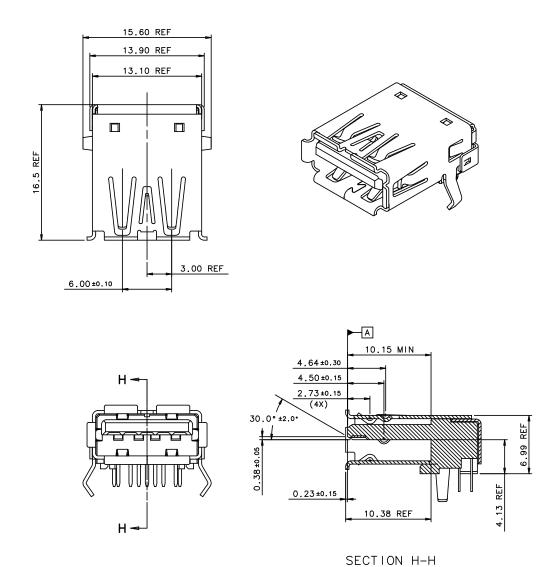

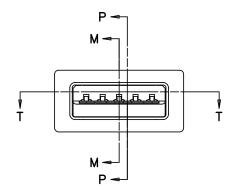

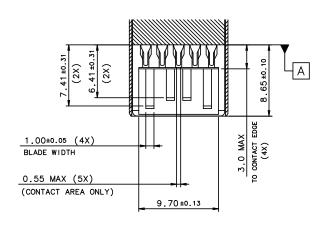

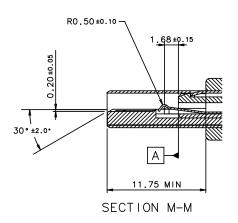

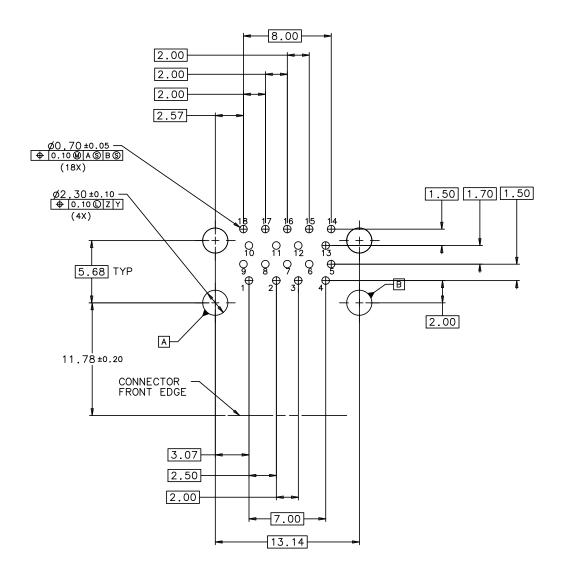

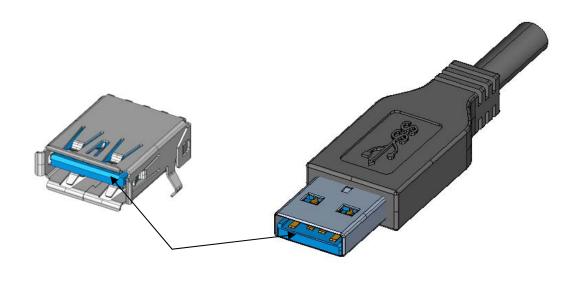

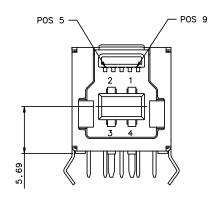

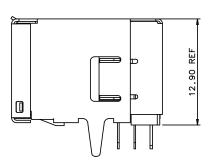

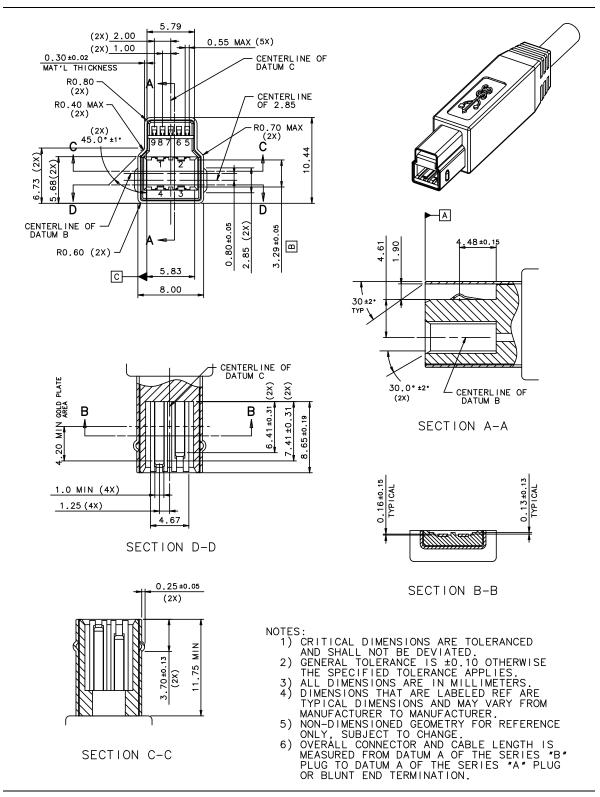

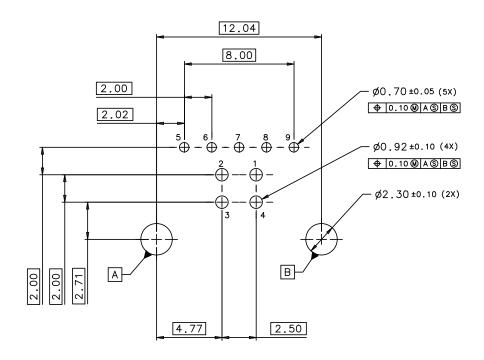

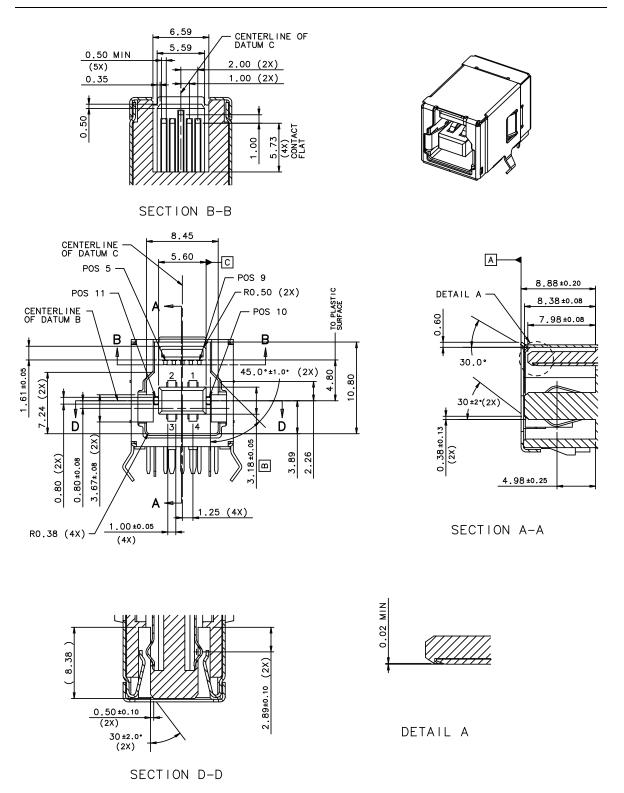

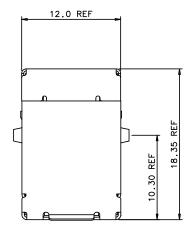

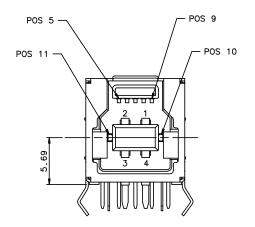

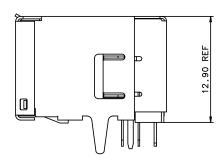

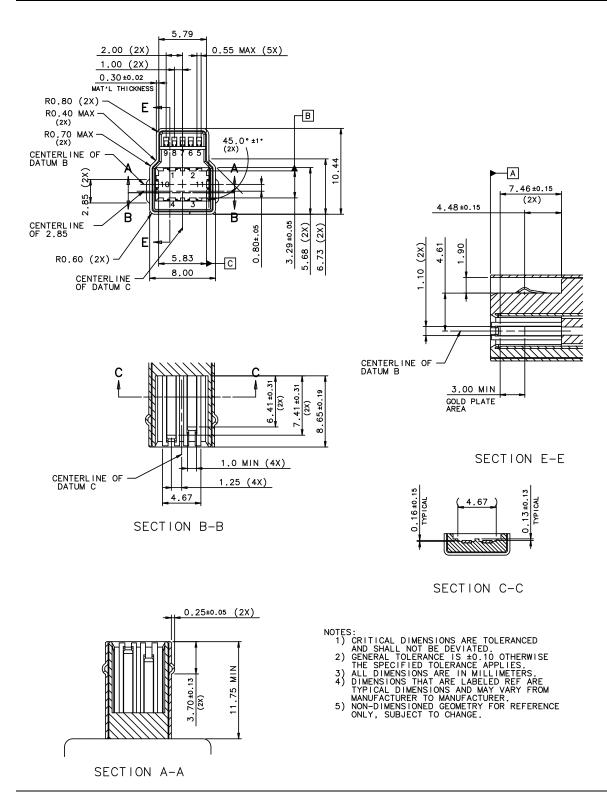

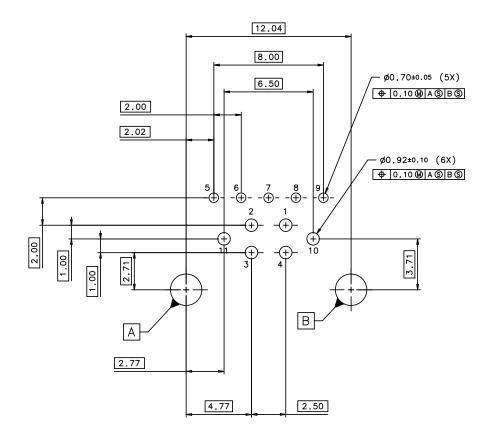

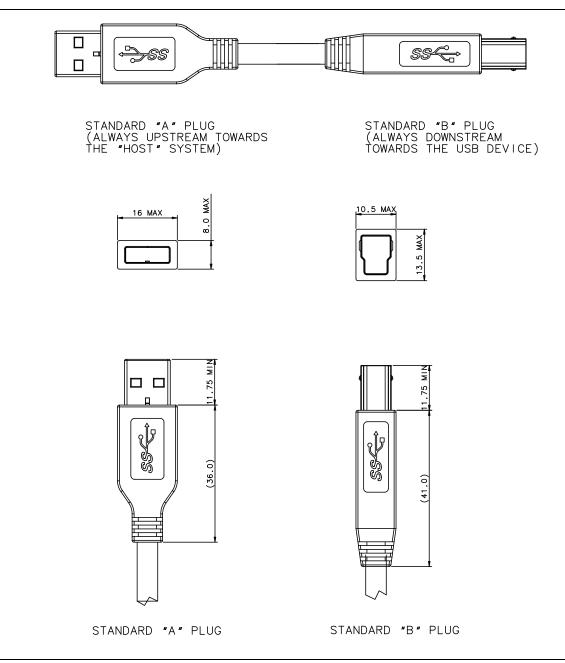

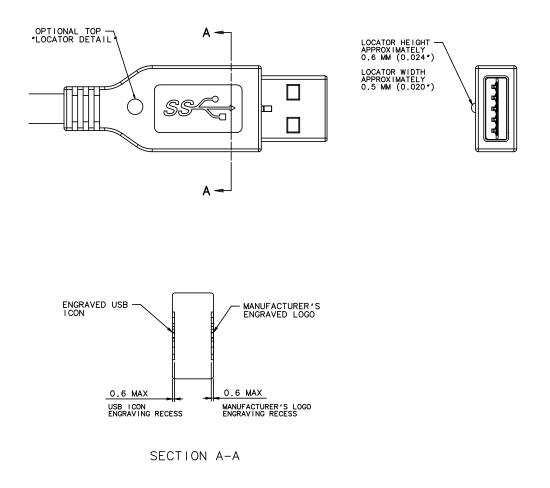

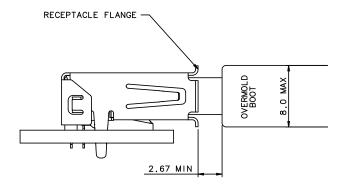

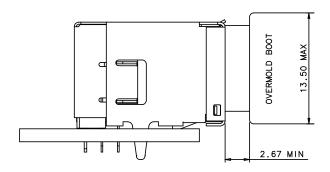

|   |            |        | 5.2.1.1               | USB 3.0 Standard-A Connector                     |            |

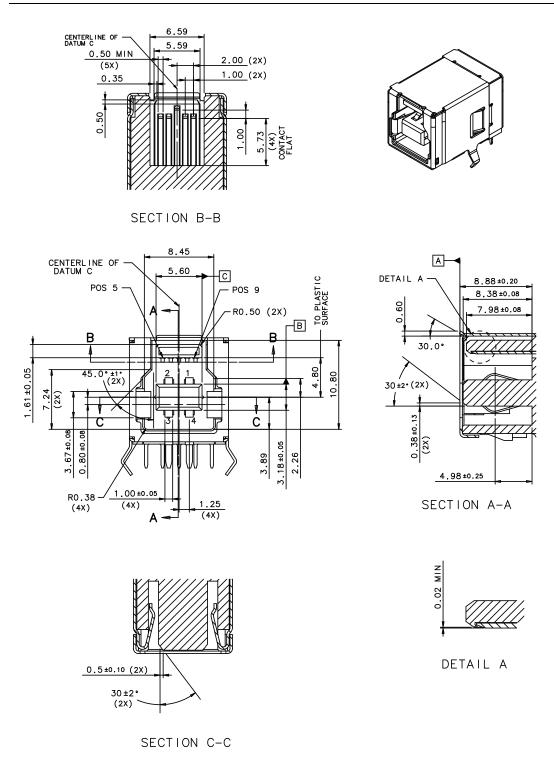

|   |            |        | 5.2.1.2               | USB 3.0 Standard-B Connector                     |            |

|   |            |        | 5.2.1.3               | USB 3.0 Powered-B Connector                      |            |

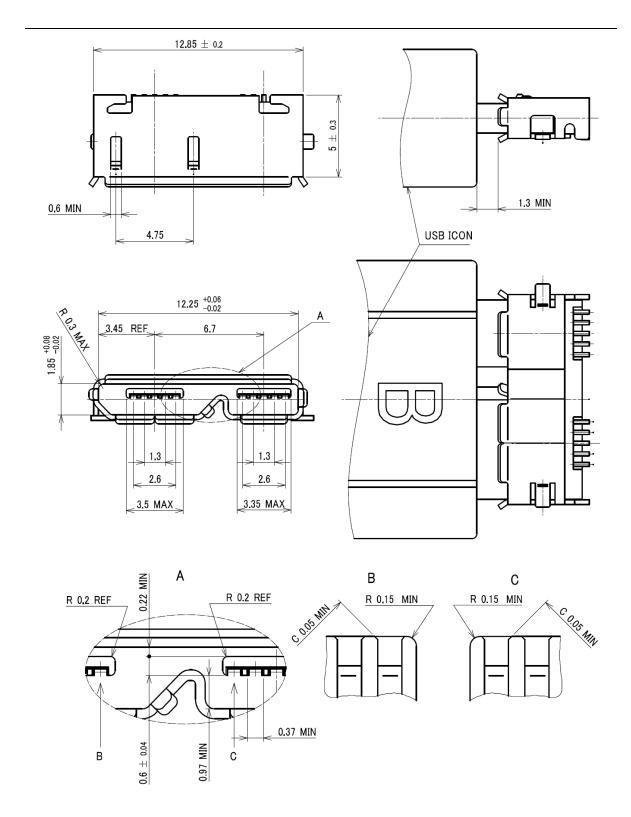

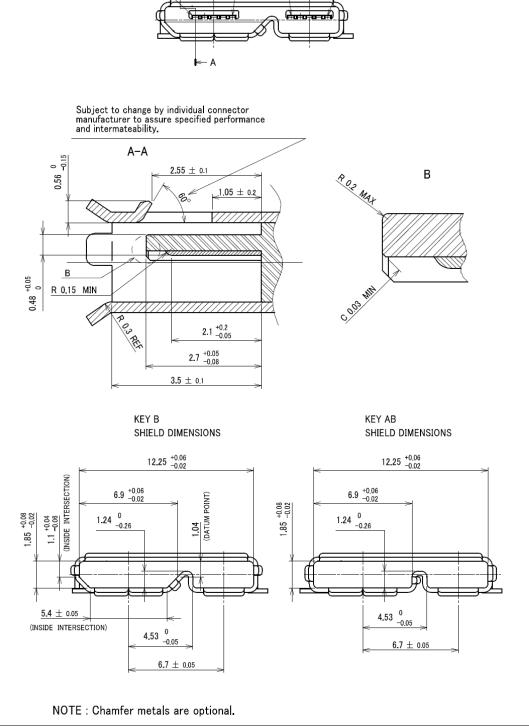

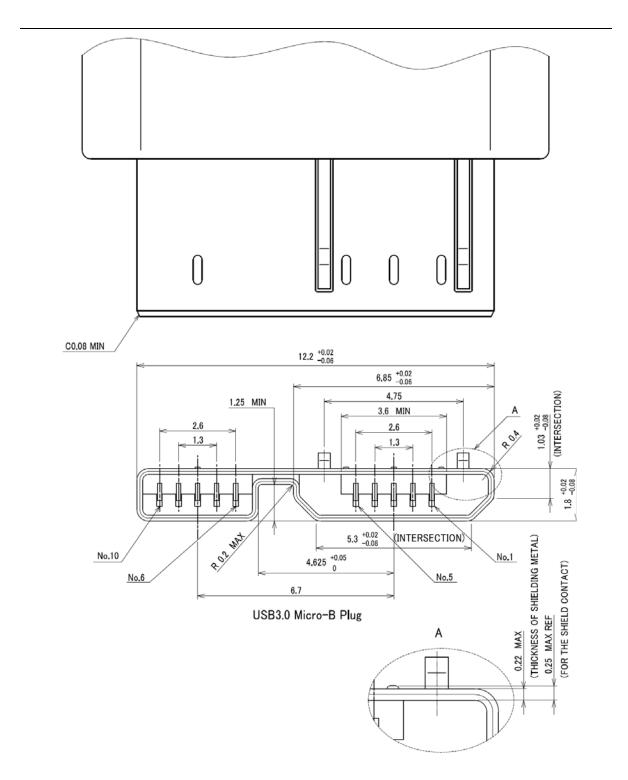

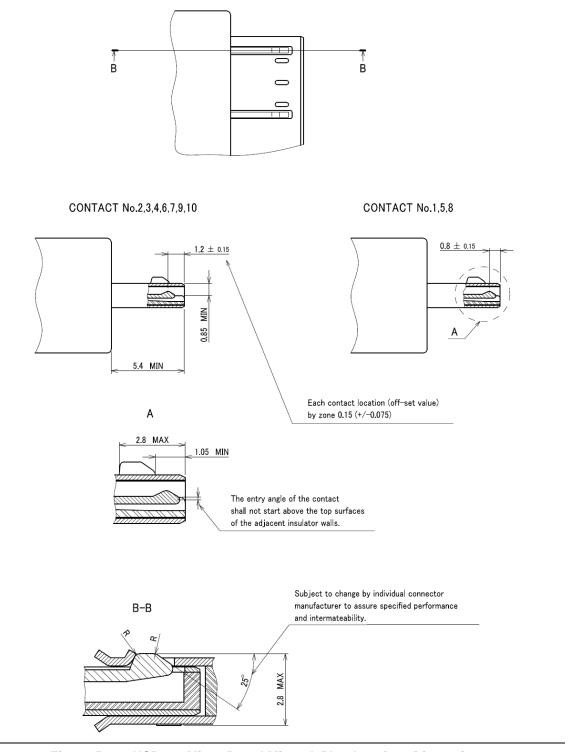

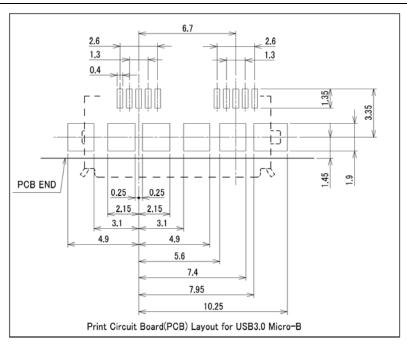

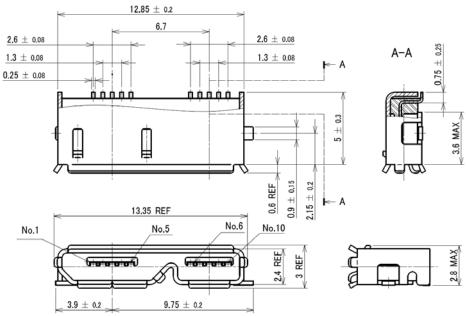

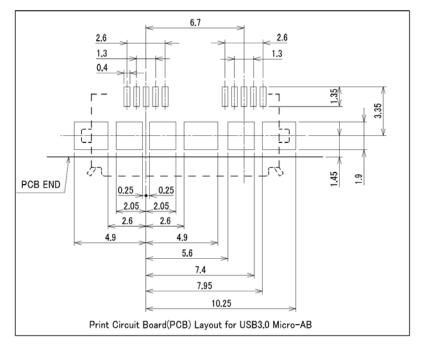

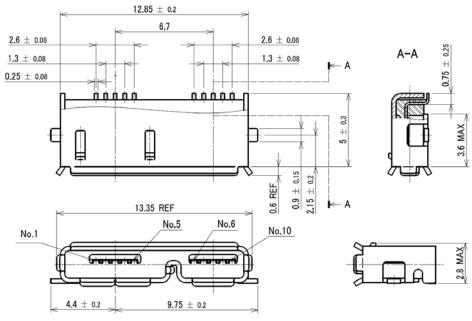

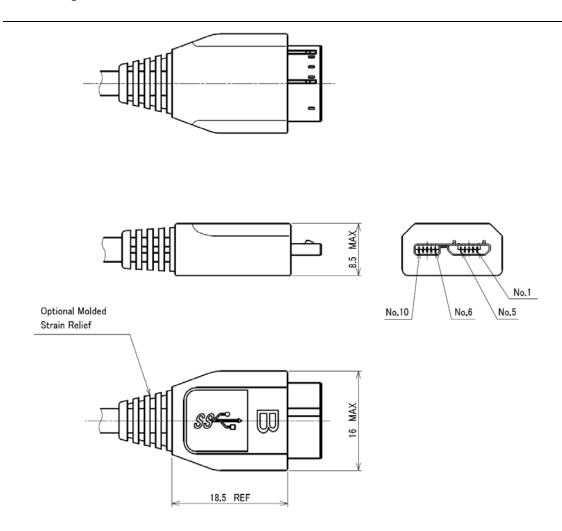

|   |            |        | 5.2.1.4               | USB 3.0 Micro-B Connector                        |            |

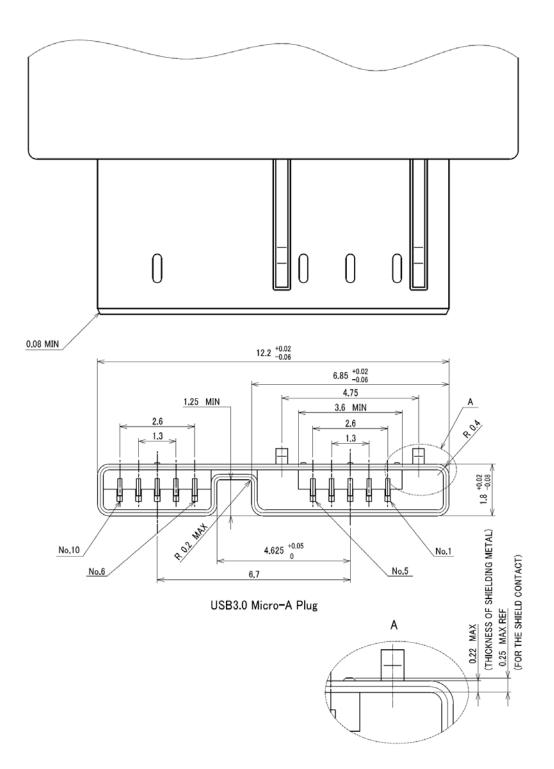

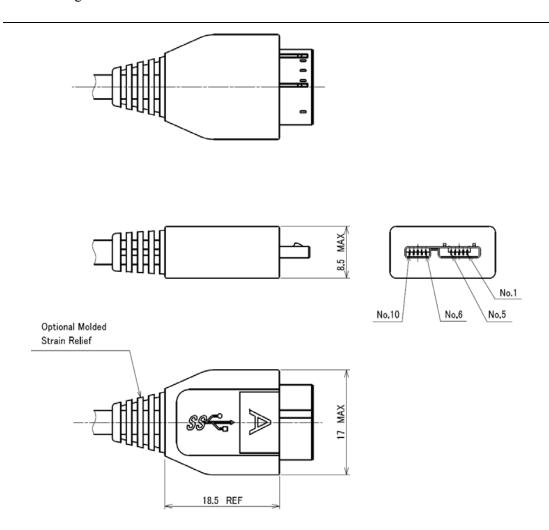

|   |            | 500    | 5.2.1.5               | USB 3.0 Micro-AB and USB 3.0 Micro-A Connectors. |            |

|   |            | 5.2.2  | •                     | ble Assemblies                                   |            |

|   | <b>-</b> 0 | 5.2.3  |                       |                                                  |            |

|   | 5.3        |        | 0                     | Ces                                              |            |

|   |            | 5.3.1  |                       | dard-A Connector                                 |            |

|   |            |        | 5.3.1.1               | Interface Definition                             |            |

|   |            |        | 5.3.1.2               | Pin Assignments and Description                  |            |

|   |            | F 2 2  | 5.3.1.3               | USB 3.0 Standard-A Connector Color Coding        |            |

|   |            | 5.3.2  |                       | dard-B Connector                                 |            |

|   |            |        | 5.3.2.1               | Interface Definition                             |            |

|   |            | F 2 2  | 5.3.2.2               | Pin Assignments and Description                  |            |

|   |            | 5.3.3  |                       | ered-B Connector                                 |            |

|   |            |        | 5.3.3.1               | Interface Definition                             |            |

|   |            | E 2 4  | 5.3.3.2               | Pin Assignments and Descriptions                 |            |

|   |            | 5.3.4  |                       | Connector Family                                 |            |

|   |            |        | 5.3.4.1<br>5.3.4.2    | Interfaces Definition                            |            |

|   |            |        | 2347                  | Pin Assignments and Description                  | 2-33       |

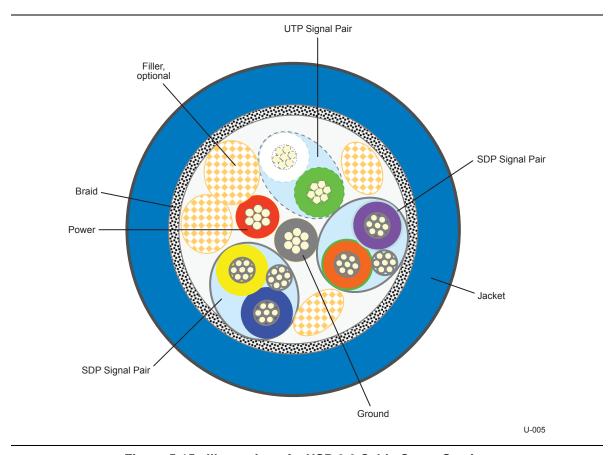

| 5.4 | Cable Co                              | onstruction and | Wire Assignments                                       | 5-35 |

|-----|---------------------------------------|-----------------|--------------------------------------------------------|------|

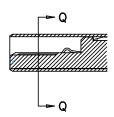

|     | 5.4.1                                 |                 | uction                                                 |      |

|     | 5.4.2                                 | Wire Assignm    | nents                                                  | 5-36 |

|     | 5.4.3 Wire Gauges and Cable Diameters |                 |                                                        |      |

| 5.5 | Cable As                              |                 |                                                        |      |

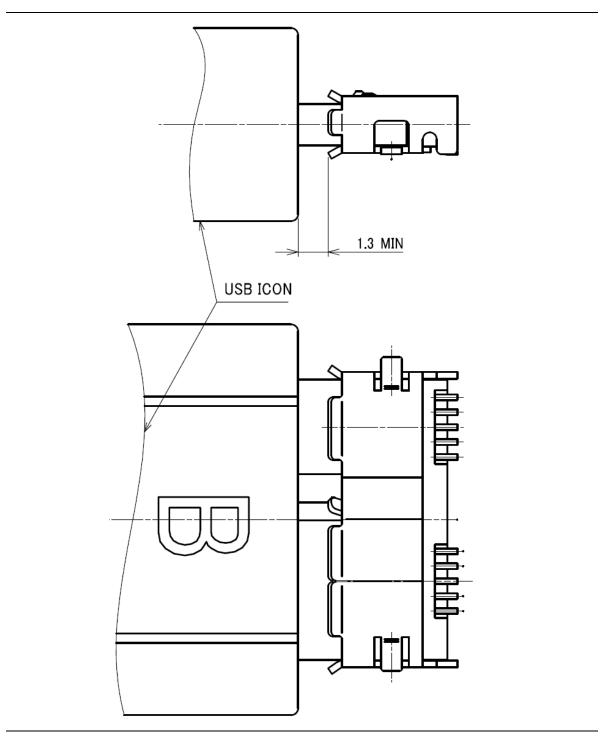

|     | 5.5.1                                 | USB 3.0 Stan    | dard-A to USB 3.0 Standard-B Cable Assembly            | 5-37 |

|     | 5.5.2                                 | USB 3.0 Stan    | dard-A to USB 3.0 Standard-A Cable Assembly            | 5-38 |

|     | 5.5.3                                 | USB 3.0 Stan    | dard-A to USB 3.0 Micro-B Cable Assembly               | 5-39 |

|     | 5.5.4                                 | USB 3.0 Micro   | o-A to USB 3.0 Micro-B Cable Assembly                  | 5-41 |

|     | 5.5.5                                 | USB 3.0 Micro   | o-A to USB 3.0 Standard-B Cable Assembly               | 5-43 |

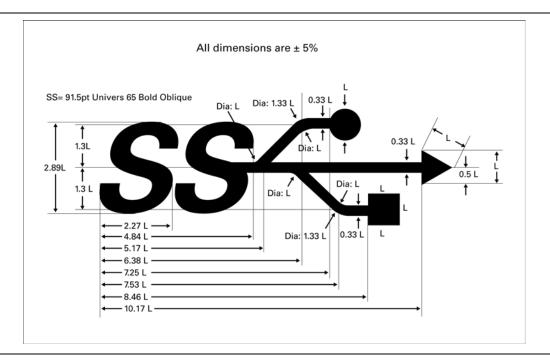

|     | 5.5.6                                 | USB 3.0 Icon    | Location                                               | 5-44 |

|     | 5.5.7                                 | Cable Assem     | bly Length                                             | 5-45 |

| 5.6 | Electrica                             | I Requirements  |                                                        | 5-46 |

|     | 5.6.1                                 | SuperSpeed I    | Electrical Requirements                                | 5-46 |

|     |                                       | 5.6.1.1         | Raw Cable                                              | 5-46 |

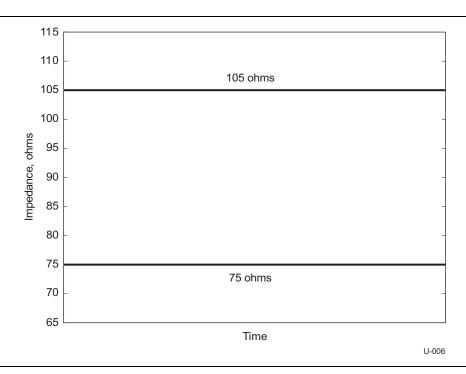

|     |                                       | 5.6.1.1.1       | Characteristic Impedance                               | 5-46 |

|     |                                       | 5.6.1.1.2       | Intra-Pair Skew                                        |      |

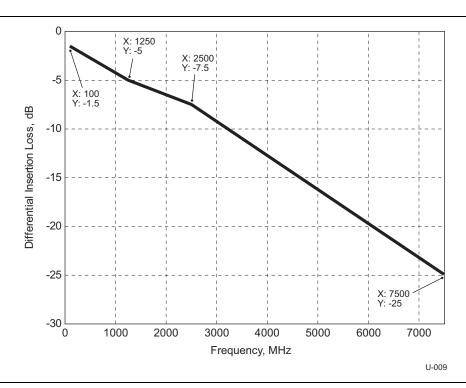

|     |                                       | 5.6.1.1.3       | Differential Insertion Loss                            | 5-47 |

|     |                                       | 5.6.1.2         | Mated Connector                                        |      |

|     |                                       | 5.6.1.3         | Mated Cable Assemblies                                 |      |

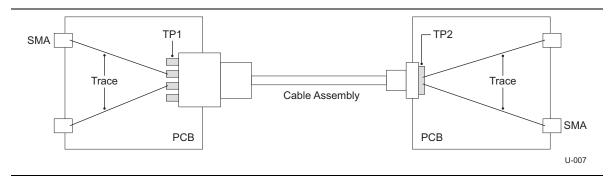

|     |                                       | 5.6.1.3.1       | Differential Insertion Loss (EIA-360-101)              | 5-49 |

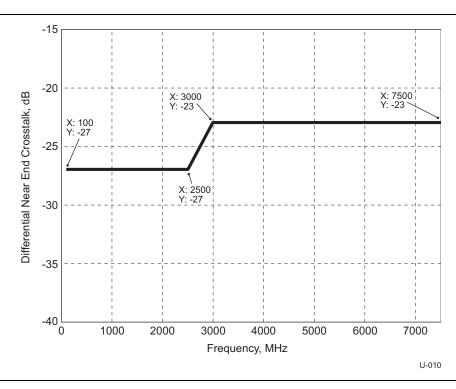

|     |                                       | 5.6.1.3.2       | Differential Near-End Crosstalk between                |      |

|     |                                       |                 | SuperSpeed Pairs (EIA-360-90)                          | 5-50 |

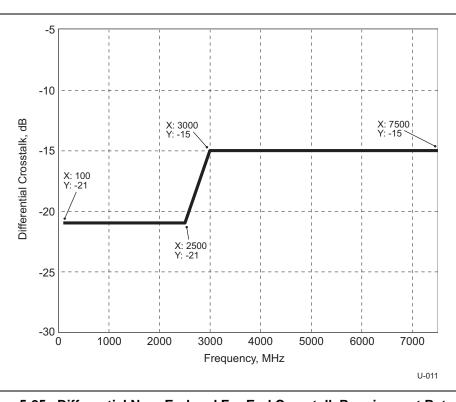

|     |                                       | 5.6.1.3.3       | Differential Crosstalk between D+/D- and               |      |

|     |                                       |                 | SuperSpeed Pairs (EIA-360-90)                          | 5-51 |

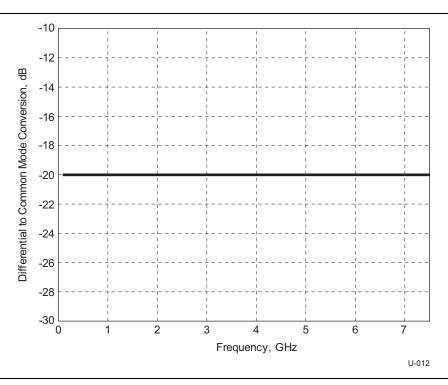

|     |                                       | 5.6.1.3.4       | Differential-to-Common-Mode Conversion                 |      |

|     | 5.6.2                                 |                 | Requirements                                           |      |

|     |                                       | 5.6.2.1         | Low Level Contact Resistance (EIA 364-23B)             |      |

|     |                                       | 5.6.2.2         | Dielectric Strength (EIA 364-20)                       |      |

|     |                                       | 5.6.2.3         | Insulation Resistance (EIA 364-21)                     |      |

|     |                                       | 5.6.2.4         | Contact Current Rating (EIA 364-70, Method 2)          |      |

| 5.7 |                                       |                 | mental Requirements                                    |      |

|     | 5.7.1                                 |                 | equirements                                            |      |

|     |                                       | 5.7.1.1         | Insertion Force (EIA 364-13)                           |      |

|     |                                       | 5.7.1.2         | Extraction Force (EIA 364-13)                          | 5-53 |

|     |                                       | 5.7.1.3         | Durability or Insertion/Extraction Cycles (EIA 364-09) |      |

|     |                                       | 5.7.1.4         | Cable Flexing (EIA 364-41, Condition I)                |      |

|     |                                       | 5.7.1.5         | Cable Pull-Out (EIA 364-38, Condition A)               | 5-54 |

|     |                                       | 5.7.1.6         | Peel Strength (USB 3.0 Micro Connector                 |      |

|     |                                       |                 | Family Only)                                           | 5-54 |

|     |                                       | 5.7.1.7         | 4-Axes Continuity Test (USB 3.0 Micro Connector        |      |

|     |                                       |                 | Family Only)                                           | 5-54 |

|     |                                       | 5.7.1.8         | Wrenching Strength (Reference, USB 3.0 Micro           |      |

|     |                                       |                 | Connector Family Only)                                 |      |

|     |                                       | 5.7.1.9         | Lead Co-Planarity                                      |      |

|     |                                       | 5.7.1.10        | Solderability                                          | 5-56 |

|     |                                       | 5.7.1.11        | Restriction of Hazardous Substances (RoHS)             |      |

|     | <b>5 7 0</b>                          | F               | Compliance                                             |      |

|     | 5.7.2                                 | ⊢nvironmenta    | al Requirements                                        | 5-56 |

|   |      | 5.7.3       | Materials                                          | 5-57 |

|---|------|-------------|----------------------------------------------------|------|

|   | 5.8  | Implemer    | ntation Notes and Design Guides                    | 5-57 |

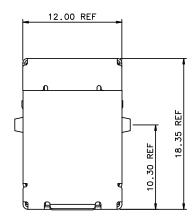

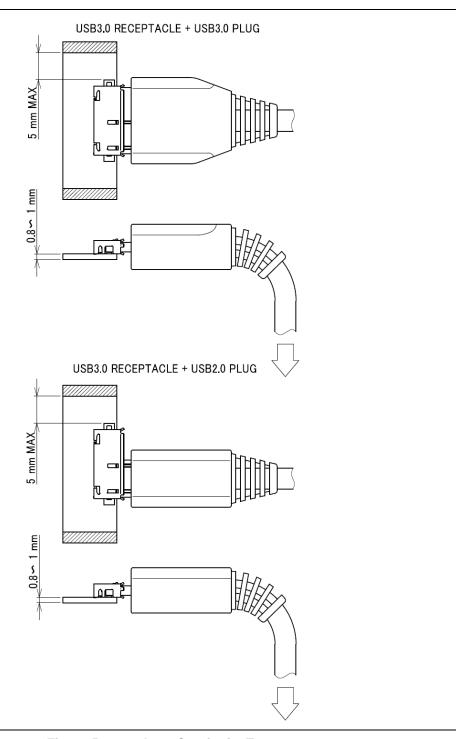

|   |      | 5.8.1       | Mated Connector Dimensions                         | 5-57 |

|   |      | 5.8.2       | EMI Management                                     | 5-60 |

|   |      | 5.8.3       | Stacked Connectors                                 | 5-60 |

| 6 | Phys | ical Laye   | er                                                 | 6-1  |

|   | 6.1  | Physical I  | Layer Overview                                     | 6-1  |

|   | 6.2  | Physical I  | Layer Functions                                    | 6-1  |

|   |      | 6.2.1       | Measurement Overview                               | 6-4  |

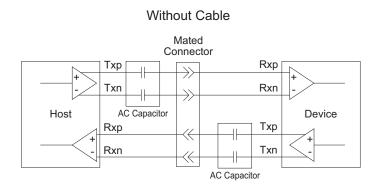

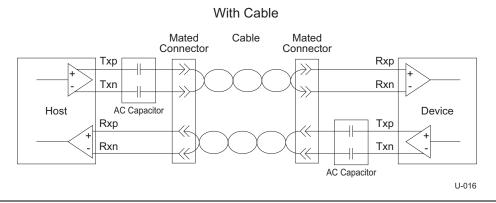

|   |      | 6.2.2       | Channel Overview                                   | 6-5  |

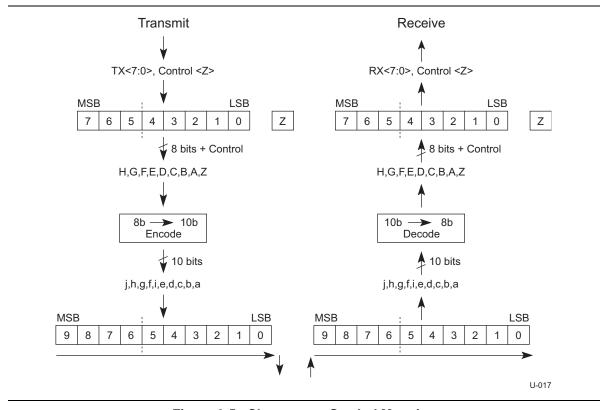

|   | 6.3  | Symbol E    | ncoding                                            | 6-5  |

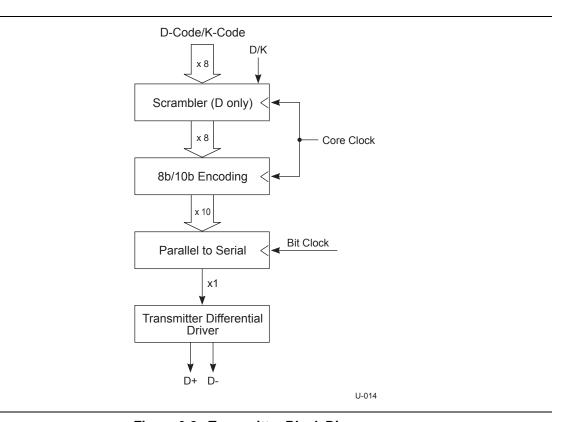

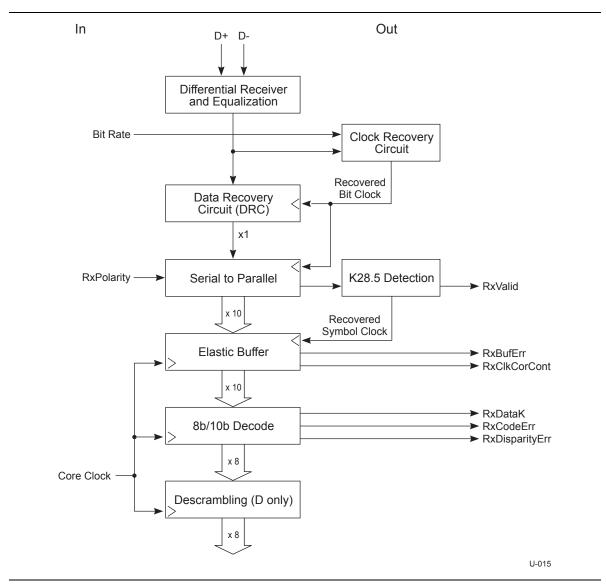

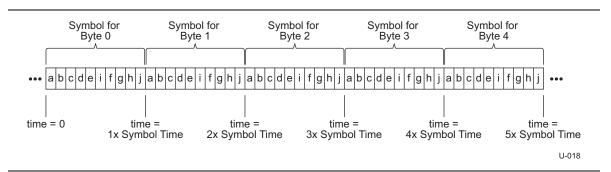

|   |      | 6.3.1       | Serialization and Deserialization of Data          | 6-6  |

|   |      | 6.3.2       | Normative 8b/10b Decode Rules                      | 6-6  |

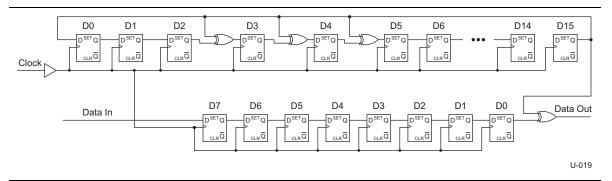

|   |      | 6.3.3       | Data Scrambling                                    | 6-6  |

|   |      | 6.3.4       | 8b/10b Decode Errors                               | 6-7  |

|   |      | 6.3.5       | Special Symbols for Framing and Link Management    | 6-8  |

|   | 6.4  | Link Initia | ilization and Training                             | 6-8  |

|   |      | 6.4.1       | Normative Training Sequence Rules                  |      |

|   |      |             | 6.4.1.1 Training Control Bits                      | 6-9  |

|   |      |             | 6.4.1.2 Training Sequence Values                   | 6-9  |

|   |      | 6.4.2       | Lane Polarity Inversion                            | 6-11 |

|   |      | 6.4.3       | Elasticity Buffer and SKP Ordered Set              | 6-11 |

|   |      | 6.4.4       | Compliance Pattern                                 | 6-12 |

|   | 6.5  | Clock and   | d Jitter                                           | 6-13 |

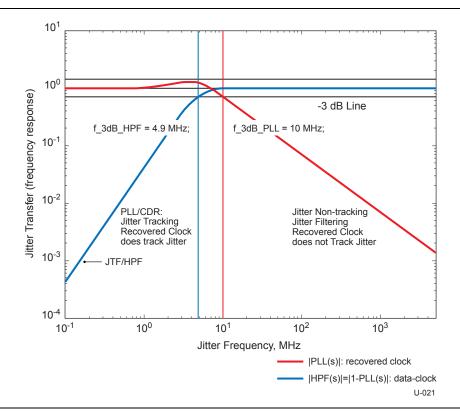

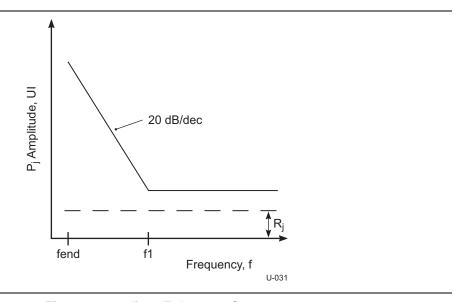

|   |      | 6.5.1       | Informative Jitter Budgeting                       | 6-13 |

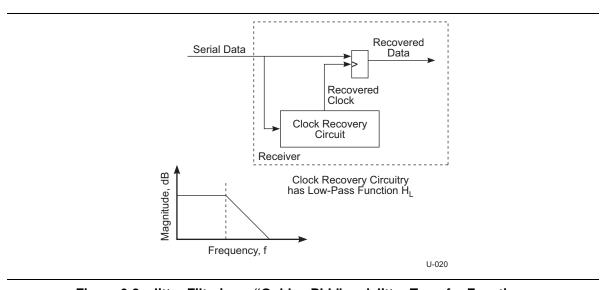

|   |      | 6.5.2       | Normative Clock Recovery Function                  | 6-14 |

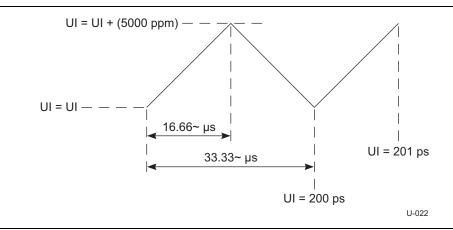

|   |      | 6.5.3       | Normative Spread Spectrum Clocking (SSC)           | 6-16 |

|   |      | 6.5.4       | Normative Slew Rate Limit                          |      |

|   | 6.6  | Signaling   |                                                    | 6-17 |

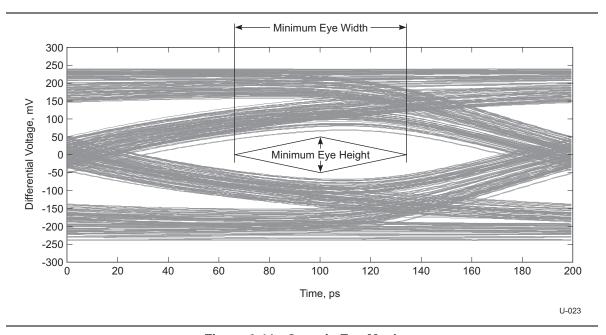

|   |      | 6.6.1       | Eye Diagrams                                       | 6-17 |

|   |      | 6.6.2       | Voltage Level Definitions                          | 6-18 |

|   |      | 6.6.3       | Tx and Rx Input Parasitics                         | 6-19 |

|   | 6.7  | Transmitt   | er Specifications                                  | 6-20 |

|   |      | 6.7.1       | Transmitter Electrical Parameters                  | 6-20 |

|   |      | 6.7.2       | Low Power Transmitter                              | 6-21 |

|   |      | 6.7.3       | Transmitter Eye                                    | 6-22 |

|   |      | 6.7.4       | Tx Compliance Reference Receiver Equalize Function | 6-22 |

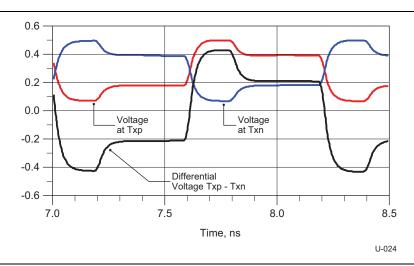

|   |      | 6.7.5       | Informative Transmitter De-emphasis                | 6-23 |

|   |      | 6.7.6       | Entry into Electrical Idle, U1                     | 6-23 |

|   | 6.8  | Receiver    | Specifications                                     |      |

|   |      | 6.8.1       | Receiver Equalization Training                     | 6-24 |

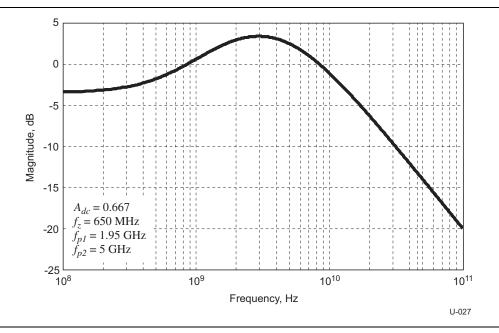

|   |      | 6.8.2       | Informative Receiver CTLE Function                 | 6-24 |

|   |      | 6.8.3       | Receiver Electrical Parameters                     | 6-26 |

|   |      | 6.8.4       | Receiver Loopback                                  | 6-27 |

|   |      |             | 6.8.4.1 Loopback BERT                              |      |

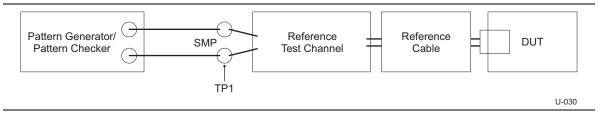

|   |      | 6.8.5       | Normative Receiver Tolerance Compliance Test       | 6-29 |

|   | 6.9  | Low Freq    | uency Periodic Signaling (LFPS)                    | 6-30 |

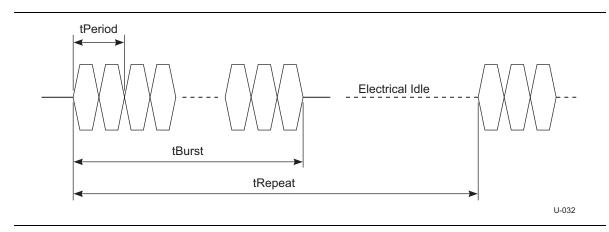

|   |      | 6.9.1       | LFPS Signal Definition                             |      |

|   |      | 6.9.2  | Example LFPS Handshake for U1/U2 Exit, Loopback Exit, and U3   | 0.00 |

|---|------|--------|----------------------------------------------------------------|------|

|   |      | 0.00   | Wakeup                                                         |      |

|   | 0.40 | 6.9.3  | Warm Reset                                                     |      |

|   | 6.10 |        | er and Receiver DC Specifications                              |      |

|   |      | 6.10.1 | Informative ESD Protection                                     |      |

|   |      | 6.10.2 | Informative Short Circuit Requirements                         |      |

|   |      | 6.10.3 | Normative High Impedance Reflections                           |      |

|   | 6.11 |        | Detection                                                      |      |

|   |      | 6.11.1 | Rx Detect Overview                                             |      |

|   |      | 6.11.2 | Rx Detect Sequence                                             |      |

|   |      | 6.11.3 | Upper Limit on Channel Capacitance                             | 6-37 |

| 7 | Link | Laver  |                                                                | 7-1  |

| - | 7.1  | •      | ering                                                          |      |

|   | 7.1  | •      | agement and Flow Control                                       |      |

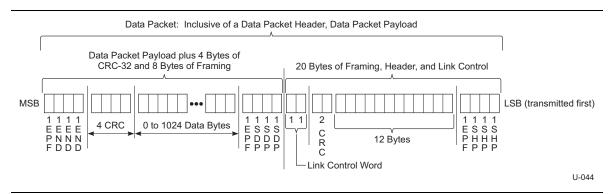

|   | 1.2  | 7.2.1  | Packets and Packet Framing                                     |      |

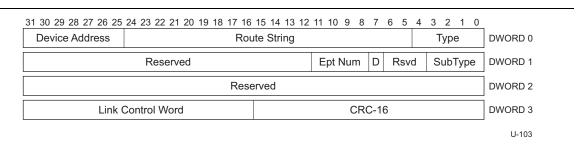

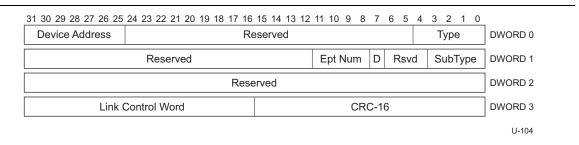

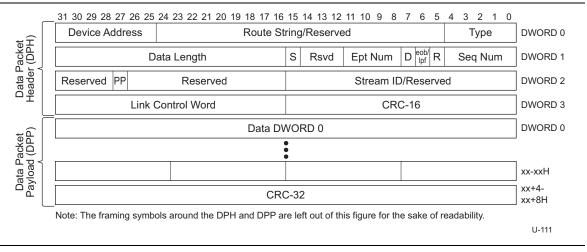

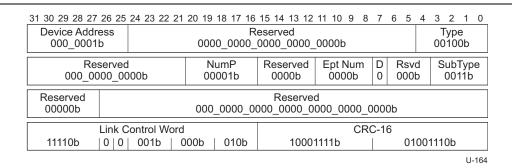

|   |      | 1.2.1  | 7.2.1.1 Header Packet Structure                                |      |

|   |      |        | 7.2.1.1.1 Header Packet Framing                                |      |

|   |      |        | 7.2.1.1.2 Packet Header                                        |      |

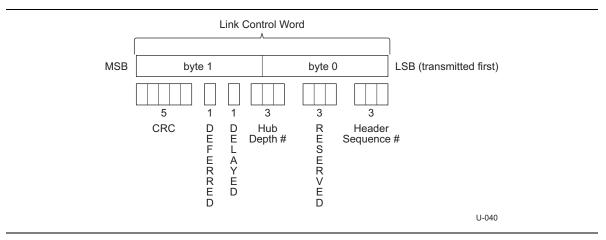

|   |      |        | 7.2.1.1.3 Link Control Word                                    |      |

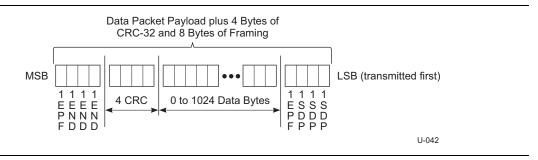

|   |      |        | 7.2.1.2 Data Packet Payload Structure                          |      |

|   |      |        | 7.2.1.2.1 Data Packet Payload Framing                          |      |

|   |      |        | 7.2.1.2.2 Data Packet Payload                                  |      |

|   |      |        | 7.2.1.2.3 Spacing Between Data Packet Header and               | 7    |

|   |      |        | Data Packet Payload                                            | 7-10 |

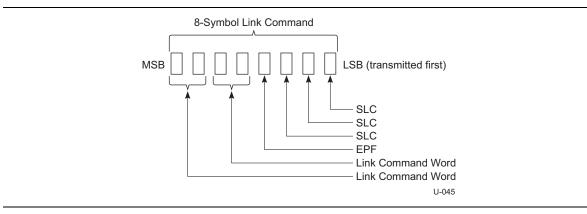

|   |      | 7.2.2  | Link Commands                                                  | 7-10 |

|   |      |        | 7.2.2.1 Link Command Structure                                 |      |

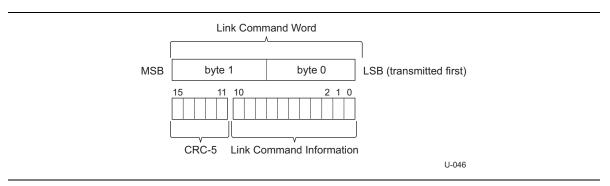

|   |      |        | 7.2.2.2 Link Command Word Definition                           |      |

|   |      |        | 7.2.2.3 Link Command Placement                                 |      |

|   |      | 7.2.3  | Logical Idle                                                   |      |

|   |      | 7.2.4  | Link Command Usage for Flow Control, Error Recovery, and Power |      |

|   |      |        | Management                                                     |      |

|   |      |        | 7.2.4.1 Header Packet Flow Control and Error Recovery          |      |

|   |      |        | 7.2.4.1.1 Initialization                                       |      |

|   |      |        | 7.2.4.1.2 General Rules of LGOOD_n and LCRD_x Usage            |      |

|   |      |        | 7.2.4.1.3 Transmitting Header Packets                          |      |

|   |      |        | 7.2.4.1.4 Receiving Header Packets                             |      |

|   |      |        | 7.2.4.1.5 Rx Header Buffer Credit                              |      |

|   |      |        | 7.2.4.1.6 Receiving Data Packet Payload                        | 7-19 |

|   |      |        | 7.2.4.1.7 Receiving LGOOD_n                                    |      |

|   |      |        | 7.2.4.1.8 Receiving LCRD_x                                     |      |

|   |      |        | 7.2.4.1.9 Receiving LBAD                                       |      |

|   |      |        | 7.2.4.1.10 Transmitter Timers                                  |      |

|   |      |        | 7.2.4.2 Link Power Management and Flow                         | 7-22 |

|   |      |        | 7.2.4.2.1 Power Management Link Timers                         |      |

|   |      |        | 7.2.4.2.2 Low Power Link State Initiation                      |      |

|   |      |        | 7.2.4.2.3 U1/U2 Entry Flow                                     |      |

|   |      |        | 7.2.4.2.4 U3 Entry Flow                                        |      |

|   |      |        | 7.2.4.2.5 Concurrent Low Power Link Management Flow            |      |

|     |            | 7.2.4.2.6          | Concurrent Low Power Link Management       |      |

|-----|------------|--------------------|--------------------------------------------|------|

|     |            |                    | and Recovery Flow                          |      |

|     |            | 7.2.4.2.7          | Low Power Link State Exit Flow             | 7-26 |

| 7.3 | Link Error | Rules/Recove       | ry                                         | 7-26 |

|     | 7.3.1      | Overview of S      | SuperSpeed Bit Errors                      | 7-26 |

|     | 7.3.2      | Link Error Typ     | pes, Detection, and Recovery               | 7-27 |

|     | 7.3.3      | Header Packe       | et Errors                                  | 7-27 |

|     |            | 7.3.3.1            | Packet Framing Error                       |      |

|     |            | 7.3.3.2            | Header Packet Error                        |      |

|     |            | 7.3.3.3            | Rx Header Sequence Number Error            |      |

|     | 7.3.4      | Link Comman        | d Errors                                   |      |

|     | 7.3.5      |                    | ler Sequence Number Error                  |      |

|     | 7.3.6      |                    | ence Number Advertisement Error            |      |

|     | 7.3.7      |                    | uffer Credit Advertisement Error           |      |

|     | 7.3.8      |                    | ience Error                                |      |

|     | 7.3.9      | 8h/10h Frrors      |                                            | 7-31 |

|     | 7.3.10     |                    | Error Types and Recovery                   |      |

| 7.4 |            |                    | and Reset                                  |      |

| 7.4 | 7.4.1      |                    | set                                        |      |

|     | 7.4.1      |                    | 961                                        |      |

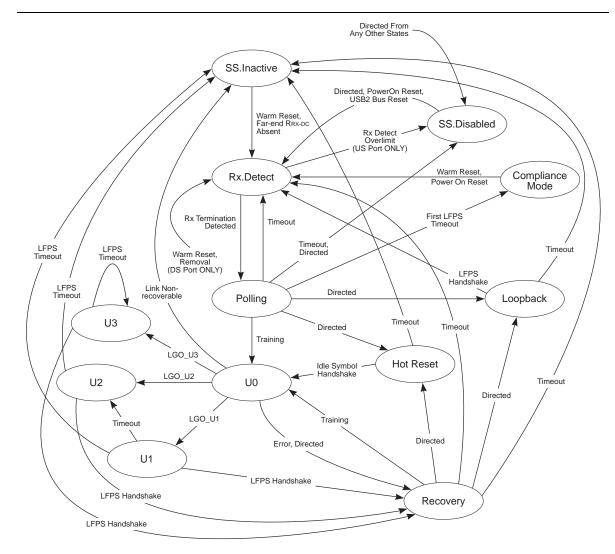

| 7.5 |            |                    | State Machine (LTSSM)                      |      |

| 7.5 | 7.5.1      |                    |                                            |      |

|     | 7.5.1      | 7.5.1.1            | SS.Disabled Requirements                   |      |

|     |            | 7.5.1.1<br>7.5.1.2 | Exit from SS.Disabled                      |      |

|     | 7.5.2      |                    |                                            |      |

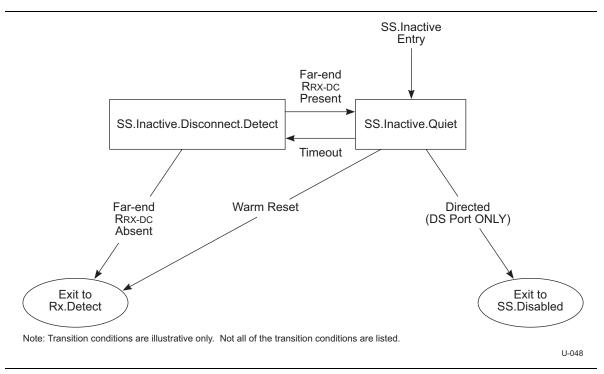

|     | 7.5.2      | SS.Inactive        |                                            |      |

|     |            | 7.5.2.1            | SS.Inactive Substate Machines              |      |

|     |            | 7.5.2.2            | SS.Inactive Requirements                   |      |

|     |            | 7.5.2.3            | SS.Inactive.Quiet                          |      |

|     |            | 7.5.2.3.1          | SS.Inactive.Quiet Requirements             |      |

|     |            | 7.5.2.3.2          | Exit from SS.Inactive.Quiet                |      |

|     |            | 7.5.2.4            | SS.Inactive.Disconnect.Detect              |      |

|     |            | 7.5.2.4.1          | SS.Inactive.Disconnect.Detect Requirements |      |

|     |            | 7.5.2.4.2          | Exit from SS.Inactive.Disconnect.Detect    |      |

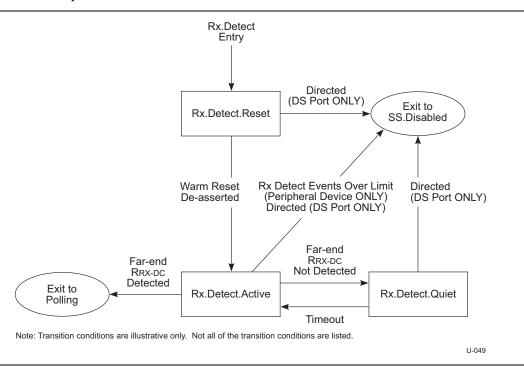

|     | 7.5.3      |                    |                                            |      |

|     |            | 7.5.3.1            | Rx.Detect Substate Machines                |      |

|     |            | 7.5.3.2            | Rx.Detect Requirements                     |      |

|     |            | 7.5.3.3            | Rx.Detect.Reset                            |      |

|     |            | 7.5.3.3.1          | Rx.Detect.Reset Requirements               |      |

|     |            | 7.5.3.3.2          | Exit from Rx.Detect.Reset                  |      |

|     |            | 7.5.3.4            | Rx.Detect.Active                           |      |

|     |            | 7.5.3.5            | Rx.Detect.Active Requirements              |      |

|     |            | 7.5.3.6            | Exit from Rx.Detect.Active                 | 7-41 |

|     |            | 7.5.3.7            | Rx.Detect.Quiet                            |      |

|     |            | 7.5.3.7.1          | Rx.Detect.Quiet Requirements               | 7-42 |

|     |            | 7.5.3.7.2          | Exit from Rx.Detect.Quiet                  | 7-42 |

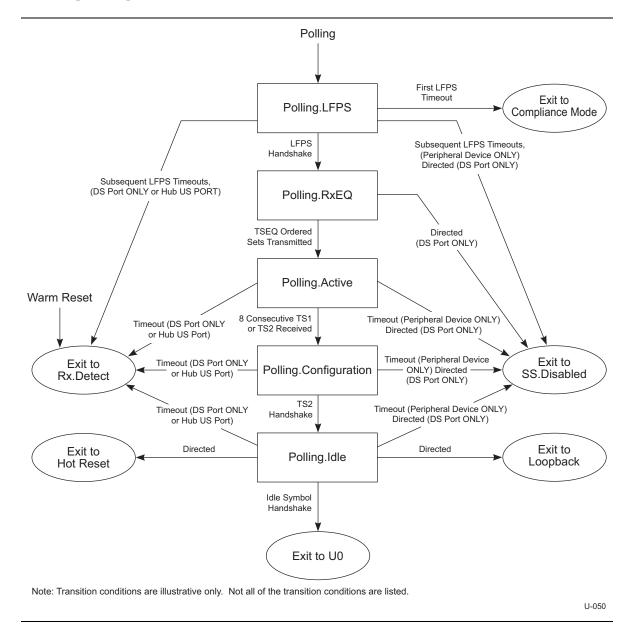

|     | 7.5.4      | Polling            |                                            | 7-43 |

|     |            | 7.5.4.1            | Polling Substate Machines                  | 7-43 |

|     |            | 7.5.4.2            | Polling Requirements                       |      |

|     |            | 7.5.4.3            | Polling.LFPS                               |      |

|     |            |                    | <del>-</del>                               |      |

|        | 7.5.4.3.1  | Polling.LFPS Requirements           | 7-43 |

|--------|------------|-------------------------------------|------|

|        | 7.5.4.3.2  | Exit from Polling.LFPS              |      |

|        | 7.5.4.4    | Polling.RxEQ                        |      |

|        | 7.5.4.4.1  | Polling.RxEQ Requirements           |      |

|        | 7.5.4.4.2  | Exit from Polling.RxEQ              |      |

|        | 7.5.4.5    | Polling.Active                      | 7-44 |

|        | 7.5.4.5.1  | Polling.Active Requirements         | 7-45 |

|        | 7.5.4.5.2  | Exit from Polling.Active            |      |

|        | 7.5.4.6    | Polling.Configuration               |      |

|        | 7.5.4.6.1  | Polling.Configuration Requirements  |      |

|        | 7.5.4.6.2  | Exit from Polling.Configuration     |      |

|        | 7.5.4.7    | Polling.Idle                        |      |

|        | 7.5.4.7.1  | Polling.Idle Requirements           |      |

|        | 7.5.4.7.2  |                                     |      |

| 7.5.5  |            | lode                                |      |

|        | 7.5.5.1    | Compliance Mode Requirements        |      |

|        | 7.5.5.2    | Exit from Compliance Mode           |      |

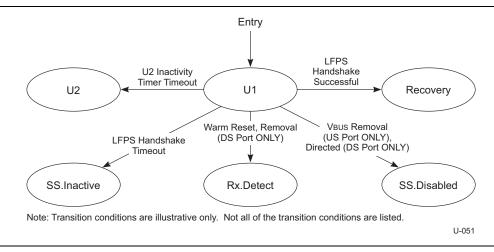

| 7.5.6  |            |                                     |      |

|        | 7.5.6.1    | U0 Requirements                     |      |

|        | 7.5.6.2    | Exit from U0                        |      |

| 7.5.7  |            |                                     |      |

|        |            | U1 Requirements                     |      |

|        |            | Exit from U1                        |      |

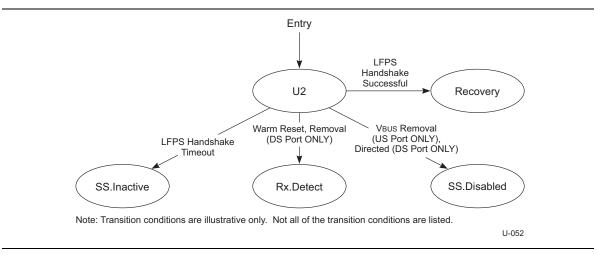

| 7.5.8  |            |                                     |      |

|        |            | U2 Requirements                     |      |

|        |            | Exit from U2                        |      |

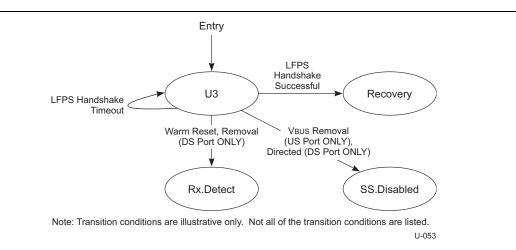

| 7.5.9  |            |                                     |      |

|        | 7.5.9.1    | U3 Requirements                     | 7-51 |

|        | 7.5.9.2    | Exit from U3                        | 7-52 |

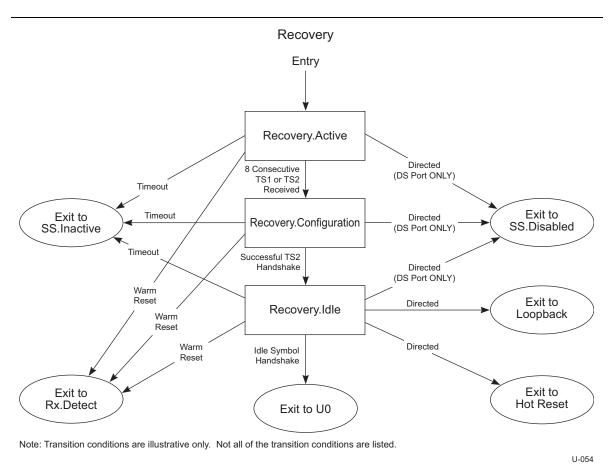

| 7.5.10 | Recovery   |                                     | 7-52 |

|        | 7.5.10.1   | Recovery Substate Machines          | 7-53 |

|        | 7.5.10.2   | Recovery Requirements               |      |

|        | 7.5.10.3   | Recovery.Active                     |      |

|        | 7.5.10.3.1 | Recovery.Active Requirements        | 7-53 |

|        | 7.5.10.3.2 | Exit from Recovery.Active           | 7-53 |

|        | 7.5.10.4   | Recovery.Configuration              | 7-53 |

|        | 7.5.10.4.1 | Recovery.Configuration Requirements | 7-54 |

|        | 7.5.10.4.2 | Exit from Recovery.Configuration    | 7-54 |

|        | 7.5.10.5   | Recovery.ldle                       | 7-54 |

|        | 7.5.10.5.1 | Recovery.Idle Requirements          | 7-54 |

|        | 7.5.10.5.2 | Exit from Recovery.Idle             | 7-55 |

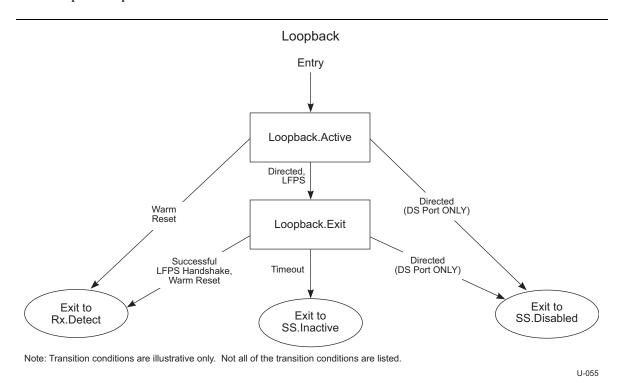

| 7.5.11 | Loopback   |                                     | 7-56 |

|        | 7.5.11.1   | Loopback Substate Machines          | 7-56 |

|        | 7.5.11.2   | Loopback Requirements               | 7-56 |

|        | 7.5.11.3   | Loopback.Active                     | 7-56 |

|        | 7.5.11.3.1 | Loopback.Active Requirements        | 7-56 |

|        | 7.5.11.3.2 |                                     |      |

|        | 7.5.11.4   | Loopback.Exit                       |      |

|        | 7.5.11.4.1 | Loopback Exit Requirements          | 7-57 |

|   |       |           | 7.5.11.4.2           | Exit from Loopback.Exit                      | 7-57 |

|---|-------|-----------|----------------------|----------------------------------------------|------|

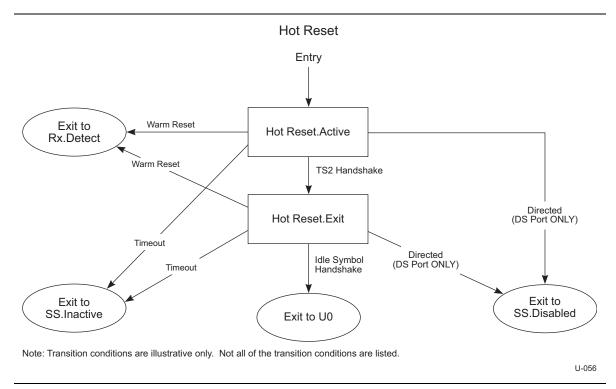

|   |       | 7.5.12    | Hot Reset            | ·                                            | 7-58 |

|   |       |           | 7.5.12.1             | Hot Reset Substate Machines                  | 7-58 |

|   |       |           | 7.5.12.2             | Hot Reset Requirements                       | 7-58 |

|   |       |           | 7.5.12.3             | Hot Reset.Active                             | 7-58 |

|   |       |           | 7.5.12.3.1           | Hot Reset.Active Requirements                | 7-58 |

|   |       |           | 7.5.12.3.2           | Exit from Hot Reset.Active                   | 7-59 |

|   |       |           | 7.5.12.4             | Hot Reset.Exit                               | 7-59 |

|   |       |           | 7.5.12.4.1           | Hot Reset.Exit Requirements                  | 7-59 |

|   |       |           | 7.5.12.4.2           | Exit from Hot Reset.Exit                     | 7-60 |

| 8 | Proto | ocol Lave | er                   |                                              | 8-1  |

|   | 8.1   | _         |                      | S                                            |      |

|   | 8.2   |           |                      |                                              |      |

|   | 8.3   |           |                      |                                              |      |

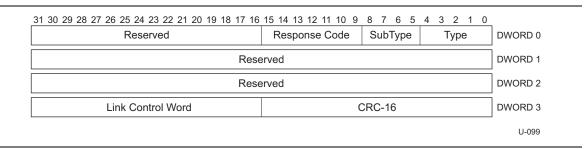

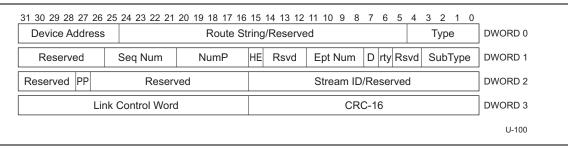

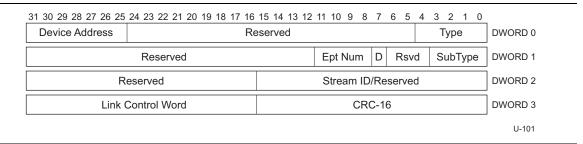

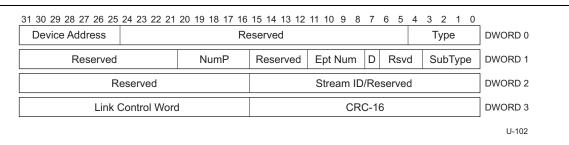

|   | 0.0   | 8.3.1     |                      | n to all Headers                             |      |

|   |       |           | 8.3.1.1              | Reserved Values and Reserved Field Handling  |      |

|   |       |           | 8.3.1.2              | Type Field                                   |      |

|   |       |           | 8.3.1.3              | CRC-16                                       |      |

|   |       |           | 8.3.1.4              | Link Control Word                            |      |

|   | 8.4   | Link Man  | agement Packet       | (LMP)                                        |      |

|   |       | 8.4.1     | Subtype Field.       |                                              | 8-6  |

|   |       | 8.4.2     |                      | ion                                          |      |

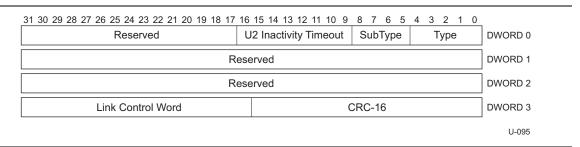

|   |       | 8.4.3     | U2 Inactivity T      | imeout                                       | 8-7  |

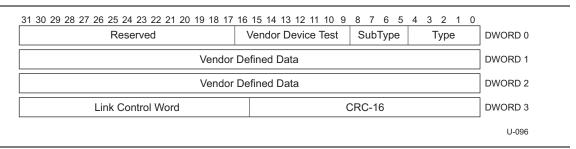

|   |       | 8.4.4     |                      | e Test                                       |      |

|   |       | 8.4.5     |                      | es                                           |      |

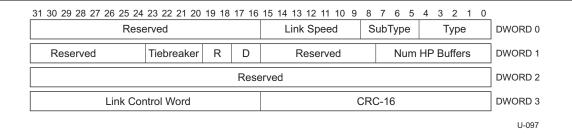

|   |       | 8.4.6     | Port Configura       | tion                                         | 8-10 |

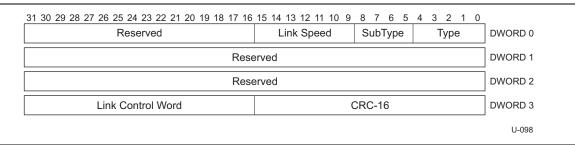

|   |       | 8.4.7     |                      | tion Response                                |      |

|   | 8.5   |           |                      |                                              |      |

|   |       | 8.5.1     |                      | nent (ACK) Transaction Packet                |      |

|   |       | 8.5.2     |                      | RDY) Transaction Packet                      |      |

|   |       | 8.5.3     |                      | dy (ERDY) Transaction Packet                 |      |

|   |       | 8.5.4     |                      | saction Packet                               |      |

|   |       | 8.5.5     |                      | ction Packet                                 |      |

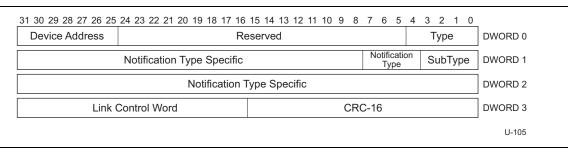

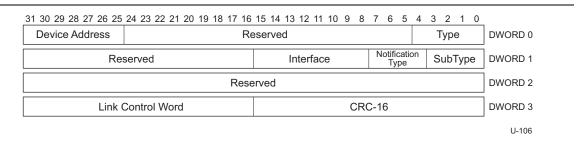

|   |       | 8.5.6     |                      | ation (DEV_NOTIFICATION) Transaction Packet  |      |

|   |       |           |                      | Function Wake Device Notification            | 8-17 |

|   |       |           | 8.5.6.2              | Latency Tolerance Message (LTM) Device       |      |

|   |       |           |                      | Notification                                 | 8-18 |

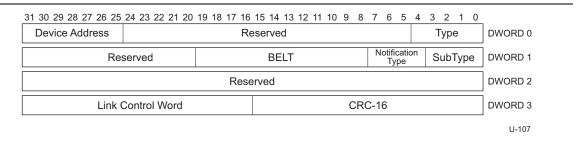

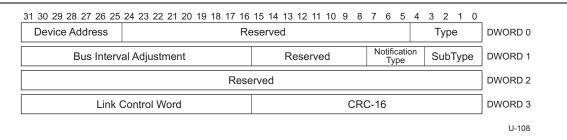

|   |       |           | 8.5.6.3              | Bus Interval Adjustment Message Device       | 0.40 |

|   |       |           | 0.5.0.4              | Notification                                 |      |

|   |       |           | 8.5.6.4              | Function Wake Notification                   |      |

|   |       |           | 8.5.6.5              | Latency Tolerance Messaging                  |      |

|   |       |           | 8.5.6.5.1            | Optional Normative LTM and BELT Requirements |      |

|   |       | 0.5.7     | 8.5.6.6              | Bus Interval Adjustment Message              |      |

|   |       | 8.5.7     |                      | tion Packet                                  |      |

|   | 0.0   | 8.5.8     |                      | NSE Transaction Packet                       |      |

|   | 8.6   |           |                      | De elect (ITD)                               |      |

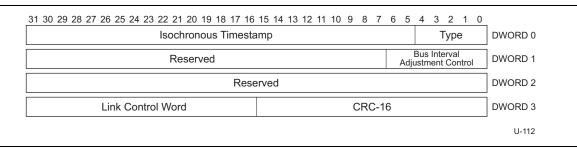

|   | 8.7   |           |                      | Packet (ITP)                                 |      |

|   | 8.8   | Addressii | 10 TIDI <del>C</del> |                                              | Ծ-Z5 |

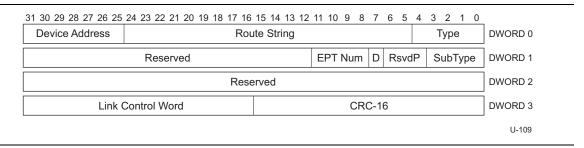

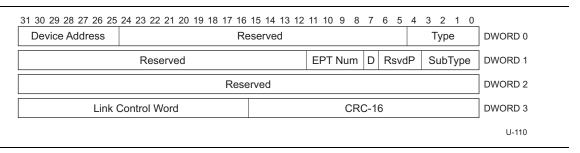

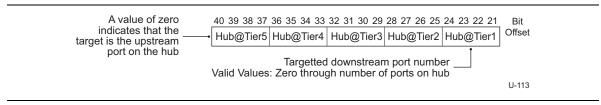

|   | 8.9   | Route Stri  |                      |                                                |      |

|---|-------|-------------|----------------------|------------------------------------------------|------|

|   |       | 8.9.1       | Route String F       | Port Field                                     | 8-26 |

|   |       | 8.9.2       | Route String F       | Port Field Width                               | 8-26 |

|   |       | 8.9.3       | Port Number.         |                                                | 8-26 |

|   | 8.10  | Transaction | n Packet Usag        | es                                             | 8-26 |

|   |       | 8.10.1      | Flow Control C       | Conditions                                     | 8-27 |

|   |       | 8.10.2      | <b>Burst Transac</b> | tions                                          | 8-27 |

|   |       | 8.10.3      |                      |                                                |      |

|   | 8.11  | TP or DP    |                      |                                                |      |

|   |       | 8.11.1      |                      | nse to TP Requesting Data                      |      |

|   |       | 8.11.2      |                      | e to Data Received from a Device               |      |

|   |       | 8.11.3      |                      | nse to Data Received from the Host             |      |

|   |       | 8.11.4      |                      | nse to a SETUP DP                              |      |

|   | 8.12  |             |                      |                                                |      |

|   | 0     | 8.12.1      |                      | ons                                            |      |

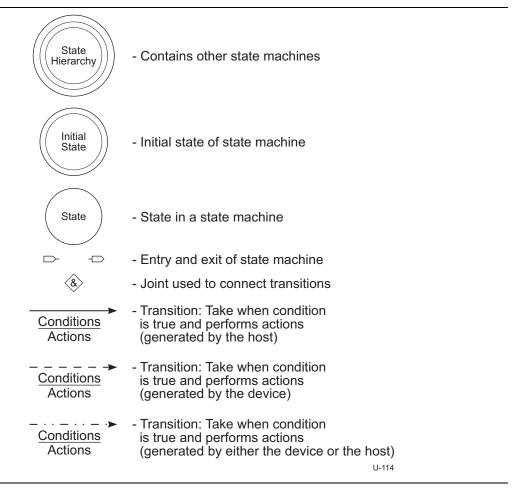

|   |       |             | 8.12.1.1             | State Machine Notation Information             |      |

|   |       |             | 8.12.1.2             | Bulk IN Transactions                           |      |

|   |       |             | 8.12.1.3             | Bulk OUT Transactions                          |      |

|   |       |             | 8.12.1.4             | Bulk Streaming Protocol                        |      |

|   |       |             | 8.12.1.4.1           |                                                |      |

|   |       |             | 8.12.1.4.2           |                                                |      |

|   |       |             | 8.12.1.4.3           |                                                |      |

|   |       | 8.12.2      | -                    | ers                                            |      |

|   |       | 0.12.2      | 8.12.2.1             | Reporting Status Results                       |      |

|   |       |             | 8.12.2.2             | Variable-length Data Stage                     |      |

|   |       |             | 8.12.2.3             | STALL TPs Returned by Control Pipes            |      |

|   |       | 8.12.3      | -                    | nd Service Interval                            |      |

|   |       | 8.12.4      |                      | sactions                                       |      |

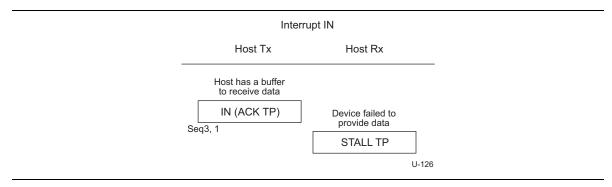

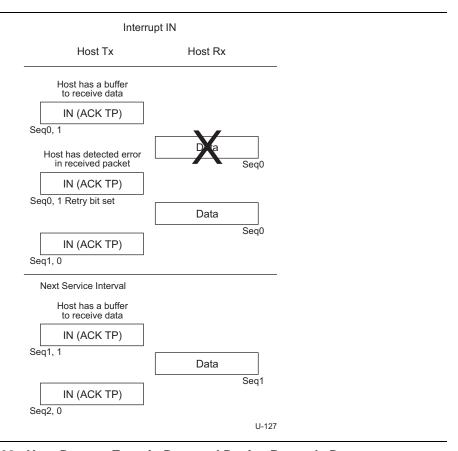

|   |       | 0.12.4      | 8.12.4.1             | Interrupt IN Transactions                      |      |

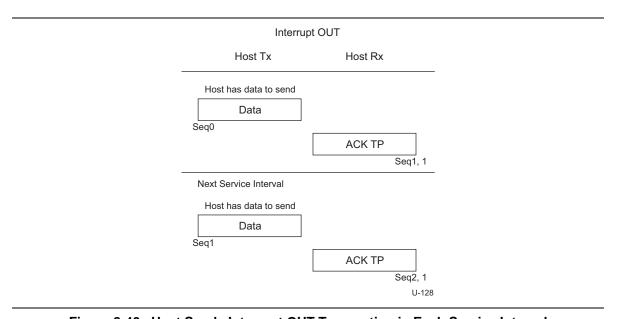

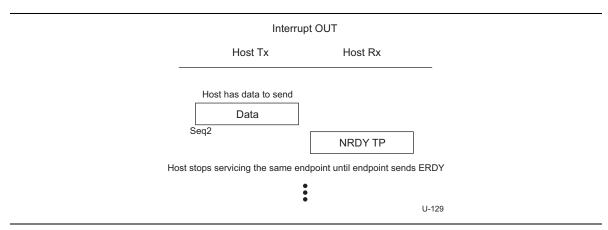

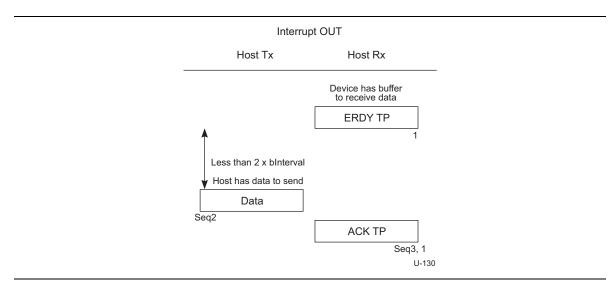

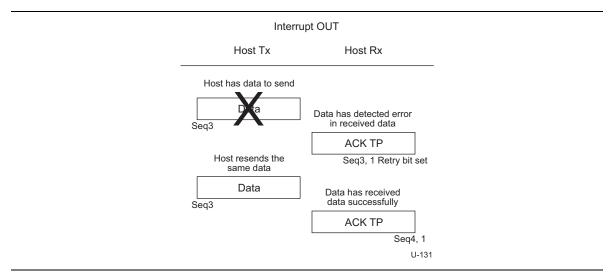

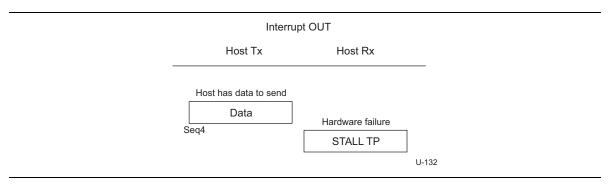

|   |       |             | 8.12.4.2             | Interrupt OUT Transactions                     |      |

|   |       | 8.12.5      |                      | formation                                      |      |

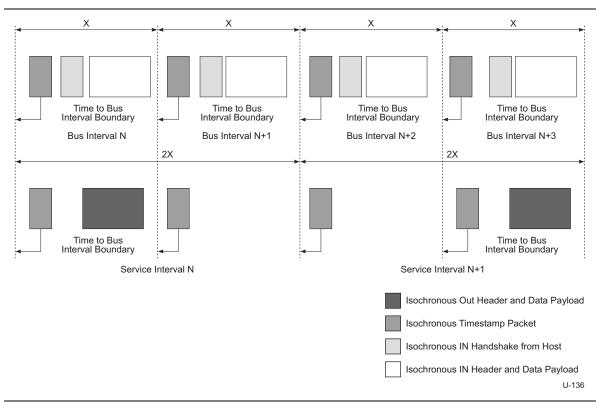

|   |       | 8.12.6      |                      | ransactions                                    |      |

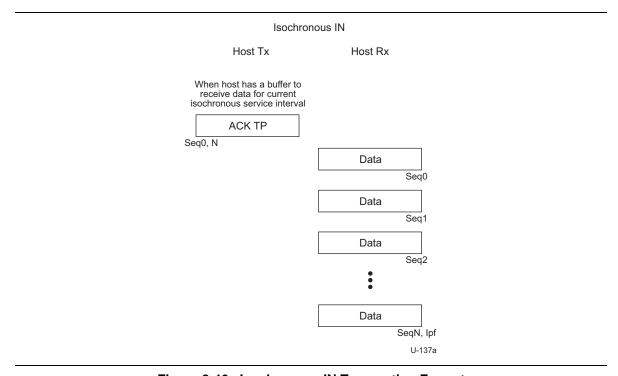

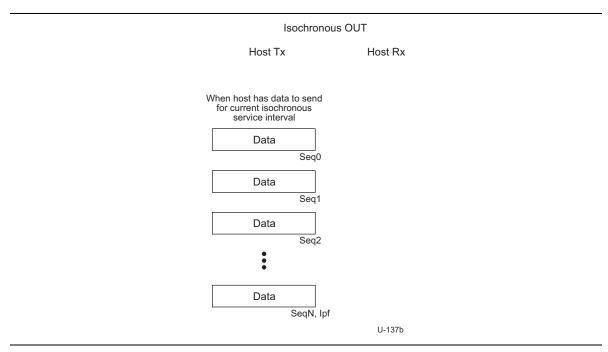

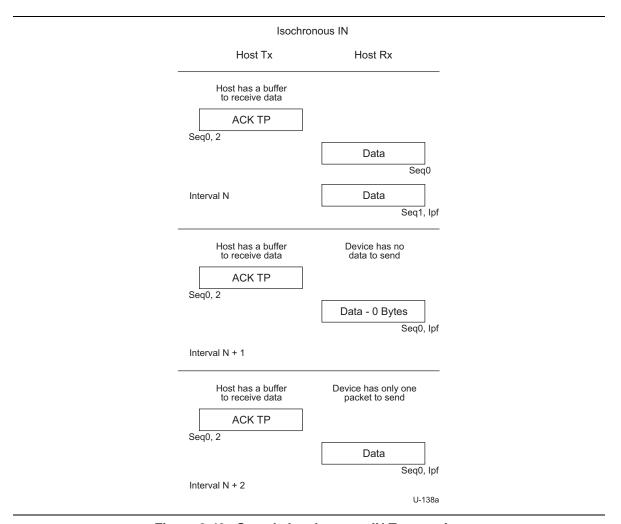

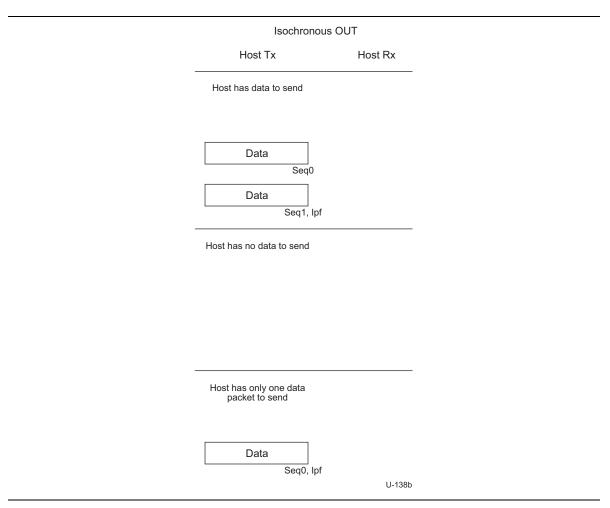

|   |       | 0.12.0      | 8.12.6.1             | Host Flexibility in Performing Isochronous     | 0-00 |

|   |       |             | 0.12.0.1             | Transactions                                   | 8-66 |

|   |       |             | 8.12.6.2             | Device Response to Isochronous IN Transactions |      |

|   |       |             | 8.12.6.3             | Host Processing of Isochronous IN Transactions |      |

|   |       |             | 8.12.6.4             | Device Response to an Isochronous OUT          | 0-00 |

|   |       |             | 0.12.0.4             | Data Packet                                    | 8-67 |

|   | 8.13  | Timing Do   | ramatara             | Data r donet                                   |      |

|   | 0.13  | Tilling Fa  | iameters             |                                                | 0-00 |

| 9 | Devic | e Frame     | work                 |                                                | 9-1  |

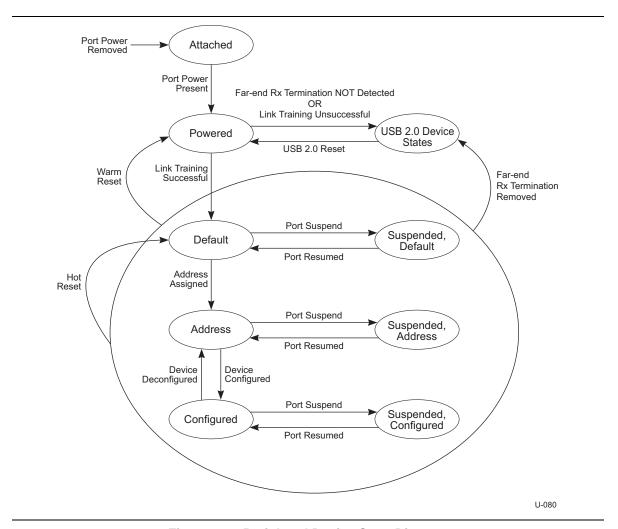

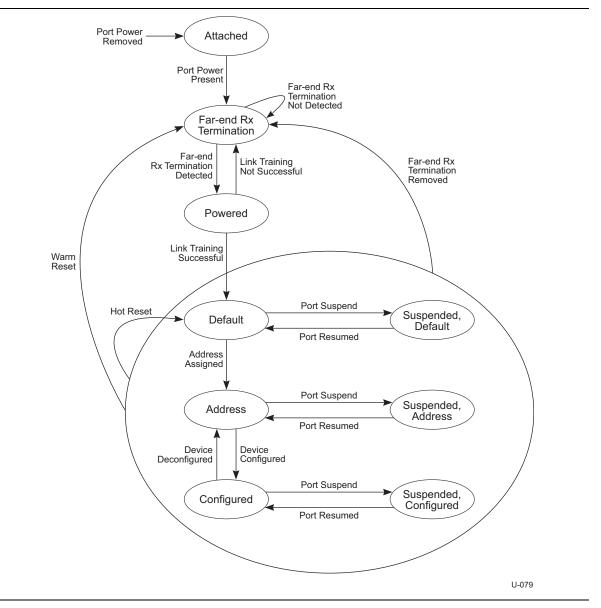

|   | 9.1   | USB Devi    | ce States            |                                                | 9-1  |

|   |       | 9.1.1       |                      | States                                         |      |

|   |       |             | 9.1.1.1              | Attached                                       |      |

|   |       |             | 9.1.1.2              | Powered                                        |      |

|   |       |             | 9.1.1.3              | Default                                        |      |

|   |       |             | 9.1.1.4              | Address                                        |      |

|   |       |             | 9.1.1.5              | Configured                                     |      |

|   |       |             | 9.1.1.6              | Suspended                                      |      |

|   |       |             | ="                   | •                                              |      |

|     | 9.1.2                    | Bus Enumera                    | tion                                   | 9-6  |  |

|-----|--------------------------|--------------------------------|----------------------------------------|------|--|

| 9.2 | Generic                  |                                | ns                                     |      |  |

|     | 9.2.1                    | Dynamic Attachment and Removal |                                        |      |  |

|     | 9.2.2                    | Address Assi                   |                                        |      |  |

|     | 9.2.3                    |                                | ······································ |      |  |

|     | 9.2.4                    | Data Transfer                  |                                        |      |  |

|     | 9.2.5                    |                                | gement                                 |      |  |

|     |                          | 9.2.5.1                        | Power Budgeting                        |      |  |

|     |                          | 9.2.5.2                        | Changing Device Suspend State          |      |  |

|     |                          | 9.2.5.3                        | Function Suspend                       |      |  |

|     |                          | 9.2.5.4                        | Changing Function Suspend State        |      |  |

|     | 9.2.6                    | Request Prod                   | essing                                 |      |  |

|     |                          | 9.2.6.1                        | Request Processing Timing              |      |  |

|     |                          | 9.2.6.2                        | Reset/Resume Recovery Time             |      |  |

|     |                          | 9.2.6.3                        | Set Address Processing                 |      |  |

|     |                          | 9.2.6.4                        | Standard Device Requests               |      |  |

|     |                          | 9.2.6.5                        | Class-specific Requests                |      |  |

|     |                          | 9.2.6.6                        | Speed Dependent Descriptors            |      |  |

|     | 9.2.7                    |                                | r                                      |      |  |

| 9.3 | USB De                   |                                |                                        |      |  |

|     | 9.3.1                    | bmRequestType                  |                                        |      |  |

|     | 9.3.2                    |                                |                                        |      |  |

|     | 9.3.3                    | wValue                         |                                        |      |  |

|     | 9.3.4                    | wIndex                         |                                        |      |  |

|     | 9.3.5                    | wLength                        |                                        |      |  |

| 9.4 | Standard Device Requests |                                |                                        |      |  |

|     | 9.4.1                    | Clear Feature                  | ·                                      | 9-18 |  |

|     | 9.4.2                    |                                | ation                                  |      |  |

|     | 9.4.3                    | Get Descripto                  | r                                      | 9-19 |  |

|     | 9.4.4                    |                                |                                        |      |  |

|     | 9.4.5                    | Get Status                     |                                        | 9-21 |  |

|     | 9.4.6                    | Set Address.                   |                                        | 9-23 |  |

|     | 9.4.7                    | Set Configura                  | ition                                  | 9-24 |  |

|     | 9.4.8                    | Set Descripto                  | r                                      | 9-24 |  |

|     | 9.4.9                    | Set Feature                    |                                        | 9-25 |  |

|     | 9.4.10                   | Set Interface                  |                                        | 9-27 |  |

|     | 9.4.11                   | Set Isochrono                  | ous Delay                              | 9-27 |  |

|     | 9.4.12                   | Set SEL                        |                                        | 9-28 |  |

|     | 9.4.13                   | Synch Frame                    |                                        | 9-29 |  |

| 9.5 |                          |                                |                                        |      |  |

| 9.6 | Standard                 | d USB Descripto                | r Definitions                          | 9-30 |  |

|     | 9.6.1                    |                                |                                        |      |  |

|     | 9.6.2                    | Binary Device                  | e Object Store (BOS)                   | 9-32 |  |

|     |                          | 9.6.2.1                        | USB 2.0 Extension                      | 9-33 |  |

|     |                          | 9.6.2.2                        | SuperSpeed USB Device Capability       | 9-34 |  |

|     |                          | 9.6.2.3                        | Container ID                           |      |  |

|     | 9.6.3                    |                                |                                        |      |  |

|     | 9.6.4                    |                                | ociation                               |      |  |

|     | 9.6.5                    | Interface                      |                                        |      |  |

|    |        | 9.6.6          | Endpoint             |                                              | 9-41  |

|----|--------|----------------|----------------------|----------------------------------------------|-------|

|    |        | 9.6.7          |                      | ndpoint Companion                            |       |

|    |        | 9.6.8          |                      |                                              |       |

|    | 9.7    | Device Cl      |                      |                                              |       |

|    |        | 9.7.1          |                      |                                              |       |

|    |        | 9.7.2          |                      |                                              |       |

|    |        | 9.7.3          | Requests             |                                              | 9-48  |

|    |        |                | •                    |                                              |       |

| 10 |        |                |                      | rt, and Device Upstream                      |       |

|    | Port : | Specifica      | ation                |                                              | 10-1  |

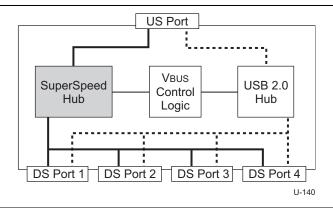

|    | 10.1   | Hub Feat       |                      |                                              |       |

|    |        | 10.1.1         |                      | apable Host with SuperSpeed Capable Software |       |

|    |        | 10.1.2         | USB 2.0 Host         |                                              | 10-4  |

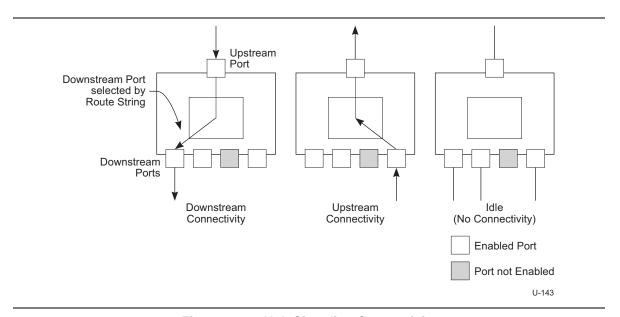

|    |        | 10.1.3         | <b>Hub Connectiv</b> | ity                                          | 10-5  |

|    |        |                | 10.1.3.1             | Packet Signaling Connectivity                | 10-5  |

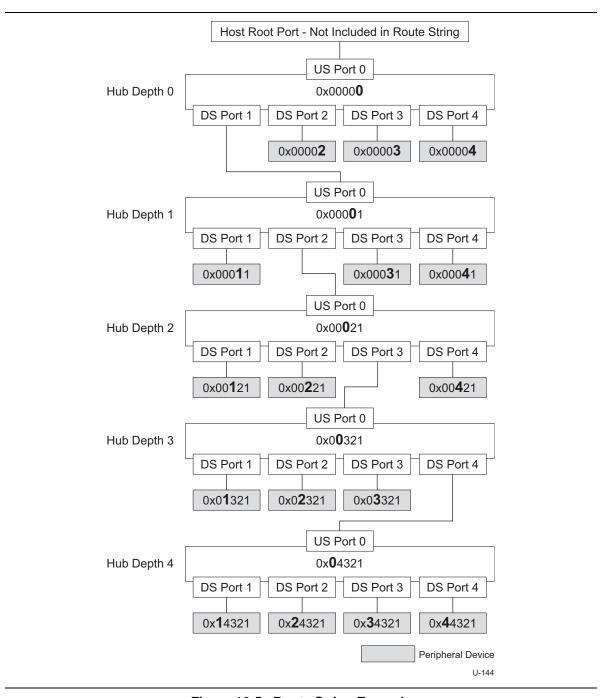

|    |        |                | 10.1.3.2             | Routing Information                          | 10-6  |

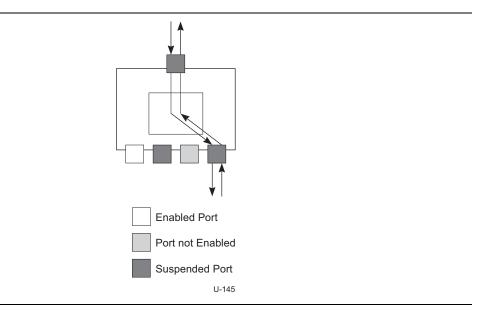

|    |        | 10.1.4         | Resume Conne         | ectivity                                     | 10-8  |

|    |        | 10.1.5         | Hub Fault Reco       | overy Mechanisms                             | 10-8  |

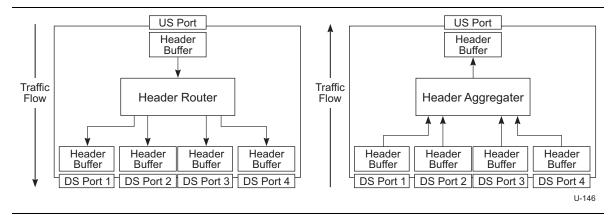

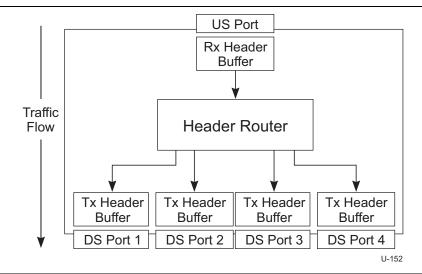

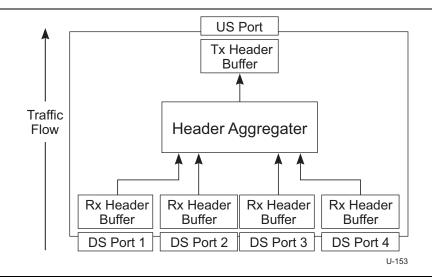

|    |        | 10.1.6         | Hub Header Pa        | acket Buffer Architecture                    | 10-9  |

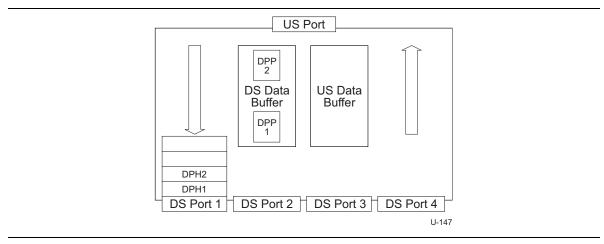

|    |        |                | 10.1.6.1             | Hub Data Buffer Architecture                 | 10-9  |

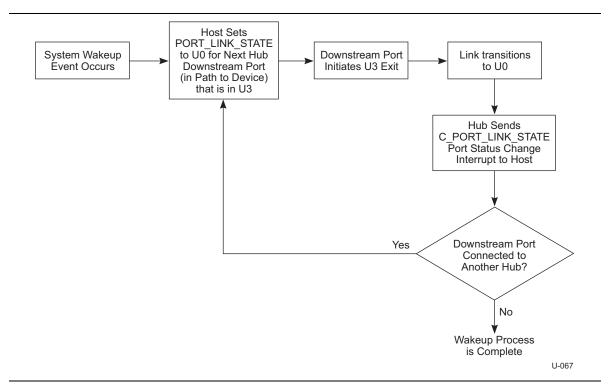

|    | 10.2   | Hub Pow        | er Management        |                                              | 10-10 |

|    |        | 10.2.1         | Link States          |                                              | 10-10 |

|    |        | 10.2.2         |                      | am Port U1/U2 Timers                         |       |

|    |        | 10.2.3         | Downstream/U         | pstream Port Link State Transitions          | 10-11 |

|    | 10.3   | <b>Hub Dow</b> |                      | Ports                                        |       |

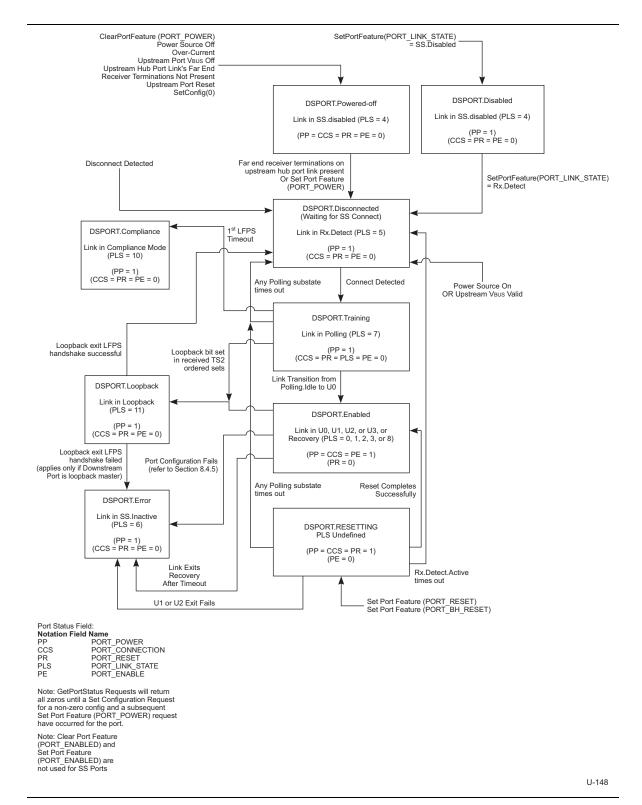

|    |        | 10.3.1         | Hub Downstrea        | am Facing Port State Descriptions            | 10-13 |

|    |        |                | 10.3.1.1             | DSPORT.Powered-off                           | 10-13 |

|    |        |                | 10.3.1.2             | DSPORT.Disconnected (Waiting for SS Connect) | 10-14 |

|    |        |                |                      | DSPORT.Training                              |       |

|    |        |                | 10.3.1.4             | DSPORT.ERROR                                 | 10-15 |

|    |        |                | 10.3.1.5             | DSPORT.Enabled                               | 10-15 |

|    |        |                | 10.3.1.6             | DSPORT.Resetting                             | 10-15 |

|    |        |                | 10.3.1.7             | DSPORT.Compliance                            | 10-16 |

|    |        |                | 10.3.1.8             | DSPORT.Loopback                              | 10-16 |

|    |        |                |                      | DSPORT.Disabled                              |       |

|    |        | 10.3.2         | Disconnect De        | tect Mechanism                               | 10-16 |

|    |        | 10.3.3         | Labeling             |                                              | 10-16 |

|    | 10.4   | <b>Hub Dow</b> | nstream Facing I     | Port Power Management                        | 10-16 |

|    |        | 10.4.1         |                      | acing Port PM Timers                         |       |

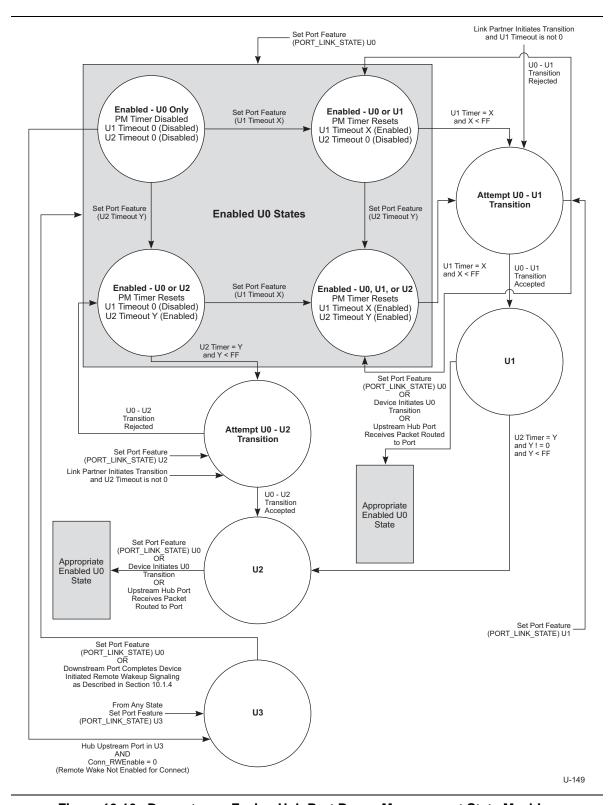

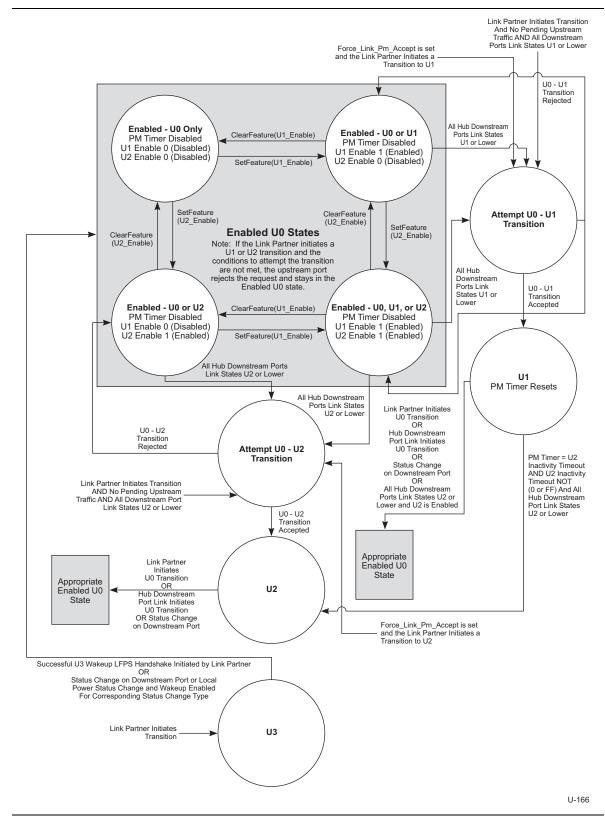

|    |        | 10.4.2         | Hub Downstrea        | am Facing Port State Descriptions            | 10-19 |

|    |        |                |                      | Enabled U0 States                            |       |

|    |        |                | 10.4.2.2             | Attempt U0 – U1 Transition                   | 10-20 |

|    |        |                |                      | Attempt U0 – U2 Transition                   |       |

|    |        |                |                      | Link in U1                                   |       |

|    |        |                | 10.4.2.5             | Link in U2                                   | 10-21 |

|    |        |                | 10.4.2.6             | Link in U3                                   | 10-21 |

|    | 10.5   | Hub Upst       |                      | t                                            |       |

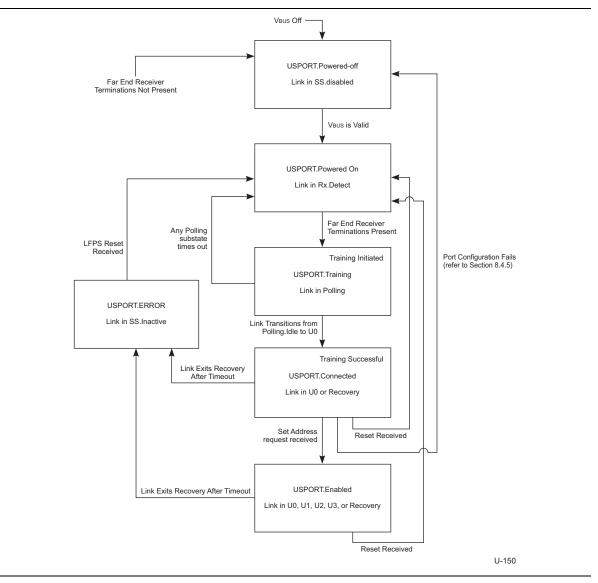

|    |        | 10.5.1         | Upstream Faci        | ng Port State Descriptions                   |       |

|    |        |                | 10.5.1.1             | USPORT.Powered-off                           | 10-23 |

|      |          | 10.5.1.2       | USPORT.Powered-on                 | 10-24 |

|------|----------|----------------|-----------------------------------|-------|

|      |          | 10.5.1.2       | USPORT.Training                   |       |

|      |          | 10.5.1.4       | •                                 |       |

|      |          |                | USPORT.Connected                  |       |

|      |          | 10.5.1.5       | USPORT.Error                      |       |

|      |          | 10.5.1.6       | USPORT.Enabled                    |       |

|      | 10.5.2   |                | State Machine                     |       |

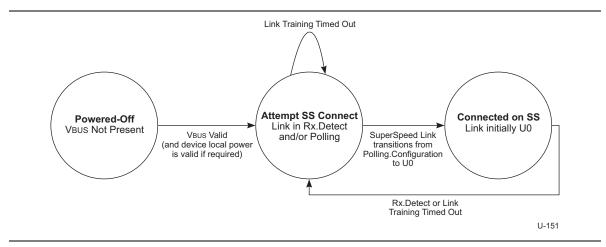

|      |          | 10.5.2.1       | Hub Connect State Descriptions    |       |

|      |          | 10.5.2.2       | HCONNECT.Powered-off              |       |

|      |          | 10.5.2.3       | HCONNECT.Attempt SS Connect       | 10-25 |

|      |          | 10.5.2.4       | HCONNECT.Connected on SS          | 10-25 |

| 10.6 | Upstream | Facing Port Po | wer Management                    | 10-26 |

|      | 10.6.1   | Upstream Fac   | ing Port PM Timer                 | 10-28 |

|      | 10.6.2   | Hub Upstream   | Facing Port State Descriptions    | 10-28 |

|      |          | 10.6.2.1       | Enabled U0 States                 | 10-28 |

|      |          | 10.6.2.2       | Attempt U0 – U1 Transition        |       |

|      |          | 10.6.2.3       | Attempt U0 – U2 Transition        |       |

|      |          | 10.6.2.4       | Link in U1                        |       |

|      |          | 10.6.2.5       | Link in U2                        |       |

|      |          | 10.6.2.6       | Link in U3                        |       |

| 10.7 | Hub Hood |                | rarding and Data Repeater         |       |

| 10.7 | 10.7.1   |                | Buffer                            |       |

|      | 10.7.1   | •              |                                   |       |

|      |          |                | Sets                              |       |

|      | 10.7.3   |                | pacing                            |       |

|      | 10.7.4   |                | et Buffer Architecture            |       |

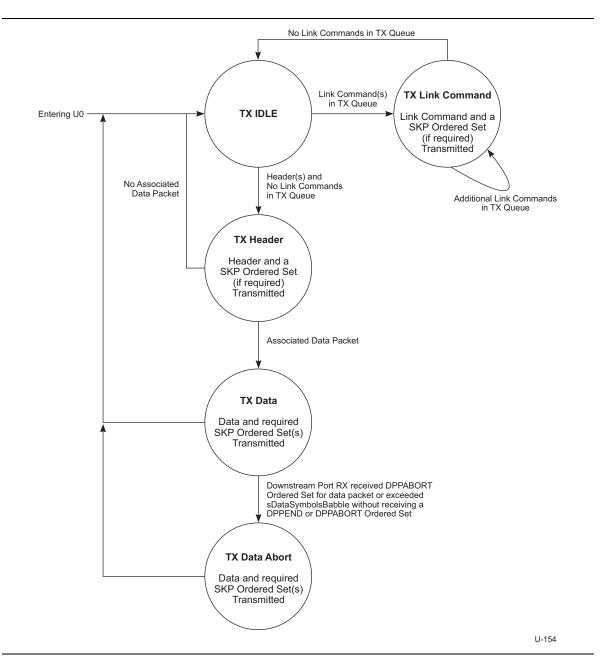

|      | 10.7.5   |                | ing Port Tx                       |       |

|      | 10.7.6   | •              | ing Port Tx State Descriptions    |       |

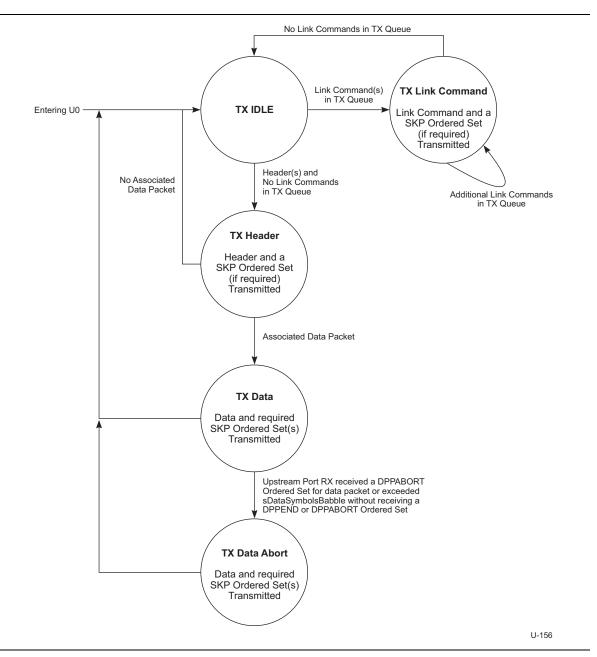

|      |          | 10.7.6.1       | Tx IDLE                           |       |

|      |          | 10.7.6.2       | Tx Header                         |       |

|      |          | 10.7.6.3       | Tx Data                           |       |

|      |          | 10.7.6.4       | Tx Data Abort                     |       |

|      |          | 10.7.6.5       | Tx Link Command                   | 10-36 |

|      | 10.7.7   |                | sing Port Rx                      |       |

|      | 10.7.8   | Upstream Fac   | ing Port Rx State Descriptions    | 10-37 |

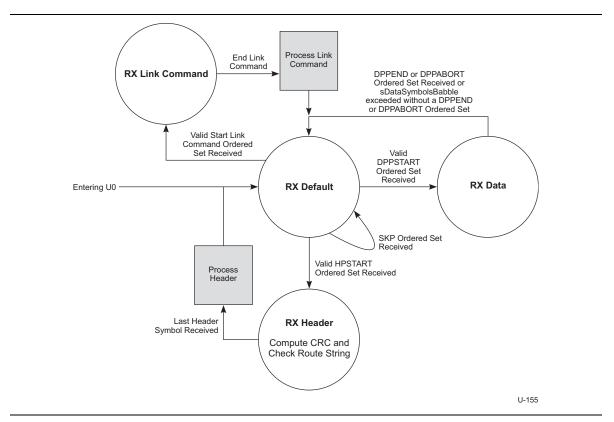

|      |          | 10.7.8.1       | Rx Default                        | 10-37 |

|      |          | 10.7.8.2       | Rx Data                           | 10-38 |

|      |          | 10.7.8.3       | Rx Header                         | 10-38 |

|      |          | 10.7.8.4       | Process Header Packet             | 10-38 |

|      |          | 10.7.8.5       | Rx Link Command                   |       |

|      |          | 10.7.8.6       | Process Link Command              |       |

|      | 10.7.9   |                | Facing Port Tx                    |       |

|      | 10.7.10  |                | Facing Port Tx State Descriptions |       |

|      |          | 10.7.10.1      | Tx IDLE                           |       |

|      |          | 10.7.10.2      | Tx Header                         |       |

|      |          | 10.7.10.2      | Tx Data                           |       |

|      |          | 10.7.10.3      | Tx Data Abort                     |       |

|      |          |                |                                   |       |

|      | 10 7 11  | 10.7.10.5      | Tx Link Command                   |       |

|      | 10.7.11  |                | Facing Port Rx                    |       |

|      | 10.7.12  |                | Facing Port Rx State Descriptions |       |

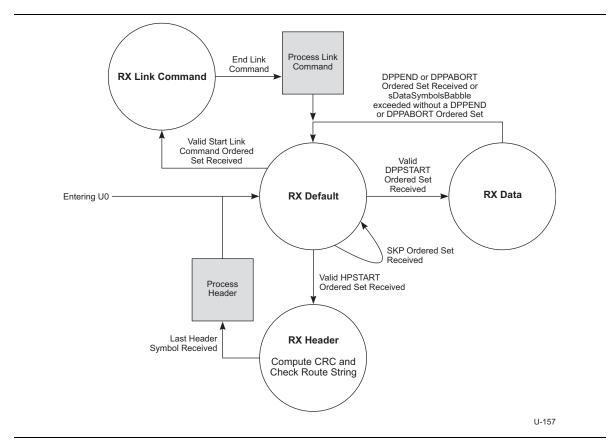

|      |          | 10.7.12.1      | Rx Default                        | 10-45 |

|       |            | 10.7.12.2      | Rx Data                                | 10-45 | , |

|-------|------------|----------------|----------------------------------------|-------|---|

|       |            | 10.7.12.3      | Rx Header                              | 10-45 | ) |

|       |            | 10.7.12.4      | Process Header                         | 10-46 | j |

|       |            | 10.7.12.5      | Rx Link Command                        | 10-46 | j |

|       |            | 10.7.12.6      | Process Link Command                   | 10-47 |   |

|       | 10.7.13    | SuperSpeed     | Packet Connectivity                    |       |   |

| 10.8  | Suspend a  |                | ······································ |       |   |

| 10.9  |            |                | et Behavior                            |       |   |

| 10.10 | •          |                |                                        |       |   |

|       | 10.10.1    |                | gs                                     |       |   |

| 10.11 | Hub Contr  |                | ·······                                |       |   |

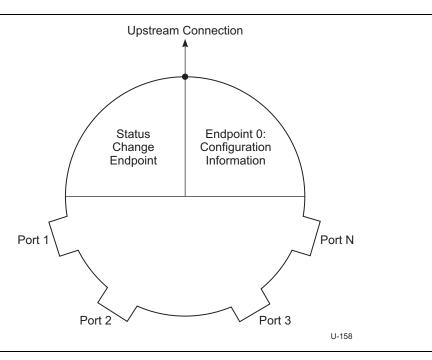

|       | 10.11.1    |                | anization                              |       |   |

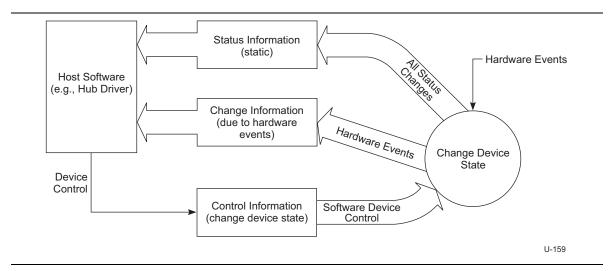

|       | 10.11.2    | Hub Informat   | ion Architecture and Operation         | 10-50 | J |

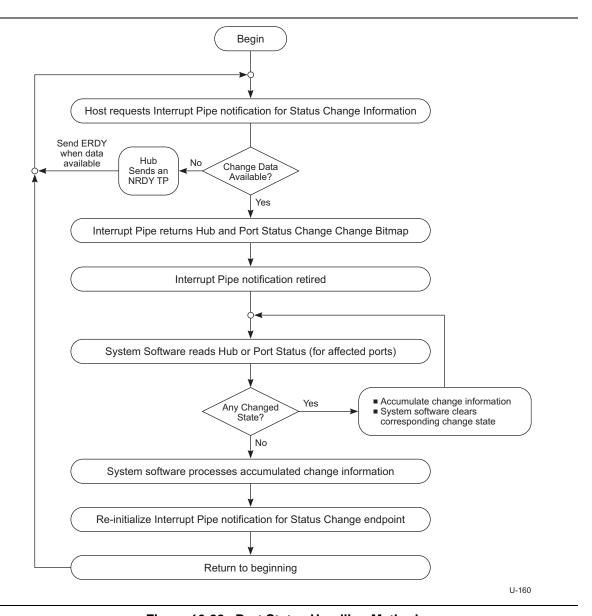

|       | 10.11.3    |                | Information Processing                 |       |   |

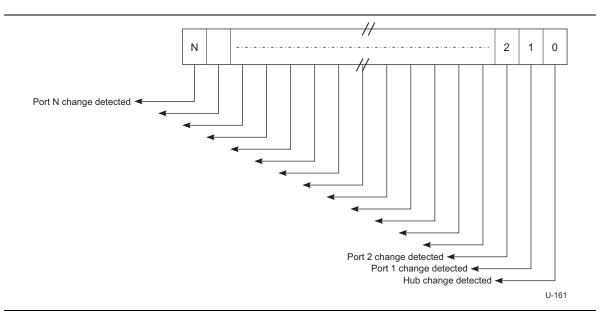

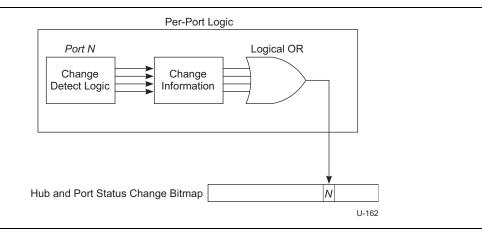

|       | 10.11.4    |                | : Status Change Bitmap                 |       |   |

|       | 10.11.5    |                | Reporting and Recovery                 |       |   |

|       | 10.11.6    |                | Handling                               |       |   |

| 10.12 | Hub Confi  | guration       |                                        | 10-54 |   |

| 10.13 | Descriptor | S              |                                        | 10-56 | į |

|       | 10.13.1    | Standard Des   | scriptors for Hub Class                | 10-56 | i |

|       | 10.13.2    | Class-specific | c Descriptors                          | 10-59 | Ì |

|       |            | 10.13.2.1      | Hub Descriptor                         | 10-59 | ĺ |

| 10.14 | Requests.  |                |                                        | 10-61 |   |

|       | 10.14.1    | Standard Red   | quests                                 | 10-61 |   |

|       | 10.14.2    | Class-specific | c Requests                             | 10-62 |   |

|       |            | 10.14.2.1      | Clear Hub Feature                      | 10-64 |   |

|       |            | 10.14.2.2      | Clear Port Feature                     |       |   |

|       |            | 10.14.2.3      | Get Hub Descriptor                     |       |   |

|       |            | 10.14.2.4      | Get Hub Status                         |       |   |

|       |            | 10.14.2.5      | Get Port Error Count                   |       |   |

|       |            | 10.14.2.6      | Get Port Status                        |       |   |

|       |            | 10.14.2.6      |                                        |       |   |

|       |            |                | RT_CONNECTION                          |       |   |

|       |            |                | RT_ENABLE                              |       |   |

|       |            |                | RT_OVER_CURRENT                        |       |   |

|       |            |                | RT_RESET                               |       |   |

|       |            |                | RT_LINK_STATE                          |       |   |

|       |            |                | RT_POWER                               |       |   |

|       |            |                | RT_SPEED                               |       |   |

|       |            | 10.14.2.6      |                                        |       |   |

|       |            |                | PORT_CONNECTION                        |       |   |

|       |            | _              | PORT_OVER_CURRENT                      |       |   |

|       |            |                | PORT_RESET                             |       |   |

|       |            | _              | PORT_BH_RESET                          |       |   |

|       |            |                | PORT_LINK_STATE                        |       |   |

|       |            |                | PORT_CONFIG_ERROR                      |       |   |

|       |            | 10.14.2.7      | Set Hub Descriptor                     |       |   |

|       |            | 10.14.2.8      | Set Hub Feature                        |       |   |

|       |            | 10.14.2.9      | Set Hub Depth                          | 10-73 | į |

|    |        |            | 10.14.2.10     | Set Port Feature                       | 10-74 |

|----|--------|------------|----------------|----------------------------------------|-------|

|    | 10.15  | Host Root  | (Downstream)   | Ports                                  | 10-77 |

|    | 10.16  |            |                | eam Ports                              |       |

|    |        | 10.16.1    |                | vice Upstream Ports                    |       |

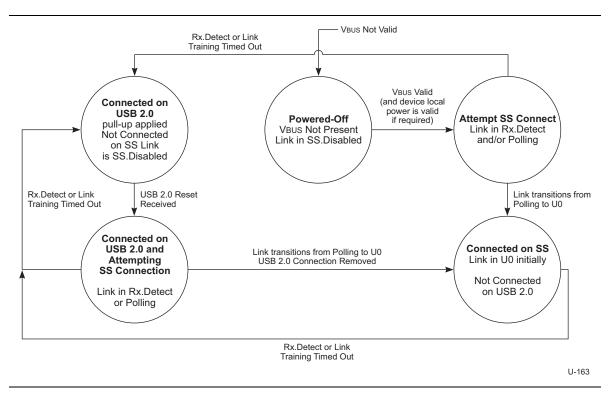

|    |        | 10.16.2    |                | vice Connect State Machine             |       |

|    |        |            | 10.16.2.1      | PCONNECT.Powered-off                   |       |

|    |        |            | 10.16.2.2      | PCONNECT.Attempt SS Connect            |       |

|    |        |            | 10.16.2.3      | PCONNECT.Connected on SS               |       |

|    |        |            | 10.16.2.4      | PCONNECT.Connected on USB 2.0          | 10-80 |

|    |        |            | 10.16.2.5      | PCONNECT.Connected on USB 2.0 and      |       |

|    |        |            |                | Attempting SS Connection               | 10-80 |

|    | 10.17  | Hub Chap   | ter Parameters | S                                      | 10-81 |

| 11 | Interd | pperabilit | tv and Powe    | er Delivery                            | 11-1  |

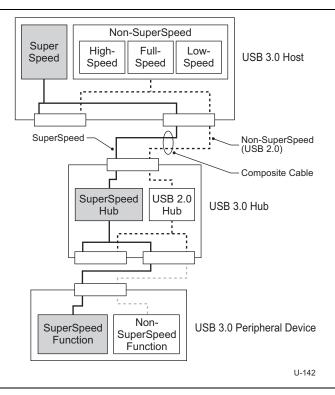

|    | 11.1   |            |                | r USB 2.0                              |       |

|    | 11.2   |            |                | USB 2.0                                |       |

|    | 11.3   |            |                | for USB 2.0                            |       |

|    | 11.4   |            |                | 101 005 2.0                            |       |

|    |        | 11.4.1     |                | evices and Connections                 |       |

|    |        |            | 11.4.1.1       | Self-powered Hubs                      |       |

|    |        |            | 11.4.1.1.1     |                                        |       |

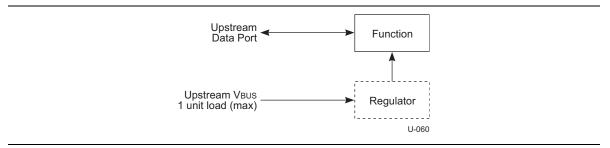

|    |        |            | 11.4.1.2       | Low-power Bus-powered Devices          |       |

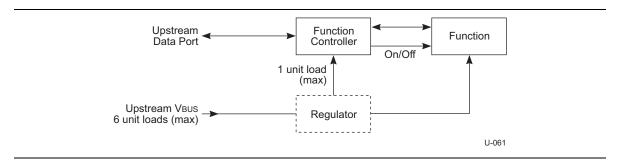

|    |        |            | 11.4.1.3       | High-power Bus-powered Devices         |       |

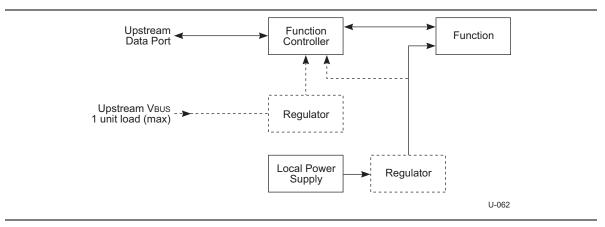

|    |        |            | 11.4.1.4       | Self-powered Devices                   |       |

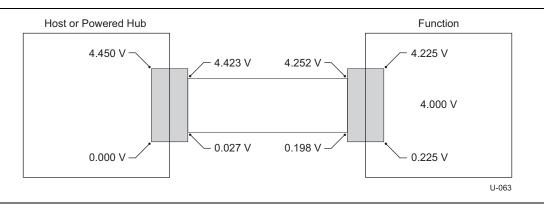

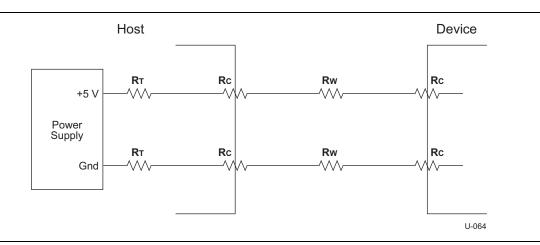

|    |        | 11.4.2     | Steady-State   | Voltage Drop Budget                    |       |

|    |        | 11.4.3     |                | I During Suspend/Resume                |       |

|    |        | 11.4.4     |                | ch and Detach                          |       |

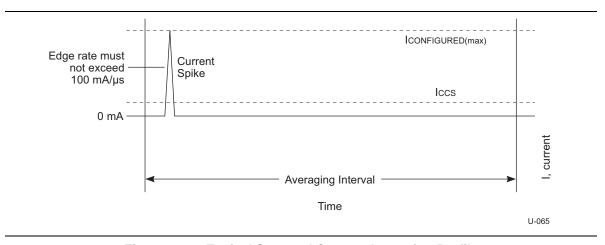

|    |        |            | 11.4.4.1       | Inrush Current Limiting                | 11-9  |

|    |        |            | 11.4.4.2       | Dynamic Detach                         | 11-10 |

|    |        | 11.4.5     |                | al Characteristics                     | 11-10 |

|    |        | 11.4.6     | Powered-B C    | onnector                               | 11-10 |

|    |        | 11.4.7     | Wire Gauge T   | able                                   | 11-11 |

| Α  | Svmb   | ool Enco   | dina           |                                        | A-1   |

|    | _      |            |                |                                        |       |

| В  |        |            |                |                                        |       |

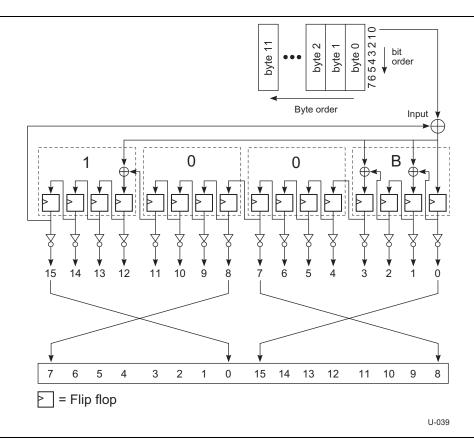

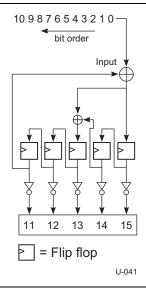

|    | B.1    | Data Scra  | mbling         |                                        | B-1   |

| C  | Powe   | er Manag   | ement          |                                        | C-1   |

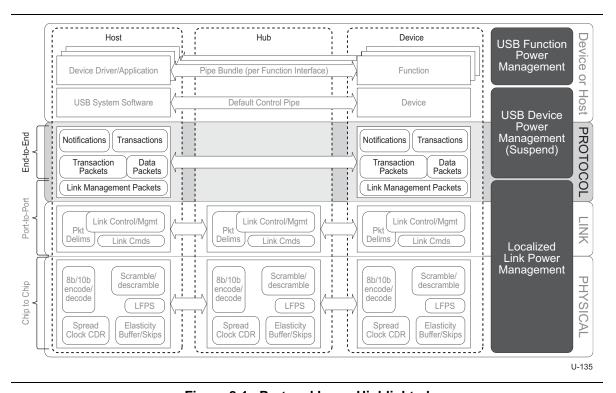

|    | C.1    | SuperSpe   | ed Power Man   | agement Overview                       | C-1   |

|    |        | C.1.1      |                | anagement                              |       |

|    |        |            | C.1.1.1        | Summary of Link States                 |       |

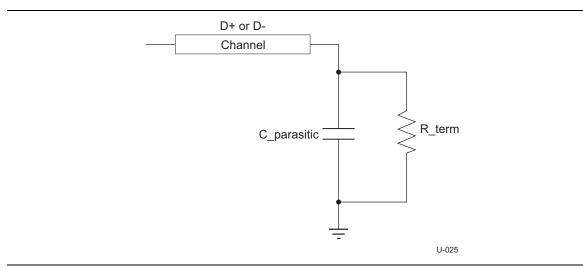

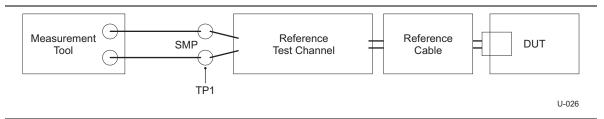

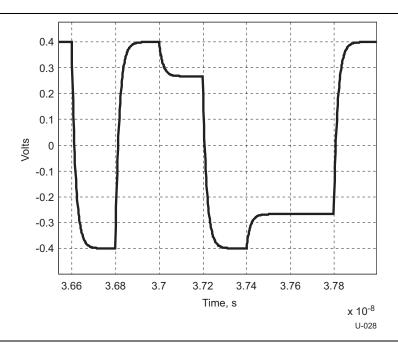

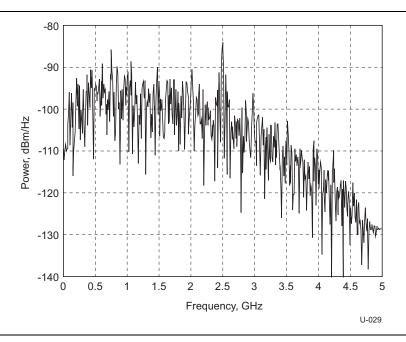

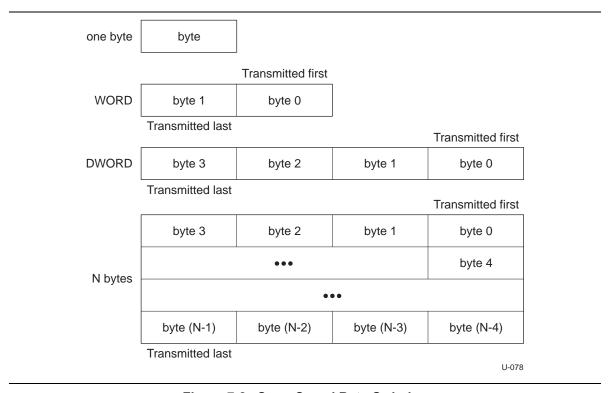

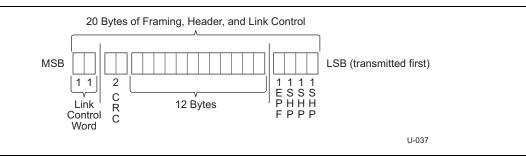

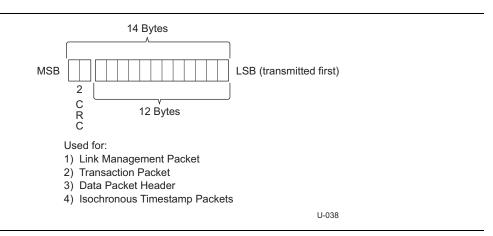

|    |        |            | C.1.1.2        | U0 – Link Active                       |       |